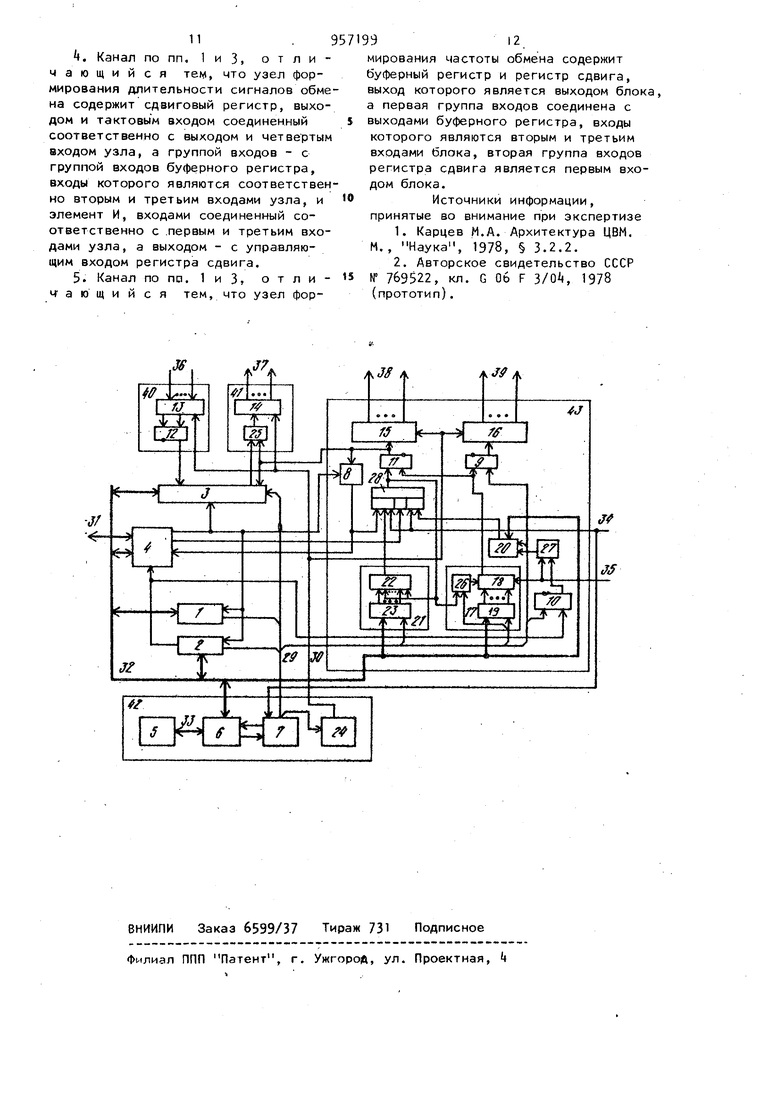

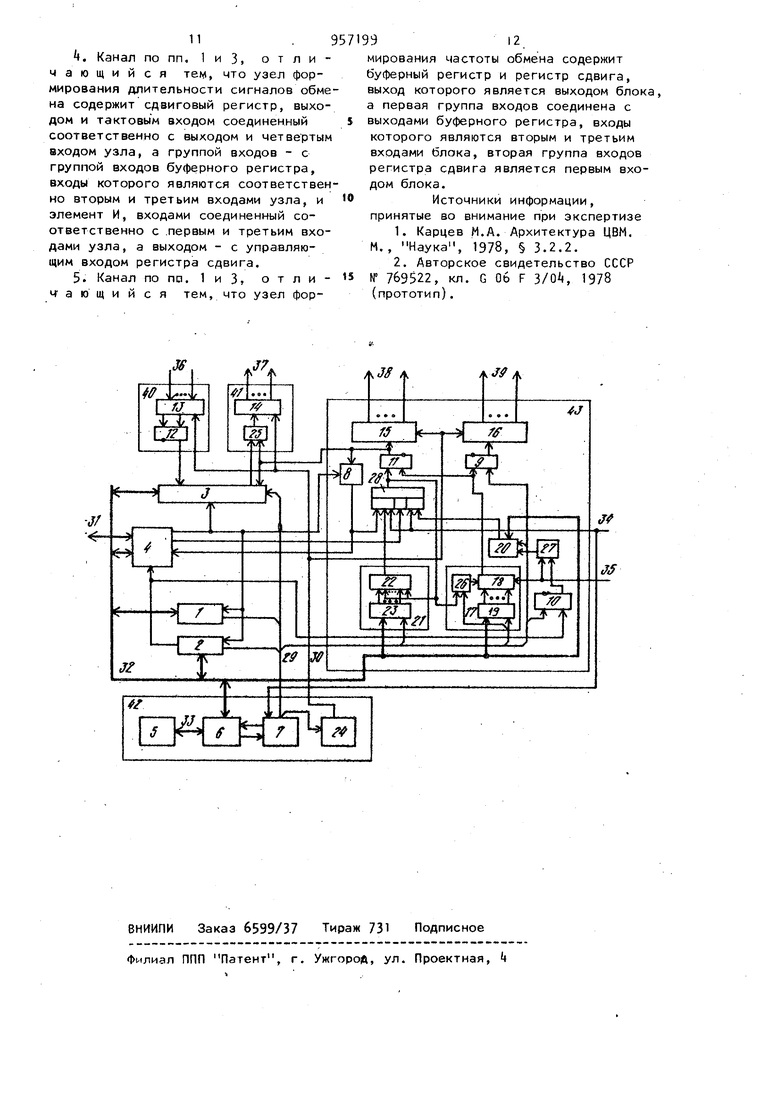

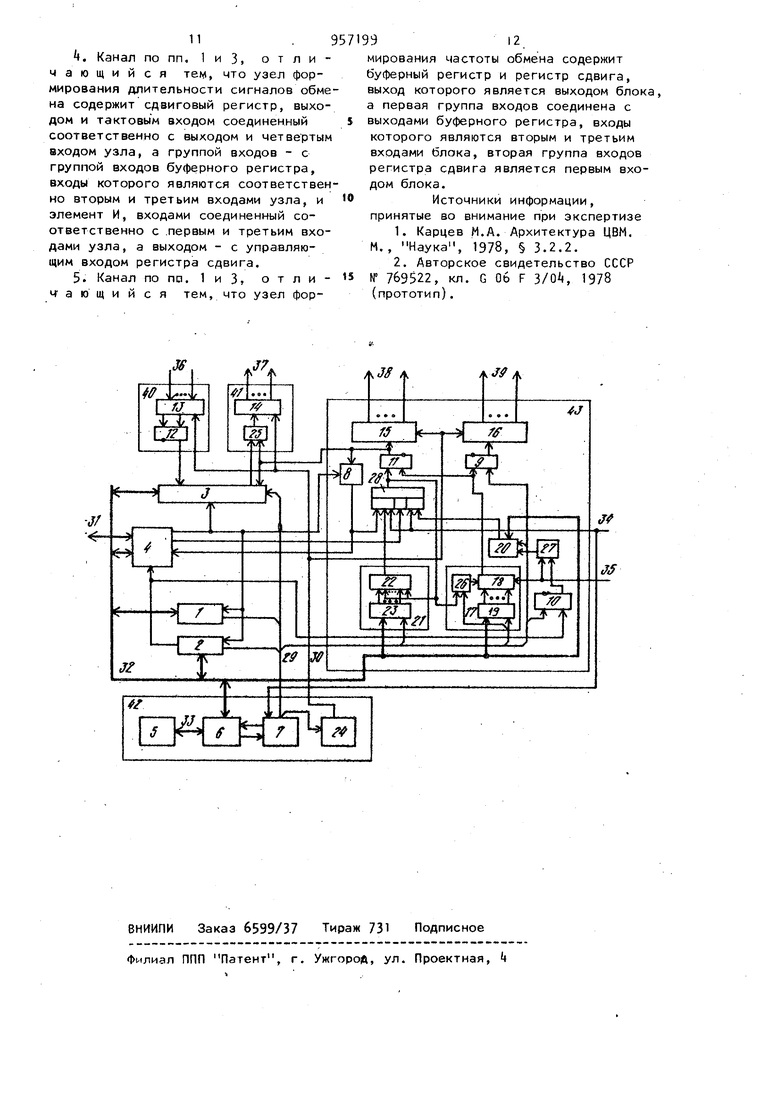

Изобретение относится к вычислительной технике и предназначено для использования а вычислительных сист мах а/, разветапенной сетью периферий ных устройств. Известны мультиплексные каналы , содержащие устройство управ.ления, узлы связи (стыковки) с oneративной памятью (ОЗУ) и процессором, регистр связи с интерфейсом (регистр-преобразователь), регистры управляющего слова, текущего адреса данных, текущего счетчика данных память подканалов, регистр кода операций и указателей. Все перечисленные узлы и регистры соединены с общими магистралями. Обмен информацией в этих устройствах между периферийными устройствами и памятью процессорапроизводится путем настройки,т.е. выдачи начальных адресов, объема массива, режимов обмена Г. Недостаток этих каналов состоит d ограниченной области применения, вследствие невозможности обслуживания одним каналов внешних устройс-гв, имеющих разные временные диаграммы обмена, разные длительности сигналов обмена. В результате для каждой группы абонентов имеющих одинаковую диаграмму обмена, длительность сигналов обмена, необходимо иметь свой мультиплексный канал, что значительно усложняет системы ввода-вывода в цифровых вычислительных комплек-сах, снижает -их надежность. Наиболее близким к предлагаемому по технической сущности, является мультиплексный канал, содержащий блок приема информации, группа входов которого является группой информационных входов канала, первый и второй выход соединен непосредственно и через первый сдвиговый регистр с соответствующими информационными входами блока передачи информации, другие информационные входы которого подключены соответственно к выходам регистра управляющего слова и второ го сдвигового регистра, группа выходов - к группе информационных выходов канала, а управляющий вход к первым входам блока управления,входу элемента.И-ИЛИ и первым управ ляющим входам коммутатора адреса, блока приема информации и узла связи с процессором, вход-выход которо го соединен с магистралью обмена с процессором, информационный выход с информационными входами первого и второго сдвиговых регистров, регистра управляющего слова, регистра текущего адреса данных, текущего счетчика данных, блока управления и через регистр номера перифери ного устройства с информационным вх дом коммутатора адреса, группа выхо дов которого подключена к адресным входам блоков приема и передачи информации и формирователя синхроимпульсов, группа выходов которого яв ляется группой синхросигналов канала, второй выход блокч управления соединен с счетными входами текущего счетчика данных и регистра текущего адреса данных, выходами соединенных с соответствующими входами узла связи с процессором и блока управления,- группа выходов которого подключена к группе управляющих вых дов канала, вторые выходы сдвиговых регистров соединены с соответствующими входами узла связи с процессором 2. Недостаток этого устройства состоит в ограниченной области применения. Цель.изобретения - расширение об ласти применения канала. Поставленная цель достигается тем, что в мультиплексном канале, содержащем блок приема информации, группа выходов которого является группой информационных входов канала, блок передачи информации, группа выходов которого является группо информационных выходов канала, блок синхронизации, первая группа выходов которого является группой выходов синхронизации канала, блок упра ления, выход которого соединен с ад ресными входами блоков приема и переда.чи информации и блока синхрониз ции, регистр сдвига, первый вхГД и выход которого соединены COOTBCI4ственно с выходом блока приема информации и информационным входом блока передачи информации, второй вход с синхронизирующим входом блока передаци информации и управляющим выходом блока синхронизации, а третий вход - с первым входом узла связи с процессором и информационными входами регистра текущего адреса данных и текущего счетчика данных, входывыходы которых подключены к магистрали ввода-вывода канала, входам-выходам регистра сдвига и блока управления и первому входу-выходу узла связи с процессором, второй входвыход которого является входом-выходом канала, а первый вход соединен с выходом текущего счетчика данных, управляющие входы текущего счетчика данных и регистра текущего адреса данных и первый управляющий вход блока синхронизации подключены к труп.пе выходов блока управления, первый информационный вход блока синхронизации подключен к магистрали вводавывода канала, вторая группа выходов и два тактовых входа являются соответственно группой выходов запуска и первым и вторым тактовыми входами канала, второй информационный вход блока синхронизации, второй и третий управляющие входы и информационный выход под| лючены соответственно к первым и второму выходам и входам узла связи с процессором, вход и выход блока управления соединены соответственно с первым тактовым входом канала и третьим входом регистра сдвига, а также тем, что блок управления содержит регистр управления коммутаторами, формирователь микро- команд и память, первый вход-выход которой через узел связи с памятью соединен с входом-выходом блока и информационным входом регистра вправления коммутаторами, выходом подключенного к выходу блока, а управляющим входом - к группе выходов формирователя микрокоманд, первый вход и выход которого соединены соответственно с входом и выходом счетчика, а второй вход - с входом блока, и тем, что блок синхронизации содержит коммутаторы синхроимпульсов и сигналов начала обмена, адресные еходы которых подключены к адресному входу блока, группы выходов - соответственно к первой и второй группам выходов блока, а информационные входы - соответственно выходам триг гера синхроимпульсов и триггера начала обмена, нулевые входы которых соединены с выходом узла формирования длительности сигнала обмена, а единичные - соответственно с выходом элемента И-ИЛИ и первым управля ющим входом блока, счетчик, управляющим входом соединенный с выходом триггера синхроимпульсов и первым у равляющим входом блока, информацион ным входом - с вторым информац-ионным входом блока, а выходом - с пер вым входом элемента И-ИЛИ и информационным выходом блока, выход элемен та И-ИЛИ подключен к первым входам узлов формирования длительности сигналов обмена и частоты обмена, вторые входы которых соединен с информационными входами блока и регист ра задержек, а третьи входы - с первыми управляющими входами блока и регистра задержек, вторым управляющим входом подключенного к выходу элемента .И, первый вход которого сое динен с вторым тактовым входом блока и четвертым входом узла формирования длительности сигнала обмена, а второй - с выходом триггера разрешения единичный и нулевой входы которого соединены соответственно с вторым и первым управляющими входами блока второй, третий, четвертый и пятый входы элемента И-ИЛИ соединены соответственно с выходами узла формирова ния частоты обмена, регистра задержек, третьим управляющим и первым та товым входами блока, а также тем, чт узел ,рмирования длительности си|- налов обмена содержит сдвиговый регистр, выходом и тактовым входом сое диненный соответственно с выходом и четвертым входом узла, а группой входов - с группой выходов буферного регистра, входы которого являются соответственно вторым и третьим входами узла, и элемент И, входами сое диненный соответственно с первым и третьим входами узла, а выходом - с управляющим входом регистра сдвига. На чертеже представлена блочная схема мультиплексного канала. Мультиплексный канал содержит регистр 1 текущего адреса данных, текущий счетчик . данных, регистр 3 сдвига, узел связи с процессором представляющий собой, например уст ройство мультиплексирования информации, принимаемой из гфоцессора и селектирования информации, выдаваемой в процессор, память 5 канала узел 6 связи с памятью, например представляющий собой счетчик с управлением, формирователь 7 микрокоманд., выполненный, например на кольцевом сдвигающем регистре и формирующий микрокоманду при наличии единицы в соответствующем триггере кольцевого регист ра, счетчик 8, триггер 9 начала обмена, триггер 10 разрешения, триггер 11 синхроимпульсов, входной триггер 12, коммутаторы соответственно входной информации, выходной информации , синхроимпульсов и сигналов начала обмена, узел 17 формирования длительности сигналов обмена, регистр 18 сдвига, буферный регистр 19. регистр 20 задержки, узел 21 формирования частоты обмена, состоящий из регистра 22 сдвига и буферного регистра 23, регистр 2it управления коммутаторами, элементы И , элемент И-ИЛИ 28, шины 29 микрокоманд, шины 30 адреса, магистрали сврди с. процессором, ввода-вывода (связи с регистрами) канала и связи с г амятью, тактовые шины 3 и 35 канала, информационных грулп входов Зб и выходов 37, группы выходов 38 синхроимпульсов и группы запускающих выходов 39. Блок +0 приема информации содержит коммутатор 13 входной информации и входной триггер 12, а блок k передачи информации - коммутатор 1 выходной информации и элемент И 25. Блок 42 улравления включает формирователь 7 микрокоманд, узел 6 связи с памятью 5 и регистр управпения коммутаторами. Блок синхронизации состоит из счетчика 8, коммутатора 15 и триггера 11 синхроимпульсов, коммутатора 16 и триггера 9 сигнала начала обмена, элементов И 27 и И-ИЛИ 28, узла 17 Формирования длительности сигналов обмена, включающего регистр 18 сдвига, буферный регистр 19 и элемент И 26, триггера 10 разрешения и регистра 20 задержек и узла 21 формирования частоты обмена. Устройство работает следующим образом. В память 5 (встроенное запоминающее устройство) канала предварительно из процессора через магистрали в соответствующие ячейки записиваются коды настройки канала на обмен с подключенными периферийными устройствами. Эти коды для каждого периферийного устройства содержат информацию о начальном адресе ячейки массива оперативной памяти (ОЗУ) процессора, куда переписывается ийформация или откуда считывается информация, длине массива, адресе данного периферийного устрэйства, длительности импульсов обмена, длительности задержки между импульсом начала обмена и первым синхроимпульсом слова, частоте обмена, сигнале начала обмена. Коды для каждого периферийного устройства в памяти 5 располагаются в порядке перечисленном выше. Для инициирования обмена с каким-либо периферийным устройством процессор выдает в канал начальный адрес массива, в котором находятся коды настройки канала на обмен с этим периферийным устройством. Начальный адрес массива памяти 5 записывается в узел 6, который выполняет считывание кодов настройки из памяти. Одновременно со считыванием кодов настройки формирователь 7 команд организует выдачу микрокоманд строго в определенной последовательности и строго определенного количества, по которым считываемые коды записываются cooTBetcTBeHно в регистр 1 текущего адреса, текущий счетчик 2, регистр 2k, буферный регистр 19, в регистр.20 задержки, в буферный регистр 23 Последняя микрокоманда формирует сигнал начало обмена, который поступает на три гер 9 и через элемент И 2б на входы регистра 18 сдвига, переписывая тем самым код длительности импульсов обмена из буферного регистра 19 в регистр 18 сдвига. Код длительности и импульсов обмена представляет собой единицу в одном определенном разряде и нули в остальных разрядах. Единица в разряде определяет длительность импульсов обмена. Сдвигаясь в регистре 18 сдвига она сбрасывает триггер 9 начала обмена и триггер 11 синхроимпульсов, определяя длительность импульсов обмена. Сигнал начала обмена поступает на KOMhtyTaTop 16 и в зависимости от кода в регистре 2 проходит на со ответствующую шину обмена с периферийным устройством. Микрокоманда, форми ющая сигнал начала обмена, также взводит триггер 10 разрешения, который разрешает прохождение тактовых импульсов на регистр 20 задержки. Сдвиг единицы, записанной в определенный разряд регистра 20 задержки, определяемой кодом настройки, задается время задержки между сигналом начала обмена и первым синхроимпульсом. При наличии единицы в последнем разряде регистра 20 тактовый импульс проходит на выход ячейки ИИЛИ 28 и взводит триггер 11 синхроимпульсов, одновременно запуская узел 17 формирования длительности сигналов обмена. На выходе триггера 11 синхроимпульсов сформируется синхроимпульс, который пройдет через коммутатор 15 в соответствии с кодом, записанным в регистр , и выйдет на соответствующую магистраль обмена с периферийным устройством. Тактовый импульс с выхода ячейки И-ИЛИ 28 поступает на входы регистра 22 сдвига, переписывая в него код настройки с буферного регистра 23. Сдвиг единицы этого кода определяет частоту выдачи синхроимпульсов каналов. Синхроимпульсы одновременно поступают в регистр 3, выдвигая из него информацию или вдвигая информацию и на счетчик 8, который определяет число синхроимпульсов в слове обмена. Сигнал переполнения счетчика 8 поступает в узел , который по этому сигналу организует обмен с процессором в режиме непосредс 7венного доступа к ОЗУ с начальным адресом ячейки массива, записанным в регистре 1 и объемом массива, записанным в текущем счетчике 2. В режиме записи информации в периферийные устройства информация из ОЗУ записывается в регистр 3 а в режиме чтения из периферийных устройств информация из регистра 3 записывается в ОЗУ. Для осуществления обмена с другим периферийным устройством процессор выдает в канал начальный адрес массива памяти 5 этого периферийного устройства и процесс работы канала происходит аналогично. Таким образом, предлагаемый мультиплексный канал обеспечивает возможность обслуживания периферийных устройств с различными временными диаграммами обмена и различными длительностями сигналов обмена путем ввода в память канала для каждого периферийного устройства кодов определяющих временные параметры обмена. Формула изобретения 1, Мультиплексный канал, содержащий блок приема информации, группа входов которого является группой информационных входов канала, блок передачи информации, группа выходов ко торого является группой информационных выходов канала, блок синхронизации, первая группа выходов которого является г эуппой выходов синхронизации канала, блок управления, выход которого соединен с адресными входами блоков приема и передачи информации и блока синхронизации, регИстр сдвига, первый вход и выход которого соединены cooTBeTctseHHo с выходом блока приема информации и информационным входом блока передачи информации, второй вход - с синхронизирующим входом блока передачи информа ции и управляющим выходом блока син ронизации, а третий вход - с первым входом узла связи с процессором и информационными входами регистра текущего адреса данных и текущего счетчика данных, входы-выходы которых подключены к магистрали вводавывода канала, входам-выходам регистра сдвига и блока управления и первому входу-выходу узла связи с процессором, второй вход-выход кото рого является входом-выходом канала а первый вход соединен с выходом текущего счетчика данных, управляющие входы текущего счетчика данных и регистра текущего адреса данных и первый управляющий вход блока синхронизации подключены к группе выходЬв блока управления, о т л и чающийся тем, что, с целью расширения области применения канала, первый информационный вход блока синхронизации подключен к магист рали ввода-вывода канала, вторая гр па выходов и два тактовых входа являются соответственно группой выходов запуска и первым и вторым тактовыми входами канала, второй инфор мационный вход блока синхронизации, второй и третий управляющие входы и информационный выход подключены соответственно к первому и второму вы ходам и входам узла связи с процессором, вход и выход блока управления соединены соответственно с пергвым тактовым входом канала И третьим входом регистра сдвига. 2. Канал по п. 1, отличающийся тем, что блок управле9910 ния содержит регистр управления коммутаторами, формирователь микрокоманд и память, первый вход-выход которой через счетчик соединен с входом-выходом блока и информационным входом регистра управления коммутаторами, выходом подключенного к выходу блока, а управляющим входом - к группе выходов формирователя микрокоманд, первый вход и выход которого соединены соответственно с входом и выходом счетчика, а второй вход - с входом блока. 1, о т л и ч а3. Канал по п. ю щ и и с я тем, что блок синхронизации содержит коммутаторы синхроимпульсов и сигналов начала обмена, адресные входы которых подключены к адресному входу блока, группы выходов - соответственно к первой и втоРой группам выходов блока, а информационные входы - соответственно к выхо дам триггера синхроимпульсов и триггера начала обмена, нулевые которых соединены с выходом узла формирования длительности сигнала обмена, а единичные - соответственно с выходом элемента И-ИЛИ и первым управляющим входом блока, счетчик, управляющим входом соединенный с выходом триггера синхроимпульсов и первым управляющим входом блока, информационным -ВХОДОМ - с вторым информационным входом блока, а выходом - с первым входом элемента И-ИЛИ и информационным выходом блока, выход элемента И-ИЛИ подключен к первым входам узла формирования длительности сигналов обмена и частоты обмена, вторые входы которых соединены с информационными входами блока и регистра задержек, а третьи входы - с первыми управляющими входами блока и регистра задержек, вторым управляющим входом подключенного к выходу элемента И, первый вход которого соединен с вторым тактовым входом блока и четвертым входом узла формирования длительности сигналов обмена, а второй - с выходом триггера разрешения, единичный и нулевой аходы которого соединены соответственно с вторым и первым управляющими входами блока, второй, третий, четвертый и пятый входы элемента И-ИЛИ соединены соответственно с выходами узла формирования частоты обмена, регистра задержек, третьим управляющим и первым тактовым входами блока.

, Канал по пп, 1 и 3i отличающийся тем, что узел формирования длительности сигналов обмена содержит сдвиговый регистр, выходом и тактовым входом соединенный соответственно с выходом и четвертым входом узла, а группой входов - с группой входов буферного регистра, входы которого являются соответственно вторым и третьим входами узла, и элемент И, входами соединенный соответственно с .первым и третьим входами узла, а выходом - с управляющим входом регистра сдвига.

5. Канал попа. 1иЗ отлиЧающийся тем, что узел формирования частоты обмена содержит буферный регистр и регистр сдвига, выход которого является выходом блок а первая группа входов соединена с выходами буферного регистра, входы которого являются вторым и третьим входами блока, вторая группа входов регистра сдвига является первым входом блока.

Источники информации, принятые во внимание при экспертизе

1.Карцев М.А. Архитектура ЦВМ. М., Наука, 1978, § 3.2.2.

2.Авторское свидетельство СССР N° 769522, кл. G Об F 3/0, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Мультиплексный канал | 1978 |

|

SU769522A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

Авторы

Даты

1982-09-07—Публикация

1980-11-28—Подача