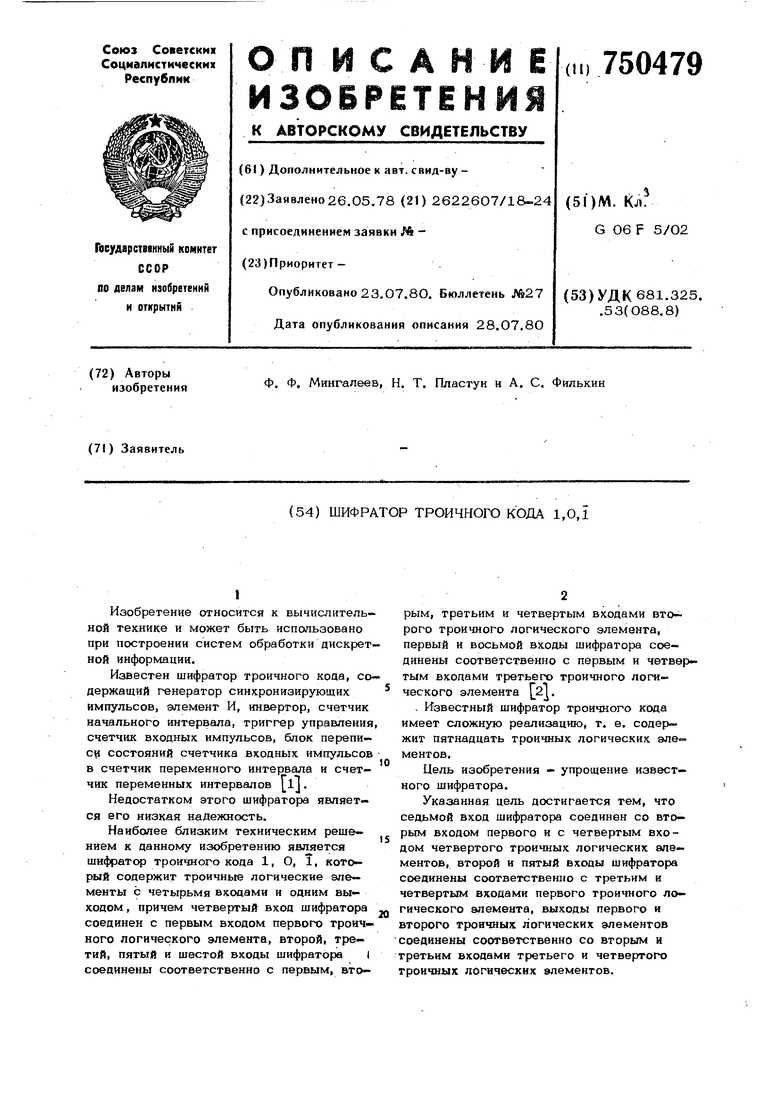

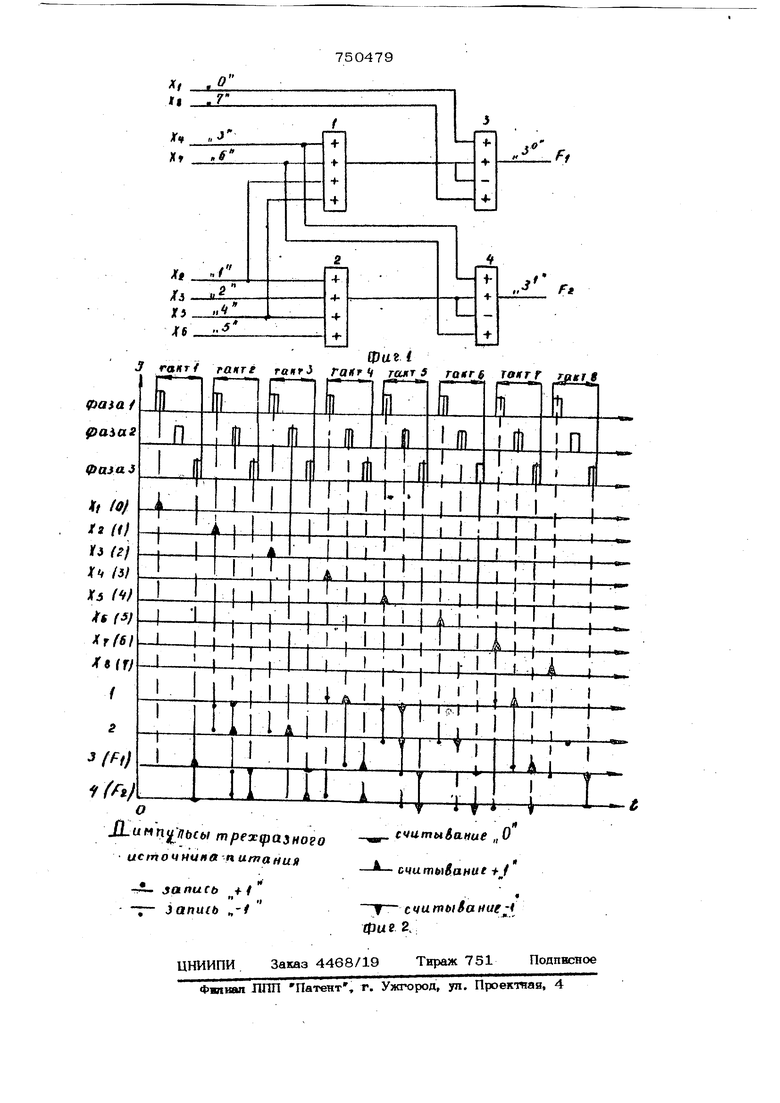

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискрет ной информации. Известен шифратор троичного кода, со держащий генератор синхронизирующих импульсов, элемент И, инвертор, счетчик начального интервала, триггер управления счетчик входных импульсов, блок переписи состояний счетчика входных импульсов в счетчик переменного интервала и счетчик переменных интервалов ij. Недостатком этого щифратора является его низкая надежность. Наиболее близким техническим решением к данному изобретению является шифратор троичного кода 1, О, 1, который содержит троичные логические элементы с четырьмя входами и одним выходом , причем четвертый вход шифратора соединен с первым входом первого троичного логического элемента, второй, третий, пятый и шестой входы шифратора I соединены соответственно с первым, вто- рым, третьим и четвертым входами второго троичного логического элемента, первый и восьмой входы шифратор соединены соответственно с первым и четвертым входами третьего троичного логического элемента 2. . Известный шифратор троичного кода имеет сложную реализацию, т. е. содержит пятнадцать троичных логических элементов. Цель изобретения - упрощение известного шифратора. Указанная цель достигается тем, что седьмой вход шифратора соединен со вторым входом первого и с четвертым входом четвертого троичных логических апементов, второй и пятый входы шифратора соединены соответственно с третьим и четвертым входами первого троичного логического элемента, выходы первого и второго троичных логических элементов соединены соответственно со вторым и третьим входами третьего и четвертого троичных логических элементов. 7504 На фир. 1 изображена блок-схема шифратора; на фиг, 2 - фаао-импульсная диаграмма его работы. Предлагаемый шифратор троичного ко да 1, О, 1 содержит четыре троичных

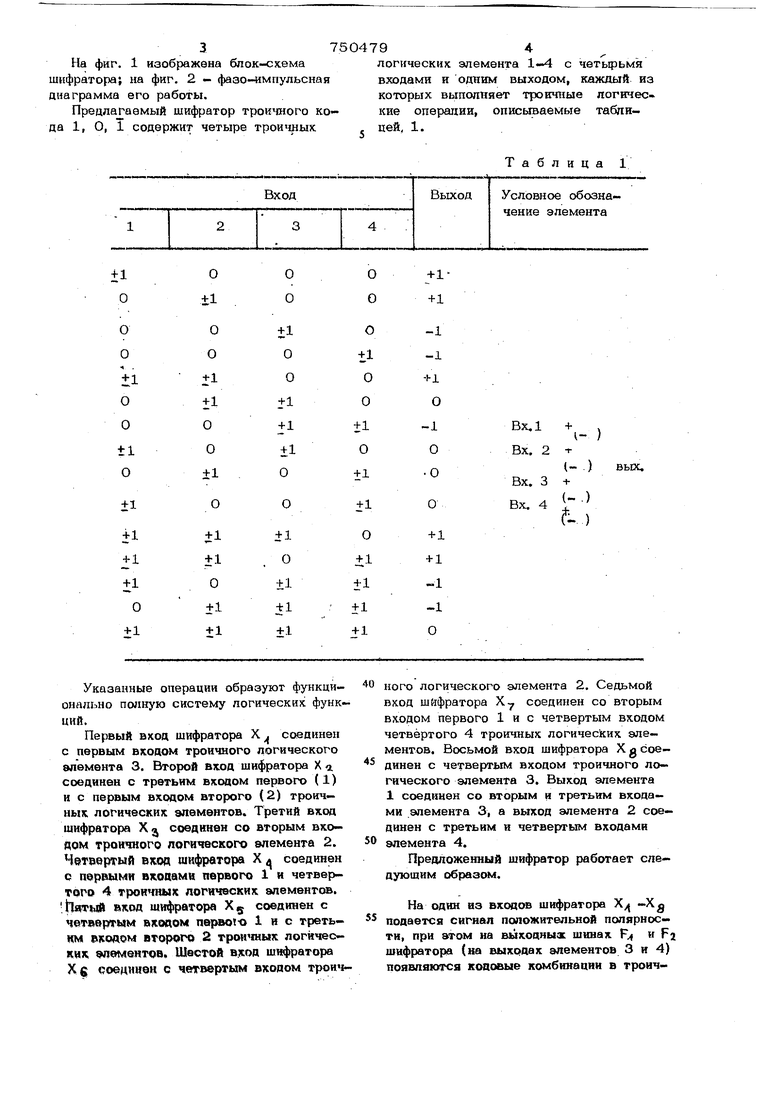

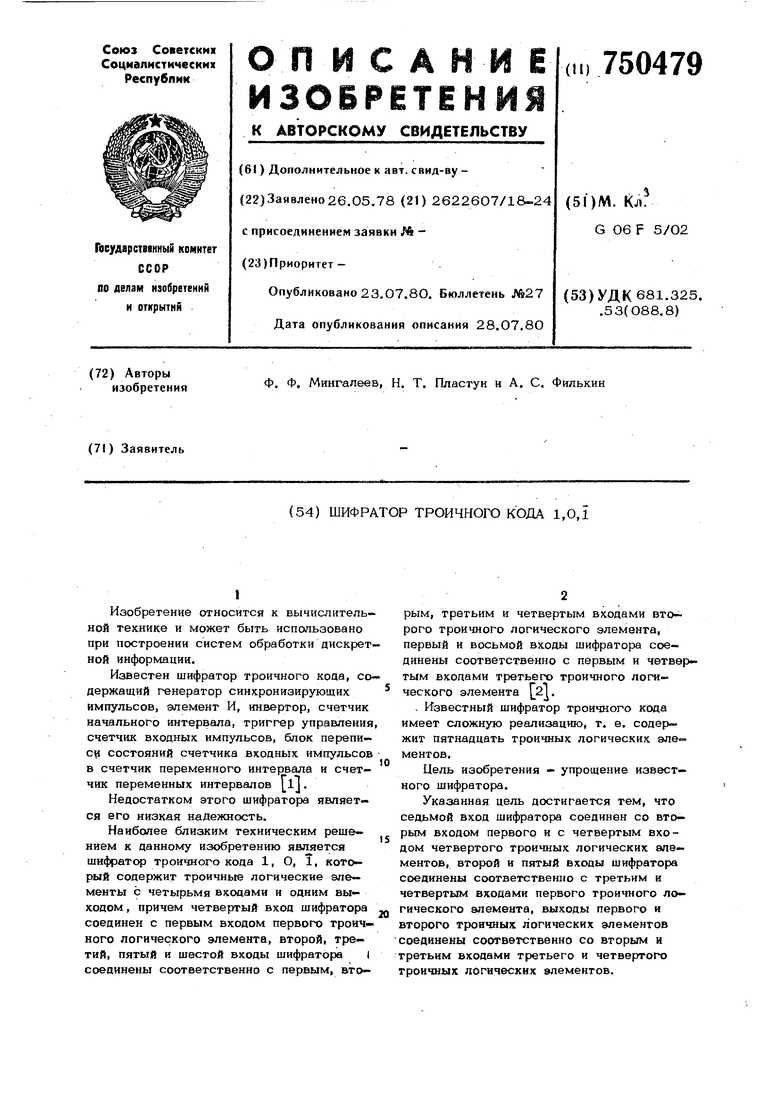

Таблица 1 9 логических элемента 1-4 с четьфьмя входами и одним выходом, каждый из которых выполняет троичные логические операции, описываемые таблицей, 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Двоичный п-разрядный счетчик импульсов | 1976 |

|

SU678675A1 |

| Преобразователь троично-десятичногоКОдА B КОд СЕМиСЕгМЕНТНОгО иНдиКАТОРА | 1979 |

|

SU851393A1 |

| Преобразователь двоичного кодаВ ТРОичНый КОд 1,0,1 | 1979 |

|

SU796838A1 |

| Дешифратор | 1986 |

|

SU1345352A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1980 |

|

SU898416A1 |

| Устройство для выполнения операции "трехзначная коньюнкция | 1982 |

|

SU1075412A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Дешифратор троичного кода 1,0,1 | 1983 |

|

SU1106015A1 |

О

о ±1

1 О

О

О

о о +1

+1

О

о

.

О

±1 +1 о о ±1 о

+1

о

+1

±1

±1 о

О

о

О

±1

+1

+1 о

+1

+1

±1

±1

о

+1

±1

о

Htl

+1 +1

+1

Указанные операции образуют функционально полную систему логических функций.

Первый вход шифратора X соединен с первым входом троичного логического алвмента 3, Второй вход шифратора Ха соединен с третьим входом первого (1) и с первым входом второго (2) троичных логических эпементов. Третий вход шифратора X« соединен со вторым входом троичного логического элемента 2. Четвертый вкод шифратора X соединен с первыми входами первого 1 и четвертого 4 троичных логических элементов. Ьятый вход шифратора Х соединен с четвертым входом пврвото 1 и с третькм входом второго 2 троичных логических здемеитов. Шестой в.ход шифратора Xg соединен с четвертым входом троичо о

+1+1

-1 -1 +1

о

Вх,1 . -1

о

Вх. 2 -г

(- )

вых. о Вх. 3 +

ВХ.4 (-

о

f-)

+1 +1

1

- 1

-1 о 1

него логического элемента 2. Седьмой вход шифратора Ху соединен со вторым входом первого 1 и с четвертым входом четвёртого 4 троичных логических элементов. Восьмой вход шифратора X g соединен с четвертым входом троичного логического элемента 3. Выход элемента 1 соединен со вторым и третьим входами элемента 3, а выход элемента 2 соединен с третьим и четвертым входами

элемента 4.

Предложенный шифратор работает следующим образом.

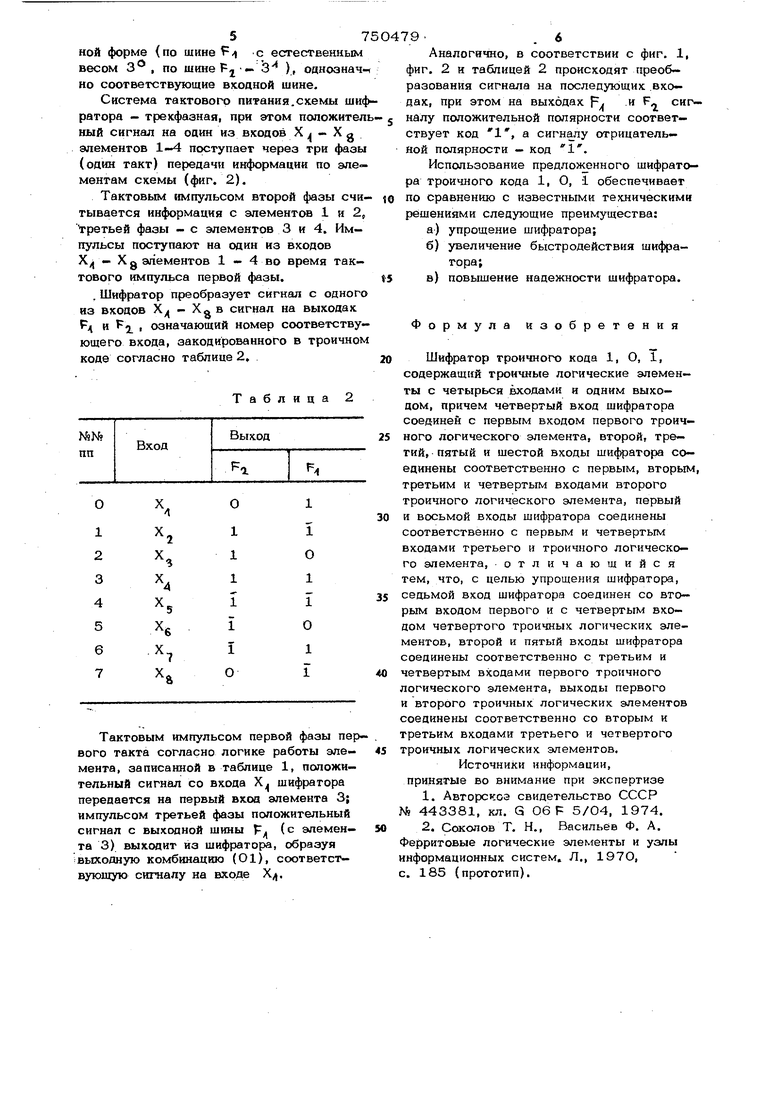

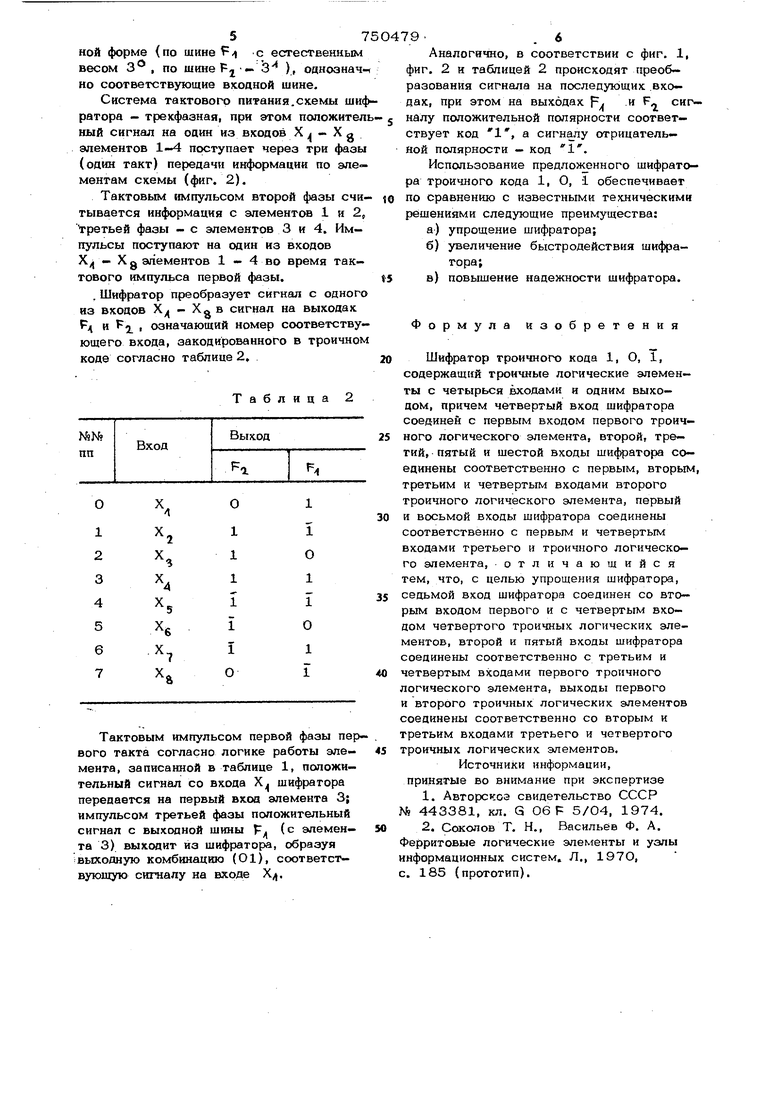

На один из входов шифратора Х -Х подается сигнал положительной полярности, при этом на выходных шинах F и р} шифратора (на выходах элементов 3 и 4) появляются кодовые комбинации в троичной форме (по шине 1 с естественны весом З , по шинеР -. З ), одноана но соответствующие входной шине. Система тактового питания,схемы ш ратора - трехфазная, при этом положите ный сигнал на один из входов X - X g элементов 1-4 поступает через три фаз (один такт) передачи информации по эле ментам схемы (фиг. 2). Тактовым импульсом второй фазы сч тывается информация с элементов 1 и 2 третьей фазы - с элементов 3 и 4. Импульсы поступают на один из входов Х - XQ элементов 1 - 4 во время так тового импульса первой фазы. ,Шифратор преобразует сигнал с одно - Хл в сигнал на выходах из входов X. А и 2. означающий номер соответству ющего входа, закодированного в троично коде согласно таблице 2, Таблица 2 Тактовым импульсом первой фазы пер вого такта согласно логике работы элемента, записанной в таблице 1, положительный сигнал со входа Х шифратора передается на первый вход элемента 3; импульсом третьей фазы положительный сигнал с выходной шины р. (с элемен- та 3) выходит из шифратора, образуя выходную комбинацюо (О1), соответствующую сигналу на входе . Аналогично, в соогватствии с фиг. 1, фиг. 2 и таблицей 2 происходят преобразования сигнала на последующих .входах, при этом на выходах р .и F сигналу положительной полярности соответствует код 1, а сигналу отрицательной полярности - код I. Использование предложенного шифратора троичного кода 1, О, 1 обеспечивает по сравнению с известными техническими решениями следующие преимущества: а)упрощение шифратора; б)увеличение быстродействия шифратора;в)повышение надежности шифратора. Формула изобретения Шифратор троичного кода 1, О, 1, содержащий троичные логические элементы с четырься входами и одним выходом, причем четвертый вход шифратора соединен с первым входом первого троичного логического элемента, второй, третий, пятый и шестой входы шифратора соединены соответственно с первым, вторым, третьим и четвертым входами второго троичного логического элемента, первый и восьмой входы шифратора соединены соответственно с первым и четвертым входами третьего и троичного логического элемента, отличающийся тем, что, с целью упрощения шифратора, седьмой вход шифратора соединен со вторым входом первого и с четвертым входом четвертого троичных логических элементов, второй и пятый входы шифратора соединены соответственно с третьим и четвертым входами первого троичного логического элемента, выходы первого и второго троичных логических элементов соединены соответственно со вторым и третьим входами третьего и четвертого троичных логических элементов. Источники информации, принятые во внимание при экспертизе 1.Авторскоа свидетельство СССР 443381, кл. Q 06 R 5/04, 1974. 2.Соколов Т. Н., Васильев Ф. А. Ферритовые логические элементы и узлы нформационных систем. Л., 197О, . 185 (прототип).

Авторы

Даты

1980-07-23—Публикация

1978-05-26—Подача