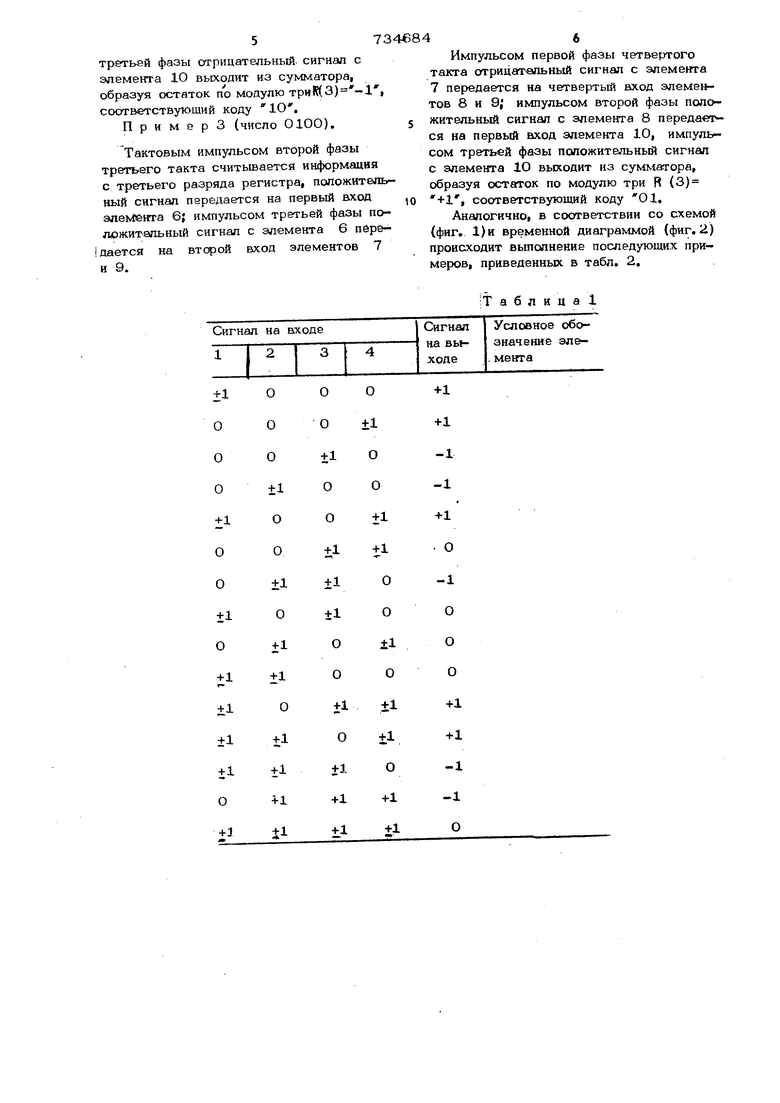

Изобретение относится к вычислительной тахнике и монсет быть использовано при проектировании аппаратуры кп.я автоматического контроля цифровых вычислительных устройств. Известны сумматоры по модулю три, выполненные на ферроидных логических элементах CQ. Эти сумматоры имеют большое количество оборудования и невысокую надежность. Известны сумматоры по модулю три, выпопнанныа на троичных логических элементах (2. Эти сумматоры также имеют большое количество оборудования, (содержат шесть логических элементов). Наиболее близким техническим решением к предложенному являе-тся сумматор но модулю три, содержащий троичные логические элементы, шина первого слагаемого соединена с первым входом nei вого троичного логического элемента, ко второму входу которого подключена шина второго слагаемсйго. Выход первого троич ного логического элемента соединен с первыми входами второго н третьего троичных логических элемеятов, выходы которых подключены соответственно к nepBOf - и второму входам четвертого троичного логического эламента, выход которого подключен к выходной шине сумматора 3. Известньй сумматор имеет сложную схему, поскольку он выполнен на пяти логических элементах. Цель изобретения экономия оборудования. Указанная цель достигается тем, о шина BTJOporo слагаемого соединена с третьим входом первого троичного логического элемента и вторым входом третьехо троичного логического элемэн- та. Шина первого слагаемого подключена к четвертому входу первого троичного логического элемента, третьему входу третьего троичного логического элемента и второму аходу второго троичного, логического элемента, третий вход кото роге подключен к шине второго слагае- MoroVa четвертый вход - к выходу первого троичного логического элемента и четвертому входу третьего троичного логического элемента. Выход третьего логического элемента соединен с третьим входом четвертого троичного логического элемента, четвертый вход которого подключен к выходу второго троичного логического элемента. Сумматор по модулю три собран на четырех троичных логических элементах, каждый из которых выполняет троичные операции, описьтаемые 1абл, 1, Указанные операции образуют -функционально полную систему логическах функций и мо

гут быть реализованы с помощью троичных элементов.

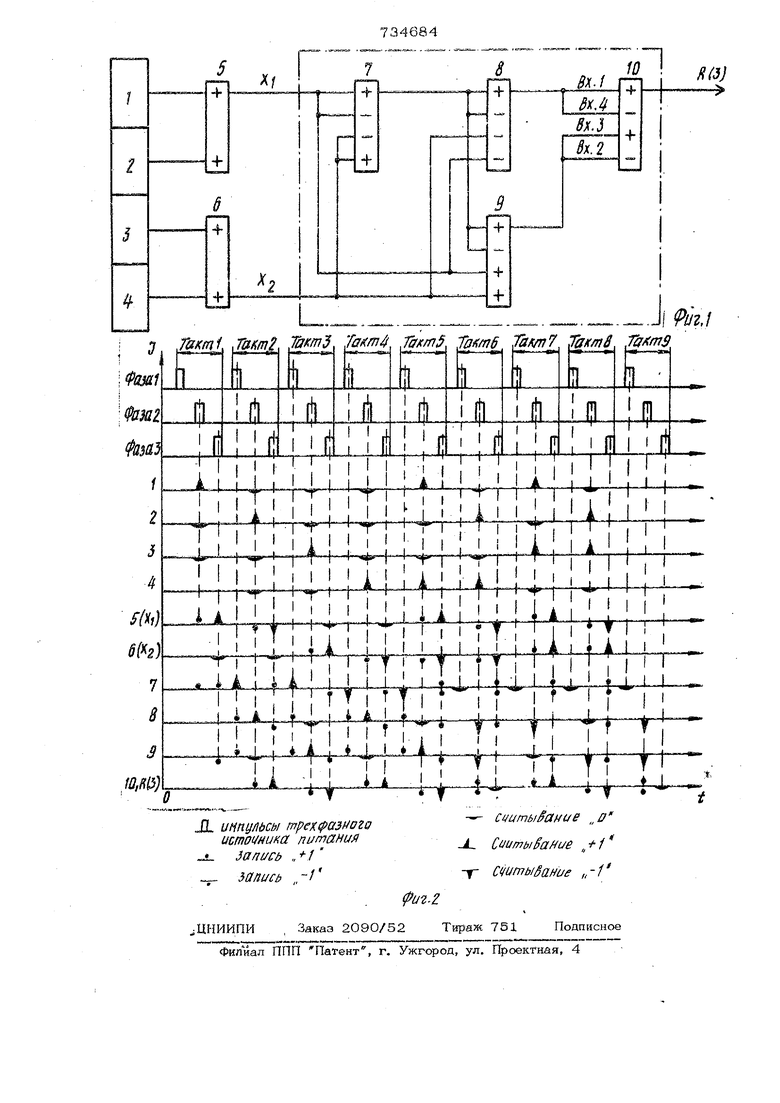

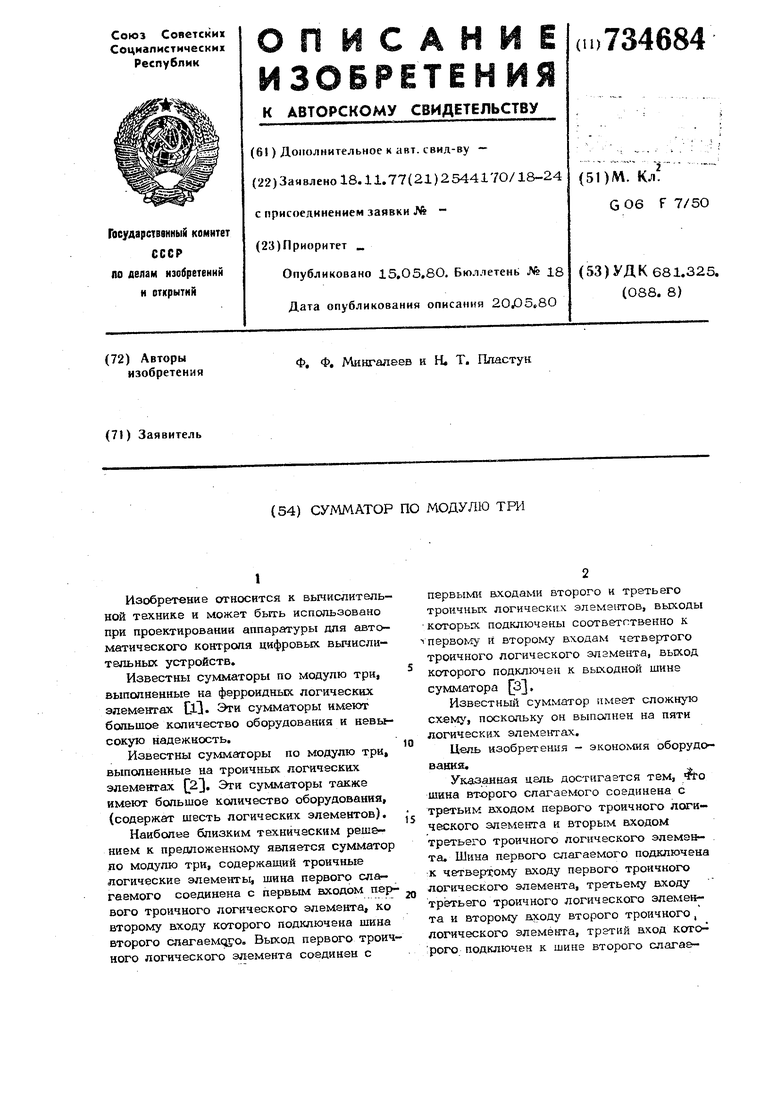

На фиг, 1 изображена схема формирования остатка четырехзначного числа, на фиг, 2 дана временная диаграмма работы сумматора,

Четырехразрядное число находится в разрядах 1-4 регистра. Троичные логические элементы 5 и 6 определяют остаток по модулю три четвертичных цифр, расположенных В двух соседнах разрядах.

Сумматор по модулю три (совокупность троичных логическах элементов 7-10) определяет остаток по модулю три от суммы цифр, поступающих на входы элементов 5 и 6 из разрядов 1-4 регистра. Выходы разрядов регистра соединены с входами троичных логическах элементов 5 и 6. Выход элемента 5 (шина первого слагаемого Xj) соединен с первым и четвертым входами первого элемента 7, со вторым нходом второго элемента 8 и с третьим аходом треть-е го элемента 9 сумматора. Выход элемета 6 (шина второго слагаемого Х) сое динен со вторым и третьим входами первого элемента 7, с третьим входом второго элемента 8, а вторым аходом третьего элемента 9 сумматора, Вьпсрд первого троичного логического элемента 7 соединен с первыми и четвертыми аходами второго и третьего логическах элементов 8 а 9 сумматора. Выход второго логического элемента 8 соединен с первым и четвертым аходами четвертого элемента Ю, а выход третьего .логического элемента 9 со вторым и третьим входами элемента Ю сумматора. На выходе четвертого троичного логического элемента 1О сумматора формируется остаток

по модулю три R (3),

Система тактового питания сумматора - трехфазная, при этом каждый

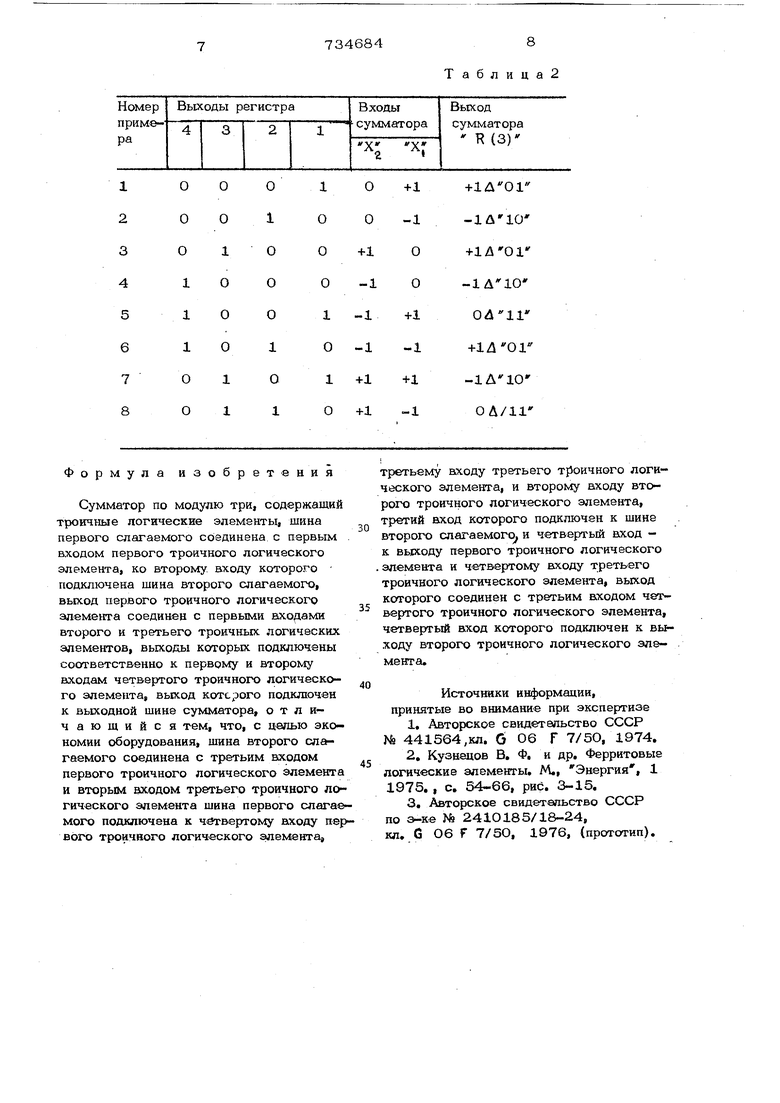

табл, 2, 1 в двоичной системе счисления представляется положительным сигналом в разряде, а О - отсутствием сигнала в разряде. Числа на разрядах регистра меняются в каждом такте последовательно в соответствии с табл, 2 (фиг, 1,2),

Пример 1 (число ОО01).

Тактовым импульсом второй фазы первого такта считывается информации с первого разряда регистра и, согласно логике работы элемента, записанной в табл, 1, положительный сигнал с первого разряда регистра 1 передается на первый аход элемента 5 импульсом третьей фазы, Попожительный сигнал с элемента 5 передается на первый вход элемента 7 и третий аход элемента 9,

Импульсом первой фазы второго такта положительный сигнал с элемента 7 передается на первый вход элементов 8 и 9, импульсом второй фазы положительный сигнал с элемента 8 передается на первый аход элемента Ю; импульсом третьей фазы полож1ательный сигнал с элемента 1О выходит из сумматора, образуя остаток по модулю три R (3) +1, соответствующий коду 01,

П р и м е р 2 (число ОО1О), Тактовым импульсом второй фазы второго такта считьшается информация со второго разряда регистра, положительный .сигнал передается на второй аход элемента 5; импульсом третьей фазы отрицательный сигнал с элемента 5 передается на четвертый аход элемента 7 и второй вход элемента 9,

Импульсом первой фазы третьего так5 та положительный сигнал с элемента 7 передается на первый аход элементов 8 и 9; импульсом второй фазы положительный сигнал с элемента 9 передается на третий вход элемента lOj импульсом следующий разряд слагаемого поступает на аход сумматора через три фазы (один, такт) передачи информации по элементам схемы (фиг, 2), Тактовым импульсовм первой фазы считывается информация с троичного логического элемента 7, импульсом второй фазы - с разрядов 1-4 регистра и троичных логических элементов 8,9, а импульсом третьей фазы - с троичных логическах элементов 5,6 и 10. Рассмотрим работу сумматора по модулю три на примерах определения остатков восьми чисел, представленных в

третьей фазы отрицательньШ сигнал с элемента 10 выходит из сумматора, образуя остаток по модулю триК(3)-1, соответствующий коду 1О,

П р и м е р 3 (число 0100).

Тактовым импульсом второй фазы третьего такта считывается информация с третьего разряда регистра, положительный сигнал передается на первый нход 6; импульсом третьей фазы положительный сигнал с элемента 6 передается на второй вход элементов 7

и 9.

Импульсом первой фазы четвертого такта отрицательный сигнал с 3jieMefrra 7 передается на четвертый вход элементов 8 и 9; импульсом второй фазы положительный сигнал с элемента 8 передает ся на первьй вход элемента 10, импульсом третьей фазы попожитьтьный сигнал с элемента 10 выходит из сумматора, образуя остаток по модулю три R (3) , соответствующий коду 01,

Аналогично, в соответствии со схемой (фиг. 1)и временной диаграммой (фиг. 2) происходит выполнение последующих примеров, приведенных в табл. 2.

:t а б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1976 |

|

SU638960A1 |

| Троичный сумматор | 1978 |

|

SU953637A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

о

о

о

о

+1

о

о

+1

о

о

+1

о

±1

±1 ±1

о

+1

о о +1 о

+1

о

+1

+1

±3.

+1

+1 +1

11

+1

1 о о +1

+1

-1

-1

+1

о

+1 о о

-1

о

о

о

+1

+1

-1

-1

о

Формула изобретения

Сумматор по модулю три, содержащий троичные логические элементы, шина первого слагаемого соединена с первым входом первого троичного логического элемента, ко второму, входу которого подключена шина второго слагаемого, выход первого троичного логического элемента соединен с первыми входами второго и третьего троичных логических элементов, выходы которых подключены соответственно к первому и второму входам четвертого троичного логического элемента, выход которого подключен к выходной шине сумматора, отличающийся тем, что, с целью экономии оборудования, шина второго слагаемого соединена с третьим входом первого троичного логического элемента и вторым входом третьего троичного логического элемента шина первого слагаемого подключена к четвертому нходу первого троичного логического элемента,

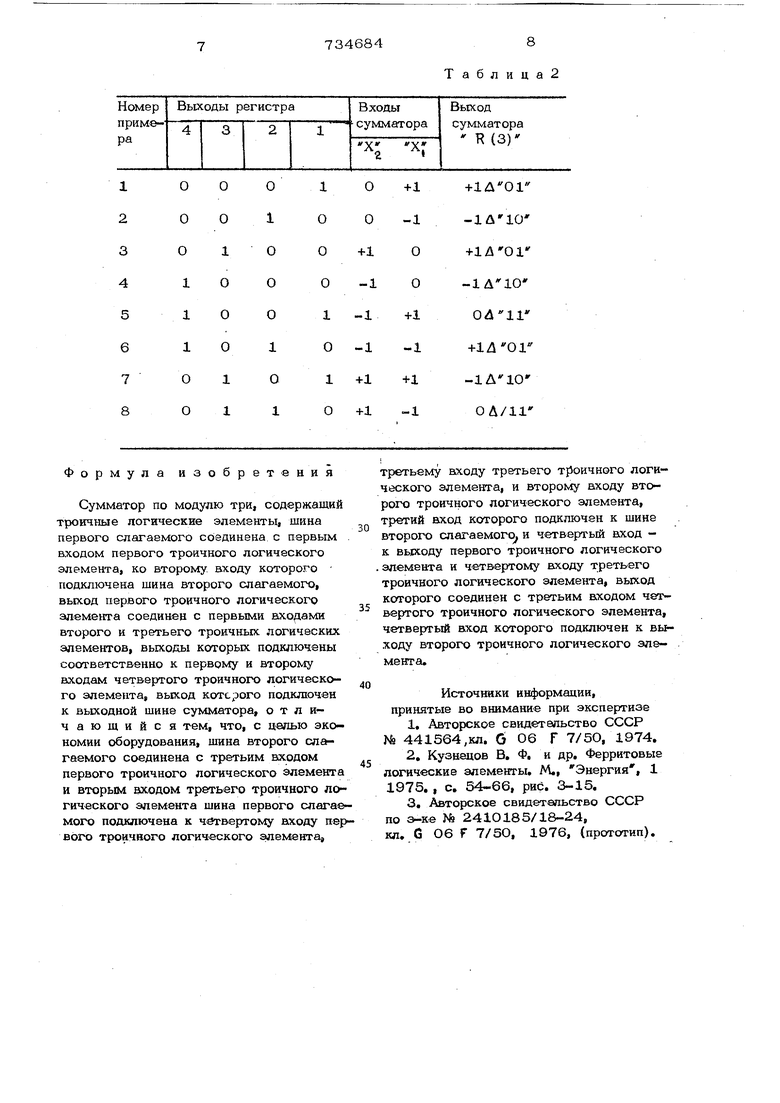

Таблица2

третьему нходу третьего троичного логического элемента, и второму входу второго троичного логического элемента, третий аход которого подключен к шине второго слагаемого, и четвертый вход к выходу первого троичного логического . элемента и ч етвертому аходу третьего троичного логического элемента, выход которого соединен с третьим аходом четвертого троичного логического элемента, четвертый аход которого подключен к вььходу второго троичного логического элемет-а.

Источники информации, принятые во внимание при экспертизе

кл. G Об Г 7/5О, 1976, (прототип).

Тзкт 7йкт4 Тв(т$

Авторы

Даты

1980-05-15—Публикация

1977-11-18—Подача