1

Изобретение относится к вычислительной технике и дискретной авто матике и мохгет быть использовано в устройствах математического моделиро-, вания для сложения сигналов.

Известные устройства для сложения сигналов, выполненные на операционных усилителях не могут быть использованы для сложения в системе j,. остаточных классов l .

Наиболее близким по технической сущности к предложенномуЯвляется устройство для сложения сигналов в системе остаточных классов, содер- 5 жащее дифференциальный усилитель, неинвертирующий вход которого через первый и второй масштабные резисторы соединен с источниками входных сигналоН, а инвертирующий вход диффе- 20 ренциального усилителя через третий масштабный резистор подключен к его выходу, четвертый масштабный резистор, один вывод которого подключен к инвертирующему входу дифференциаль- 25 ного усилителя, и источники напряжения 2 .

Недостатком данного устройства сложения в системе остаточных классов является то, что входные сиг-- ЗО

«налы могут принимать максимальные значения, не превышающие половину динамического диапазона выходного напряжения в узле и недостаточное быстродействие из-за задержки выполнения операций на время переходного процесса.

Цель изобретения - повышение быстродействия и расширение динамического диапазона входных сигналов.

Это достигается тем, что в устройство введены компаратор и ключи, выходы которых соединены со вторым выводом четвертого масштабного резистора, вход первого ключа подключен к первому источнику напряжения, вход второго ключа соединен с шиной нулевого потенциала, управляющие входы ключей связаны с выходом компаратора, первый вход которого соединен со вторым источником напряжения, а второй вход подключен к неинвертирующему входу дифференциального усилителя.

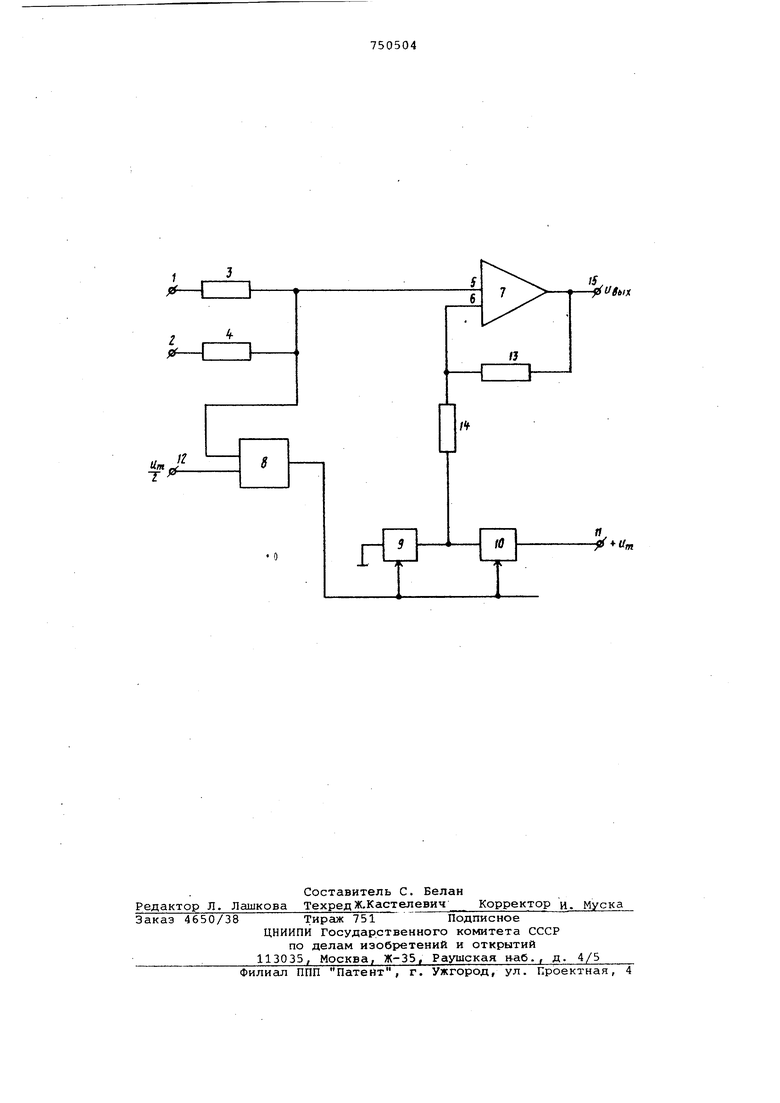

На чертеже представлена блок-схема устройства.

Устройство для сложения сигналов в системе остаточных класссв содержит источник 1 и 2 входных сигналов Ил соответственно, первый масштабный резистор 3, второй масштабный резисто 4 f неинвертируюгдий 5 и инвертирующий 6 входы дифференциального усилителя 7, компаратор 8, ключи 9 и 10, источ никн напряжения 11 и 12, третий-масшта бный резистор 13, четвертый масштабный резистор 14, выход 15 дифференциального усилителя. Входные сигналы от источников 1 и 2 сумт ируются на масштабных резисторах 3 и 4 и поступают на неинвертирующий вход 5 дифференциального усилителя 7 и один из входов компаратора 8, ко второму входу компаратора 8 подключен источник напряжения 12. Выход компаратора 8 соединен с управляющими входами ключей 9 и 10, подключающих инвертирующий вход б дифференциального усилителя 7 через резистор 14 или к шине нулевого потенциала, или к источнику напряжения 11. Результат суммировани снимается с выхода 15 дифференциального усилителя 7 и через масштабный резистор 13 подается на инвертирующий вход б дифференциального усилителя 7. Устройство работает следующим образом. Входные сигналы и и Ur, от источников входных сигналов 1 и 2 суммируются на резисторах 3 и 4. Резуль тат суммирования подается на неинвер тирующий вход б дифференциального уси лителя 7 и на один из входо}з компаратора 8. На второй вход компаратора подается сигнал Urn/2 от источника на пряжения 12, где Цт напряжение, пропорциональное модулю т. При равенстве резисторов 3 и 4 напряжение на входе усилителя 7 будит равно ()/2 Таким образом, если (U,)/2 меньше, чем и,т 11, т.е. то выходной сигнал компаратора 8 буд таким, что ключ 9 подключает резистор 14 к шине нулевого потенциала. При этом ключ 10 разомкнут. На выход 15 дифференциального усилителя 7 долж но устанавливаться такое напряжение )k которое обеспечивает величину вхойных напряжений дифференциального усилителя 7,при котором удовлетворяется равенство A i 4 i i . 1 R, Ra «л R: R, и соответственно где R. резисторов 3,4 14 и 13При RfR Ueb,. U, + u,. Если же сигнал на входе 5 усилителя 7 и компаратора 8 превышает Um/2 то выходной сигнал компаратора 8 ста новится таким, что ключ 9 размыкаетс К резистору 14 подключается напряжеHHeUrn . В этом случае выходное напряение усилителя 7 станет таким, что, как и в предыдущем случае, будет обеспечено равенство входных сигналов силителя 7. В этом случае будет справедливо ледующее соотношение е,ыч -01 i-v з которого при равенстве сопротивлеий Нд К R R R получаем U 4 и т - и , п Устройство нашло применение в аналоговых и гибридных вычислительных блоках, использующих для представления информации непозиционную систему счисления в остаточных классах. По данному техническому предложению на предприятии был изготовлен макет, который показал работоспособность данного устройства. Выполнение суммирования и сравнения на входе усилителя обеспечило повышение быстродействия и расширение динамического диапазона изменения входного напряжения . Формула изобретения Устройство для сложения сигналов в системе остаточных классов, содержащее дифференциальный усилитель, неинвертирующий вход которого через первый и второй масштабные резисторы соединен с источниками входных сигналов, а инвертирующий вход дифференциального усилителя через третий масштабный резистор подключен к его выходу, четвертый масштабный резистор, первый вывод которого подключен к инвертирующему входу дифференциального усилителя, и источники напряжения, о тличающееся тем, что, с целью повышения быстродействия и расширения динамического диапазона входных сигналов, в него введены компаратор и ключи, выходы которых соединены со вторым выводом четвертого масштабного резистора, выход первого ключа подключен к первому источнику напряжения, вход второго ключа соединен с шиной нулевого потенциала, управляющие входы ключей связаны с выходом компаратора, первый вход которого соединен со вторым источником напряжения, а второй вход подключен к неинвертирующему входу дифференциального усилителя. Источники информации, принятые во внимание при экспертизе 1.Коган Б.Я.Электронные моделирующие устройства.Л.,Физматлит,1959 с. 58-61. 2.Авторское свидетельство СССР № 362312, кл. G 06 Q 7/12, 1973(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения модуля | 1978 |

|

SU741279A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 1987 |

|

RU1709841C |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| Преобразователь напряжение-ток | 1987 |

|

SU1478131A1 |

| Усилитель-ограничитель | 1983 |

|

SU1124334A1 |

| Устройство для выделения модуля | 1981 |

|

SU980102A1 |

| Функциональный преобразователь | 1980 |

|

SU886013A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Устройство для вычисления функции @ = @ | 1984 |

|

SU1167621A1 |

Авторы

Даты

1980-07-23—Публикация

1978-02-13—Подача