(5) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты повторения импульсов | 1977 |

|

SU687602A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Умножитель частоты | 1979 |

|

SU811250A1 |

| Умножитель частоты | 1979 |

|

SU813728A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство умножения частоты следованияиМпульСОВ | 1979 |

|

SU822327A1 |

| Следящий умножитель частоты | 1979 |

|

SU840892A1 |

1

Изобретение относится к измерительной технике и автоматике и может быть использовано для повышения быстродействия процесса преобразования частоты при работе с низкочастотными датчиками.

Известен умножитель частоты, содержащий делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, входной и выходной формирователи, запоминающий регистр и блок управления, один из выходов которого подключен к нулевым входам всех разрядов делителя опорной частоты и запоминающего регистра, нулевой выход каждого разряда счетчика импульсов соединен с первым входом первого блока элементов И, второй вход которого подключен ко второму выходу блока управления, а выход - к единичному входу того же разряда запоминающего регистра, причем, третий выход блока управления

подключен к единичным входам всех разрядов счетчика импульсов, единичный выход каждого разряда запоминающего регистра соединен со входом второго блока элементов И, выход которого соединен с единичным входом того же разряда счетчика импульсов опорной частоты, а второй вход - с выходной шиной выходного формирователя, вход которого подключен к вы«Оходу счетчика импульсов опорной частоты lJ.

Недостатком устройства является возможность появления ложной информации.

IS

Известен умножитель частоты, содержащий генератор импульсов, суммирующий счетчик, вычитающий счетчик, делитель частоты, схемы переноса кода, триггеры, элементы И и элемент

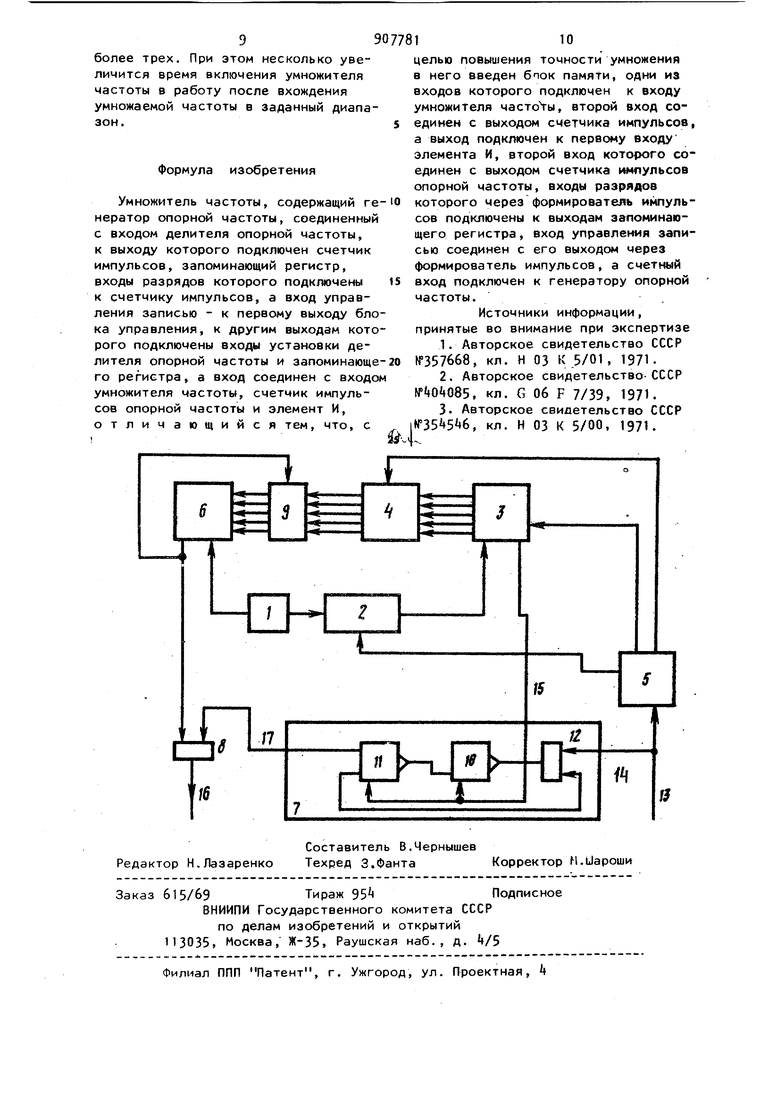

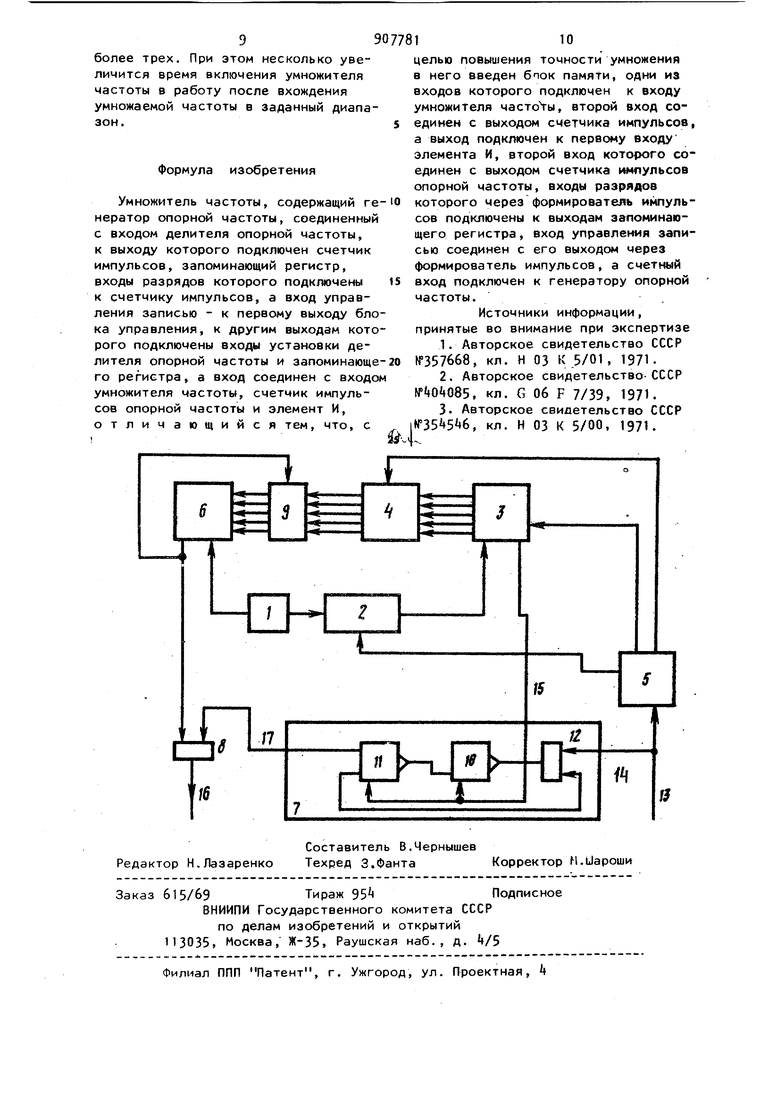

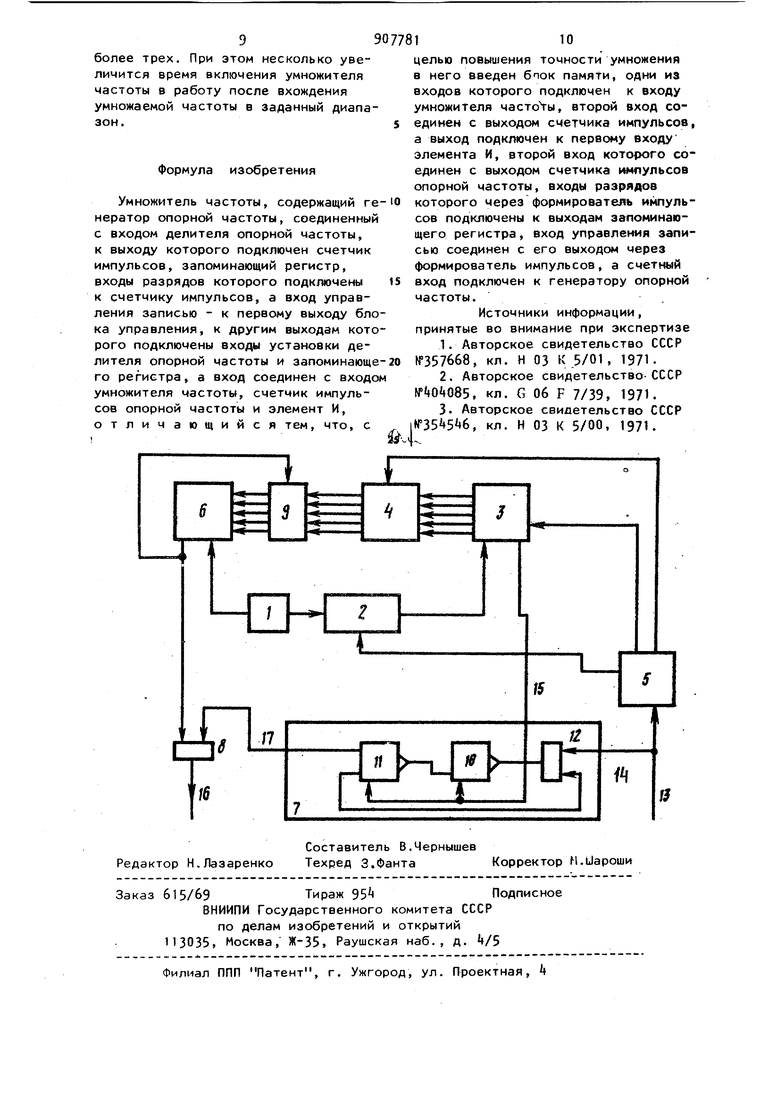

20 ИЛИ, в котором генератор импульсов соединен со входами суммирующего счетчика и делителя частоты, выход суммирующего счетчика соединен с выходом устройства и с первыми управ ляющими входами схем переноса кода, вторые управляющие входы которых подключены к различным выходам перво го триггера, кодовые входы схем переноса кода подключены к выходам вычитающих счетчиков, а выходы схем переноса кода соединены со входами суммирующего счетчика, выход делителя частоты соединен с первыми входами элементов И, вторые входы которых подключены к различным выходам первого триггера, а выходы схем И соединены со входами вычитающих счетчиков, вход первого триггера через элемент ИЛИ подключен к выходам второго триггера, соединенным со входами сброса на нуль вычитающих счетчиков, а вход второго триггера соединен со входом устройства T JОднако этот умножитель частоты также имеет недостаток, заключающийся в том, что при значении входной частоты меньше нижнего предела диапа зона входной частоты на выходе их имеются импульсы с некоторой частотой. Объясняется это тем, что при снижении входной частоты ниже минимального значения на вход счетчика, подключенного к выходу делителя опор ной частоты поступает количество импульсов , превышающее числовую емкость этого счетчика. Поэтому счетчик может устанавливаться в различнее состояния, опреде ляемые дробной частью дел-ения перио да, имеющейся в данный момент входной частоты на период входной частоты, соответствующий нижнему значению диапазона умножаемых частот. Частота на выходе умножителя в этом случае может принимать значения, находящиеся в диапазоне от выходной частоты, соответствующей нижнему пределу диапазона входной частоты, до выходной частоты, во много раз превышающей ее значение, соответствующее верхнему пределу диапазона входной частоты, до выходной частоты во много раз превышающей ее значение, соотпетствующее верхнему преде лу диапазона входной частоты. Причем превышение это тем больше, чем больш чй.словые емкости примененных в умно жителе счетчиков, выбранные из усло вия ограничения погрешности дискрет ности умножителя частоты. Следовательно, описанный умножитель частоты также может давать на выходе ложную информацию. Наиболее близким по технической сущности к предлагаемому является умножитель частоты, содержащий генератор опорной частоты, делитель опорной частоты, счетчики импульсов, входной формирователь, блок управления, запоминающий регистр, сравнивающее устройство и выходной формирователь, причем генератор опорной частоты соединен со входами первого счетчика и делителя опорной частоты, к выходу которого подключен второй счетчик, к выходам разрядов второго счетчика подключены входы запоминающего регистра , выходы запоминающего регистра и выходы первого счетчика соединены со сравнивающим устройством, к выходу которого подключен выходной формирователь, соединенный с выходом устройства и со входом сброса на нуль первого счетчика, вход блока управления подключен к выходу входного формирователя, соединенного со входом устройства, к первому выходу схемы управления подключены входы сброса на нуль делителя опорной частоты, запоминающего регистра и первого счетчика, к второму выходу блока управления подключена цепь управления записью в запоминающий регистр числа из второго счетчика, а к третьему выходу блока управления подключен вход сброса на нуль второго счетчика. Для предотвращения выходной частоты при нулевом значении входной частоты в этом устройстве имеются дополнительно триггер, элемент И и сравнивающее устройство,, одни входы которого подключены к счетчику, соединенному с делителем опорной частоты, другие его входы подключены к запоминающему регистру, а выход дополнительного сравнивающего устройства через триггер соединен с одним входом элемента И, другой вход которого подключен к генератору опорной частоты, а выход элемента И соединен со входом счетчика опорной частоты З. Однако известный умножитель частоты имеет ряд недостатков, снижающих его точность. Предотвращение выходной частоты при нулевом значении входной частоты в этом устройстве получено за смет 5 снижения его точности в диапазоне умножаемых частот. При снижении входной частоты в каждом периоде входной частоты прекращается подача импульсов с выхода умножителя часто ты на время, равное разности последующего и предшествующего периодов. Это объясняется тем, что при каждом достижении во втором счетчике числа равного числу в регистре, прекращается подача импульсов генератора опорной частоты на вход первого сче чика. Таким образом, при снижении входной частоты в каждом периоде входной частоты умножитель на некоторое время прекращает выполнять свою функцию. При значении входной частоты меньше нижнего предела диапазона умножаемых частот на выходе его появляются пачки импульсов с частотой принимающей значения, находящиеся в диапазоне от выходной частоты, соответствующей нижнему пределу диапазона входной частоты, до выходно частоты, во много раз превышающей ее значение, соответствующее верхне му пределу диапазона умножаемых частот. Не выполняется в этом умножителе частоты в полной мере и предотвраще ние выходных импульсов при нулевом значении частоты. Так при каждом случайном одиночном импульсе, поступающем на вход умножителя частоты, на выход.е его появляется пачка импульсов с некото рой частотой. Кроме отмеченного, рассмотренный умножитель частоты имеет пониженную точность и за счет того, что период выходной частоты на границе двух периодов умножаемой частоты имеет увеличенное значение, доходящее до удвоенного по сравнению с требуемым. Объясняется это увеличение выходного периода тем, что в момент окончания очередного периода умножаемой частоты в первом счетчике может содержаться число, близкое к числу, хранящемуся в запоминающем регистре. Однако, при окончании периода умножаемой частоты этот счетчик сбрасывается на нуль и затем сно ва накапливает импульсы. Цель изобретения - повышение точности умножения. Эта цель достигается тем, что в умножитель частоты, содержащий гене1ратор опорной частоты, соединенный с входом делителя опорной частоты, к выходу которого подключен счетчик импульсов, запоминающий регистр, входы разрядов которого подключены к счетчику импульсов, а вход управления записью - к первому выходу блока управления, к другим выходам которого подключены входы установки делителя опорной частоты и запоминающего регистра, а вход соединен с входом умножителя частоты, счетчик импульсов опорной частоты и элемент И, введен блок памяти, один из входов которого подключен к входу умножителя частоты, второй вход соединен с выходом счетчика импульсов, а выход подключен к первому входу элемента И,.второй вход которого соединен с выходом счетчика импульсов опорной частоты, входы разрядов которого через формирователь импульсов подключены к выходам запоминающего регистра, вход управления записью соединен с его выходом через формирователь импульсов, а счетный Вход подключен к генератору опорной частоты. На чертеже приведена структурная электрическая схема умножителя частоты . Умножитель частоты содержит генератор 1 опорной частоты, делитель 2 опорной частоты, счетчик 3 импульсов, запоминающий регистр , блок 5 управления, счетчик 6 импульсов опорной частоты, блок 7 памяти с не менее чем тремя состояниями, элемент И 8 и формирователь 9 импульсов. На чертеже представлен один из возможных вариантов исполнения блока 7 памяти с тремя состояниями, включающего в себя два триггера 10 и 11 и элемент И 12. Генератор 1 опорной частоты соединен со входами делителя 2 частоты и счетчика 6 импульсов опорной частоты. Входы разрядов запоминающего регистра 4 подключены к счетчику 3, счетный вход которого соединен с выходом делителя 2 частоты. Входы разрядов счетчика 6 импульсов опорной частоты подключены через формирователь 9 импульсов к выходам запоминающего регистра k, а вход управления записью счетчика 6 импульсов опорной частоты соединен с его выходом. Вход управления записью запоминающего регистра и входы установки в исходное состояние счетчика . 3 и делителя 2 частоты подключены к выходам блока5 управления, вход которой соединен со входом 13 умноже ния частоты, к которому подключен вход И блока 7 памяти, другой вход 15 которого соединен с выходом счетчика 3- Выход 16 умножения частоты соединен с выходом элемента И 8, один из входов которой подключен к выходу счетчика 6 импульсов опорной частоты, а второй вход - к выходу 17 устройства 7 памяти с тремя состояниями. Счетный вход триггера 10 через элемент И 12 соединен со входом 1 4 блока 7 памяти и с одним из выходов триггера 11, второй выход которого является выходом блока 7 памяти. Счетный вход триггера 11 подключен к выходу триггера 10, а входы установки в нулевое состояния триггеров 10 и 11 соединены со входом 15 блока 7 памяти. При нахождении значения входной частоты в диапазоне умножаемых частот, на который рассчитан умножитель частоты, блок 7 памяти находится в состоянии, при котором с его выхода 17 подается разрешающий сигнал на схему И 8, а импульсы, поступающие на его вход 1 со входа 13 умножите-ля частоты, не могут вывести его из этого состояния, так как элемент И 12 закрыт. В счетчике 3 за каждый период умножаемой частоты происходит накопление импульсов, поступающих с выхода делителя 2 частоты. При окончании периода умножаемой частоты в этом счетчике фиксируется число N . Ч к где fj - частота импульсов генератора 1 опорной частоты) период умножаемой частоты К - коэффициент деления делителя 2 частоты. После окончания периода умножаемой частоты сигналом с блока 5 управ ления в запоминающий регистр записывается число, зафиксированное в счетчике 3- Затем сигналом блока 5 управления счетчик 3 устанавливается в нулевое состояние. Сигналом с блока 5 управления в нулевое состояние устанавливается и делитель 2 частоты После этого снова начинается процесс накопления импульсов счетчиком 3. Счетчик 6 импульсов опорной частоты работает в режиме вычитания. При каж 9 18 дом его обнулении с выхода его подается импульс, который через открытый элемент И 8 поступает на выход 16 умножителя частоты и на вход управления записью в счетчик 6 числа, зафиксированного в запоминающем регистре 4. Период частоты на выходе умножителя частоты определяется выражанием Tj N, где Т - период частоты генератора 1 опорной частоты Следовательно, Р,( К, где F - частота импульсов на входе умножителя частоты. Если значение входной частоты становится меньше нижнего предела диапазона умножаемых частот, то происходит переполнение счетчика 3- При этом с выхода этого счетчика поступает сигнал на установочные входы триггеров 10 и 11 и триггеры устанавливаются в нулевое состояние, что приводит к закрытию элемента И 8 и, следовательно, к прекращению подачи импульсов на выход умножителя частоты и открыванию элемента И 12, При поступлении следующего импульса на вход умножителя частоты триггер 10 устанавливается в единичное состояние, а триггер 11 сохраняет нулевое состояние. Элемент И 8 остается в закрытом состоянии, а элемент И 12 в открытом. Если время между этим и последующим импульсом будет соответствовать нахождению частоты в заданном диапазоне, то переполнение счетчика 3 не произойдет и последующий импульс на входе умножителя приведет к установке триггера 10 в нулевое состояние, а триггера 11 - в единичное, элемент И 8 снова откроется и на выход умножителя будут подаваться импульсы умноженной частоты. Таким образом, умножитель частоты прекращает выдачу импульсов, как только частота на его входе станет меньше нижнего значения диапазона умножаемых частот. При нахождении входной частоты в заданном диапазоне умножаемых частот устройство памяти с тремя состояниями не снижает точность работы умножителя. Кроме этого, в предлагаемом умножителе частоты не происходит увеличение периода выходной частоты на границе двух периодов входной частоты. Следует отметить, что устройство памяти, введенное в умножитель частоты для предотвращения выдачи ложной информации может иметь число состояний 9 более трех. При этом несколько увеличится время включения умножителя частоты в работу после вхождения умножаемой частоты в заданный диапазон. Формула изобретения Умножитель частоты, содержащий ге нератор опорной частоты, соединенный с входом делителя опорной частоты, к выходу которого подключен счетчик импульсов, запоминающий регистр, входы разрядов которого подключены к счетчику импульсов, а вход управления записью - к первому выходу бло ка управления, к другим выходам кото рого подключены входы установки делителя опорной частоты и запоминающе го регистра, а вход соединен с входо умножителя частоты, счетчик импульсов опорной частоты и элемент И, отличающийся тем, что, с 1 целью повышения точности умножения в него введен бпок памяти, одни из входов которого подключен к входу умножителя частоУы, второй вход соединен с выходом счетчика импульсов, а выход подключен к первому входу элемента И, второй вход которого соединен с выходом счетчика импульсов опорной частоты, входы разрядов которого через формирователь импульсов подключены к выходам запоминающего регистра, вход управления записью соединен с его выходом через формирователь импульсов, а счетный вход подключен к генератору опорной частоты.. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №357668, кл. Н 03 К 5/01 , 19712.Авторское свидетельство-СССР №kOk085. кл. G Об F 7/39, 1971. 3.Авторское свидетельство СССР , кл. Н 03 К 5/00, 197t.

Авторы

Даты

1982-02-23—Публикация

1979-07-12—Подача