вых шин, а соответствующие выходы подключены к стробирующему входу дешифратора числовых линеек и другим входам логических элементов И.

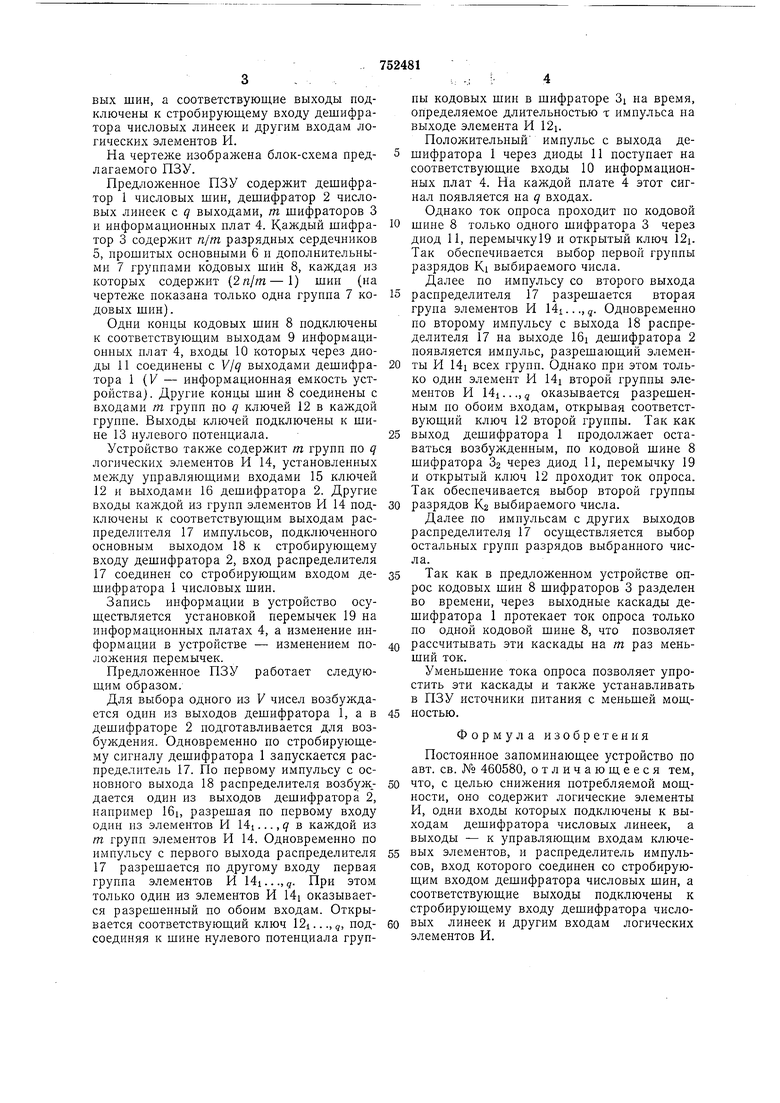

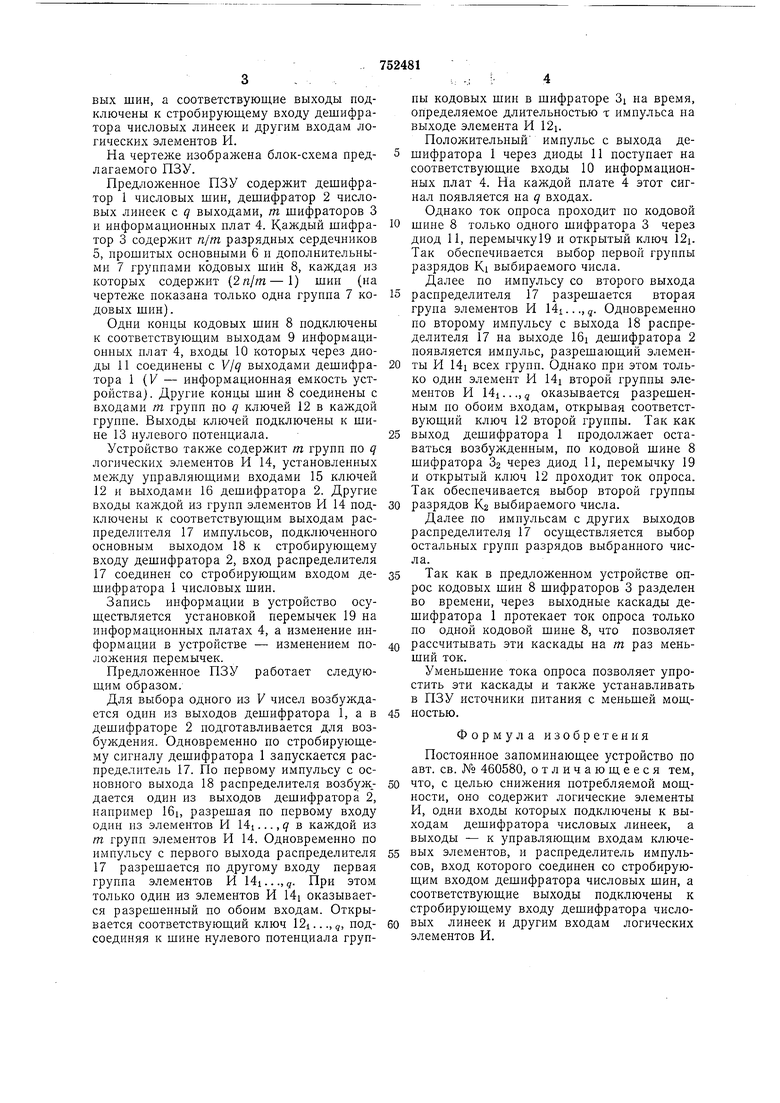

На чертеже изображена блок-схема предлагаемого ПЗУ.

Предложенное ПЗУ содержит дешифратор 1 числовых шин, дешифратор 2 числовых линеек с q выходами, т шифраторов 3 и информационных нлат 4. Каждый шифратор 3 содержит я/т разрядных сердечников 5, прошитых основными 6 и дополнительными 7 группами кодовых шин 8, каждая из которых содержит (2n/m-1) шин (на чертеже показана только одна группа 7 кодовых шин).

Одни концы кодовых шин 8 подключены к соответствуюш им выходам 9 информационных плат 4, входы 10 которых через дноды 11 соединены с Vlq выходами дешифратора 1 (V - информационная емкость устройства). Другие концы шин 8 соединены с входами т групп по q ключей 12 в каждой группе. Выходы ключей подключены к шине 13 нулевого потенциала.

Устройство также содержит т групп по q логических элементов И 14, установленных между управляюш,нми входами 15 ключей 12 и выходами 16 дешифратора 2. Другие входы каждой из групп элементов И 14 подключены к соответствуюш,им выходам распределителя 17 импульсов, подключенного основным выходом 18 к стробируюш,ему входу дешифратора 2, вход распределителя 17 соединен со стробирующим входом дешифратора 1 числовых шин.

Запись информации в устройство осуществляется установкой перемычек 19 на информационных платах 4, а изменение ннформацни в устройстве - изменением положения перемычек.

Предложенное ПЗУ работает следующим образом.

Для выбора одного из V чисел возбуждается один из выходов дешифратора 1, а в дешифраторе 2 подготавливается для возбуждения. Одновременно по стробирующему сигналу дешифратора 1 запускается распределитель 17. По первому импульсу с основного выхода 18 распределителя возбуж дается один из выходов дешифратора 2, например 16i, разрешая по первому входу один из элементов И 14i... ,q в каждой из т групп элементов И 14. Одновременно по импульсу с первого выхода распределителя 17 разрешается по другому входу первая группа элементов И 14i...,g. При этом только один из элементов И 14i оказывается разрешенный по обоим входам. Открывается соответствующий ключ 12i..., ,, подсоединяя к шине нулевого потенциала группы кодовых шин в шифраторе 3i на время, определяемое длительностью т импульса па выходе элемента И 12i.

Положительный импульс с выхода дешифратора 1 через диоды И поступает на соответствуюшие входы 10 информационных плат 4. На каждой плате 4 этот сигнал появляется на q входах. Однако ток опроса проходит по кодовой

шине 8 только одного шифратора 3 через диод И, перемычку19 и открытый ключ 12i. Так обеспечивается выбор первой группы разрядов Ki выбираемого числа.

Далее по нмпульсу со второго выхода

распределителя 17 разрешается вторая група элементов И 14i...,g. Одновременно по второму импульсу с выхода 18 распределителя 17 на выходе 16i дешифратора 2 появляется импульс, разрешающий элементы И 14i всех групп. Однако при этом только один элемент И 14i второй группы элементов И 14i..., 5 оказывается разрешенным по обоим входам, открывая соответствующий ключ 12 второй группы. Так как

выход дешифратора 1 продолжает оставаться возбужденным, но кодовой шине 8 шифратора Зз через диод 11, перемычку 19 и открытый ключ 12 проходит ток опроса. Так обеспечивается выбор второй группы

разрядов Кг выбираемого числа.

Далее по импульсам с других выходов распределителя 17 осуществляется выбор остальных групп разрядов выбранного числа.

Так как в предложенном устройстве опрос кодовых шин 8 шифраторов 3 разделен во времени, через выходные каскады дешифратора 1 протекает ток опроса только по одной кодовой шине 8, что позволяет

рассчитывать эти каскады на т раз меньший ток.

Уменьшение тока опроса позволяет упростить эти каскады и также устанавливать в ПЗУ источники питания с меньшей мощностью.

Формула изобретения

Постоянное запоминающее устройство по авт. св. № 460580, отличающееся тем,

что, с целью снижения нотребляемой мощности, оно содержит логические элементы И, одни входы которых нодключены к выходам дешифратора числовых линеек, а выходы - к управляющим входам ключевых элементов, и распределитель импульсов, вход которого соединен со стробирующим входом дешифратора числовых шин, а соответствующие выходы подключены к стробирующему входу дешифратора числовых линеек и другим входам логических элементов И.

rf

7J

ff

i

f

r/

72

f

IT

7J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи командной информации с рассредоточенных пунктов управления | 1990 |

|

SU1795500A1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Адаптивное устройство для приема информации с удаленных рассредоточенных объектов | 1986 |

|

SU1325546A1 |

| Устройство для вычисления уровня запасного оборудования технической системы | 1990 |

|

SU1756904A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Система телемеханики для рассредоточенных объектов | 1975 |

|

SU556477A1 |

| УСТРОЙСТВО ДЛЯ ТЕЛЕСИГНАЛИЗАЦИИ О СОСТОЯНИИ РАССРЕДОТОЧЕННЫХ ОБЪЕКТОВ С ОБЩЕЙ ПРОВОДНОЙЛИНИЕЙ СВЯЗИ | 1973 |

|

SU435550A1 |

/«

Tiriirr:::

Ж

Авторы

Даты

1980-07-30—Публикация

1978-05-04—Подача