1

Изобретение относится к измерительной технике,в частности к устройствам цифрового преобразования быстроменяющегося аналогового сигнала и к устройствам обработки информации.

Для осуществления преобразования аналог-код при быстроменяющихся аналоговых сигналах (относительно скорости работы преобразователя) необходима высокоточная схема выборки уровня аналогового сигнала и сохранения этого уровня с большой точностью на время преобразования его в код. Устройство данного типа носит название схемы выборки и хранения .

Известно устройство выборки и хранения аналогового сигнала, выполненное по операционной схеме.

Недостаточно большое входное сопротивление операционного усилителя интегратора приводит к малому допустимому отношению времени хранения во времени выборки.

Известны также устройства выборки и хранения, выполненные по автобуферной и буферной схемам ij .

Общим недостатком этих устройств является то, что период работы устройства складывается из времени выборки и времени хранения, причем полезным является только время хранения, в течение которого производится обработка сигналов. Уменьшение времени выборки ограничивается быстродействием операционного усилителя ,

Наиболее близким из известных по технической сутдности является аналоговое запоминаклцее устройство, содержащее входной буферный каскад, выход которого соединен с входами двух ключей, выход первого ключа соединен с входом буферного каскада

5 и накопительным конденсатором, вы- ход второго ключа соединен с входом второго буферного каскада и вторым накопительным конденсатором, выход первого буферного каскада соединен

20 с входом третьего ключа, выход второго буферного каскада соединен с входом четвертого ключа, выход третьего и четвертого ключа соединены со входом выходного каскада 2 .

2 На каждом конденсаторе этого устройства происходит поочередно запоминание (выборка) и хранение входного аналогового напряжения.

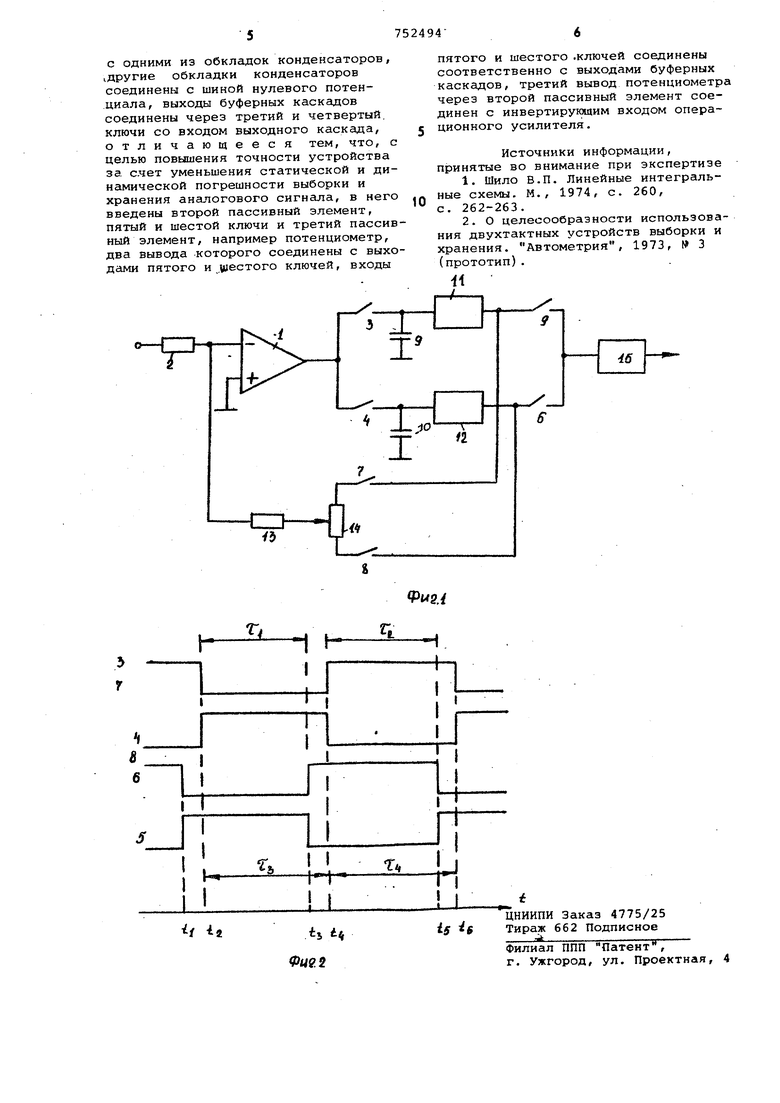

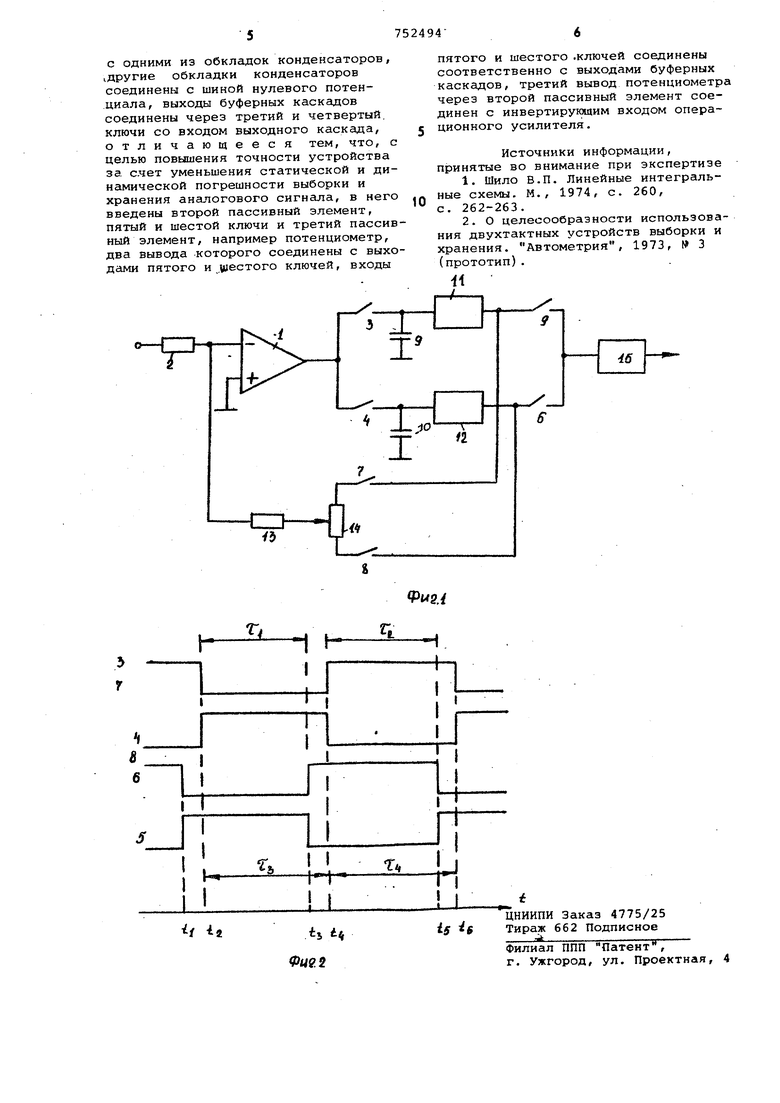

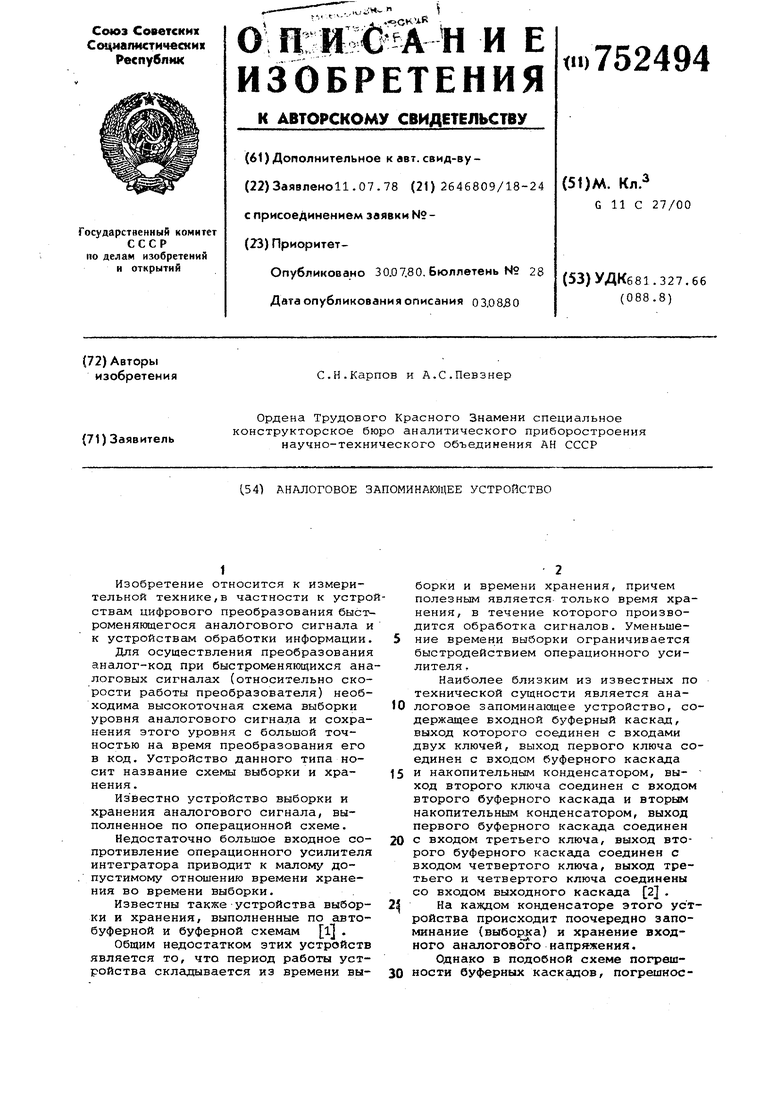

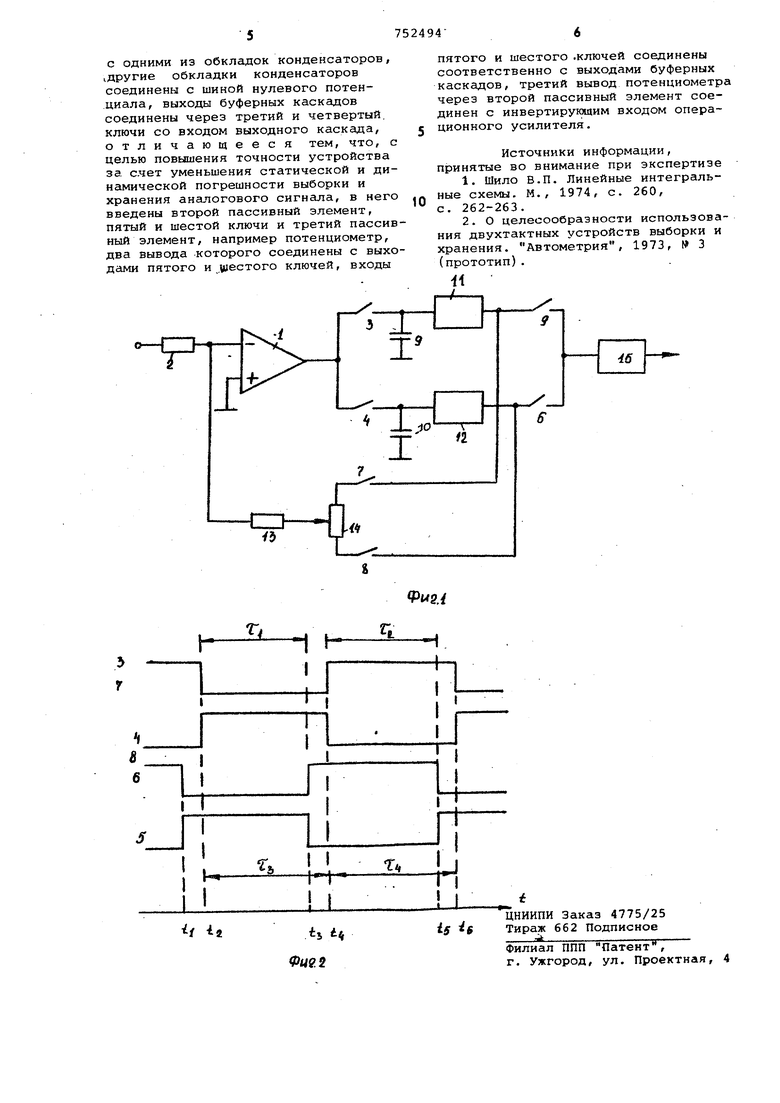

Однако в подобной схеме погрешности буферных каскадов, погрешности неидентичности накопительных конденсаторов и их буферных-каскадов целиком входят в погрешность устройства выборки и хранения. Цель изобретения - повышение точности устройства за счет уменьшения статической и динамической погрешности выборки и хранения аналогового сигнала. Поставленная цель достигается тем что в аналоговое запоминающее устройство, содержащее операционный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала, инвертирующий вход операционного усилителя подключен через первый пассивный элемент ко входу устройства, выход операционного усилителя соединен со входами первого и второго ключей, выходы которых соединены соответственно со входами буферных каскадов и накопительными эле ментами, например, с одними из обкла док конденсаторов, другие обкладки конденсаторов соединены с шиной нуле вого потенциала, выходы буферных кас кадов соединены через третий и четвертый ключи со входом выходного кас када, введены второй пассивный элемент, пятый и шестой ключи и третий пассивный элемент, например потенцио метр, два вывода которого соединены с выходами пятого и шестого ключей, входы пятого и шестого ключей соединены соответственно с выходс1ми буферных каскадов, третий вывод потенциометра через второй пассивный элемент соединен с инвертирующим входом операционного усилителя. На фиг. 1 представлена блок-схема аналогового запоминающего устройства на фиг. 2 - временная диаграмма управления ключами. Устройство содержит операционный усилитель 1, первый пассивный элемент 2, ключи 3-8, накопительные элементы, например конденсаторы 9 и 10, буферные каскады 11 и 12, второй пассивный элемент 13, третий пассивный элемент, например потенциометр 14, выходной каскад 15. Устройство работает следующим образом. В моменты времени tj, t2, t tg и t, .(, происходит переключение ключей -3-8 (фиг.2). В моменты времеу ни t , t и t происходит переключение цепи обратной связи устройства выборжи и хранения. Таким образом, в интервал времени Т замыкании от рицательной обратной связи через клю чи 4 и 8 и буферный каскад 12 происходит запоминание аналогового сигнала на конденсаторе 10, а напряжение с конденсатора 9 через буферный каскад 11, ключ 5 и входной буферный каскад 15 в течение времени 1 подается на выход устройства, при этом ключи 3 и 7 разомкнуты. Соответстенно в интервале времени i. ключи и 7 замкнуты и на конденсаторе 9, роисходит запоминание входного налогового сигнала, а ключи 4 и разомкнуты,и с конденсатора 10 апомненное за время tj напряжение ерез буферный каскад 12, ключ 6 и ыходной буферный каскад 15 в теение времени 1 подается на выод устройства. Использование операционного усиителя с большим коэффициентом усиения К дает возможность получить алую величину эквивалентной постонной времени заряда конденсатора, риведенной к входу устройства, что начительно снижает динамическую огрешность устройства выборки и ранения. Кроме того, в К-|Ь раз меньшается статическая погрешность стройства, вызванная неидентичостью накопительных конденсатоов, буферных каскадов и ключей, де 5 - коэффициент обратной свяи, равный где величина входного сопротивления пассивного элемента 2; Т, - величина сопротивления пассивного элемента 13. Испытание макетов показали, что данное устройство обладает высокой точностью выборки и хранения аналоговых сигналов при достаточном быстродействии и большом динамическом диапазоне. Наличие такого устройства позволяет значительно увеличить сферу применения и производительность аналитических систем и систем обработки информации другого назначения. За счет повышения быстродействия устройства и точности выборки данных создается экономический эффект, который на единицу продукции (на прибор) составляет 250000-300000 руб. в год. Формула изобретения Аналоговое запоминающее устройство, содержащее операционный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала, инвертирующий вход операционного усилителя подключен через первый пассивный -элемент ко входу устройства, выход операционного усилителя соединен со входами первого и второго ключей; выходы которых соединены соответственно со входами буферных каскадов и накопительными элементами, например.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1531173A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104586A1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ | 2007 |

|

RU2389070C2 |

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU966749A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-11—Подача