чен выход элемента ИЛИ и вход детектора разблокировки, выход которого подключен к второму входу блока памяти и к первому дополнительному входу блока управления, к второму дополнительному входу которого подкл чен второй выход второго накопителя, при этом выход второго клапана подклчен ко входу счетчика и первому упраляющему входу буферного накопителя непосредственно и через элемент задержки, а к первому, второму, третьему и четвертому входам элемента ИЛИ подключены соответственно управляющий выход, выход ошибка, выход запрос анализатора и первый выход блока управления, третий выход которого подключен к второму входу анализатора, причем второй вход элемента объединенный с вторым управляющим входом буферного накопителя, подключен к выходу запрос анализатора, третий управляющий вход буферного накопителя подключен к выходу ошибка анализатора.

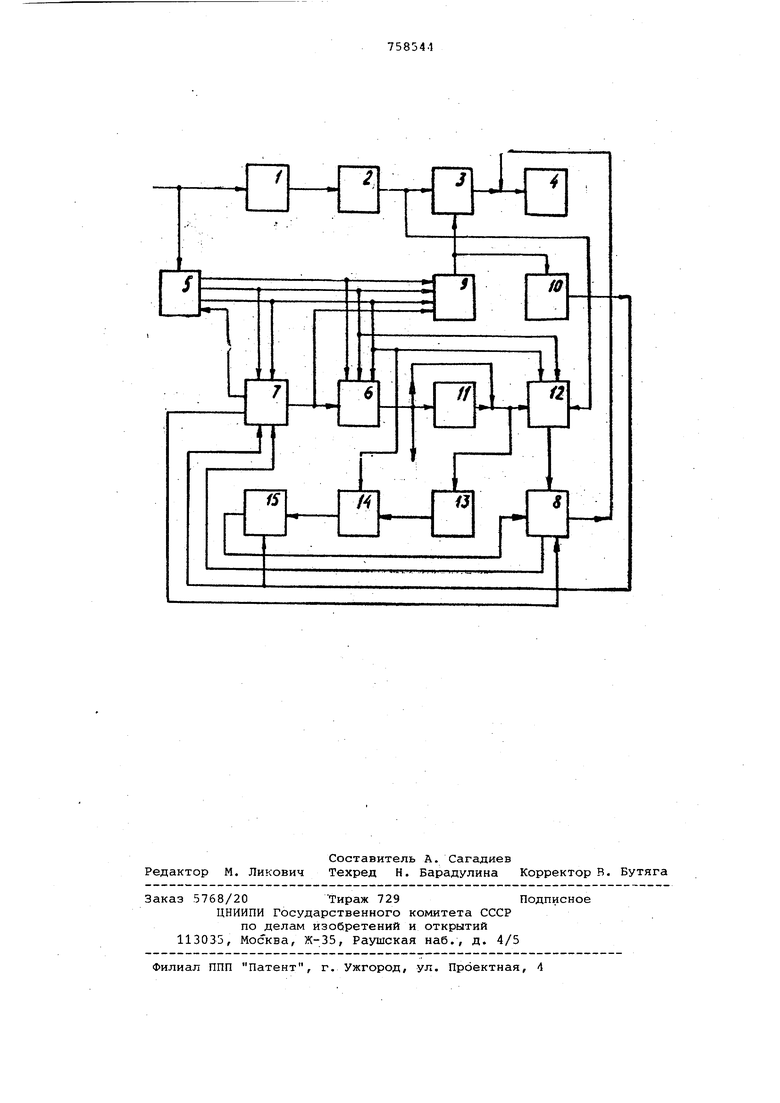

На чертеже приведена структурная электрическая схема предложенноггустройства.

Устройство для приема дискретной информации содержит декодер 1, первый накопи: ель 2, первый клапан , 3, приемник 4 информации, анализатор 5, второй клапан 6, блок 7 управления, второй накопитель 8, элемент 9 ИЛИ, детектор 10 разблокировки, элемент 11 задержки, буферный накопитель 12, счетчик 13, элемент 14 и блок 15 памяти.

Устройство для приема дискретной информации работает следующим образом.

Принимаемые из канала связи через вход устройства кодовые блоки поступают на декодер 1 и анализатор 5„ С выхода декодера 1 информационная часть кодового блока поступает в первый накопитель 2. Анализатор 5 проверяет, принятые кодовые блоки на наличие в них ошибок или команды запрос. Если анализатор 5 не обнаружил ни ошибки НИ запроса в первом кодовом блоке, то разрешается вывод информации из первого накопителя 2 через- первый клапан 3 в приемник 4. В противном случае анализатор 5 выдает со своих выходов сигнал ошибка или запрос, которые через второй клапан б поступают на управляющий выход устройства в виде сигнала переспрос для повторения с передающей станции информации. Сигнал ошибка или запрос поступают также в блок 7 и на управляющие входы буферного накопителя 12 Одновременно с этим анализатор 5 подает сигнал ошибка или запрос через элемент 9 ИЛИ на управляющий вход первого клапана 3, блокируя тем самым прохождения в приемник 4 из

первого накопителя 2 информации с ошибкой или содержащей команду запрос, что приводит к стиранию перво кодового блока. После обнаружения ошибки или команды запрос в первом кодовом блоке анализатор 5 выдает со своего управляющего выхода блокирующий сигнал, который поступает на второй клапан б, запрещается формирование нового сигнала переспрос в случае поступления во время его действия сигналов ошибка или запрос, и через элемент.9 на управляющий вход первого клапана 3, запрещая прохождение через первый клапан 3 информации из первого накопителя 2. Блокирующий сигнал анализатором 5 подается на время приема п блоков, поступающих после первого искаженного. Информационные блоки с выхода, первого накопителя 2 поступают также в буферный накопитель 12, который обеспечивает хранение (п+1) блоков. При поступлении каждого нового блока содержимое буферного накопителя 12 смещается на один блок, при этом блок, записанный в последне ячейке буферного накопителя 12, стирается. Если анализатор 5 обнаружил в принимаемом кодовом блоке ошибку или команду запрос, то по соответствующему сигналу с анализатора 5 на месте этого кодового блока в буферном накопителе 12 делается пропуск (стирание-) , который отмечается oco6fcJM признаком. По сигналу переспрос с выхода второго клапана б из буферного накопителя 12 производится быстрый вывод хранящихся в нем блоков в порядке их поступления в него, причем выводятся и пропуски (стертые блоки) вместе с отличающим их признаком. После вывода хранящейся в нем информаг ии буферный накопитель 12 освобождается полностью и готов снова к приему информации с выхода первого накопителя 2. Управление выводом информации из буферного накопителя 12 осуществляется не только по сигналам с выхода второго клапана 6, но и по сигналам с выхода элемента 11, обеспечивакидего задержку ВХОДНЕЛХ сигналов на время, равноме длительности приема (п+1) кодовых блоков. Если будет происходить подряд несколько циклов переспроса, то сигналы е выходов второго клапана 6 и элемента 11 будут совпадать во времени (кроме первого сигнала со второго клапана б и последнего - с элемента 11). По сигналам с выхода второго клапана 6 или элемента 11 производится начальная установка и запуск счетчика 13, изменяющего свое состояние на единицу за время приема одного кодового блока. Выход счетчика 13 через элемент 14 подключен к блоку 15, который запоминает состояние счетчика 13 на момент поступления сигнала запрос от анализатора 5 на второй вход элемента 14. Если сигнал переспрос с выхода второго клапана б был вызван сигналом запро то блок 15 зафиксирует состояние сче чика 13, равное нулю. Если сигнал запрос будет выделен анализатором 5 в блоке, следующем вслед за искаженкЕлм кодовым блоком, вызвавшим блокировку устройства, то в блоке 15 зафиксируется состояние счетчика 13, равное единице, и так далее. Таким образом, счетчик 13, элемент 14 и блок 15 определяют и запоминают число кодовых блоков, разделяющих начало блокировки устрой ства и момент выделения сигнала за прос. С блока 15 состояние счетчик 13 вводится через управляющий вход во второй накопитель 8 и определяет число первых информационных блоков, которые можно вводить во второй накопитель В из последовательности блоков, поступающих с выхода буферного накопителя 1,2. Если в блоке 15 хранится нуль, то во второй накопитель 8 не разрешается ввод новы блоков,.если состояние блока 15 соо ветствует, например трем, то во вто рой накопитель 8 разрешается ввод п вых трех информационных блоков (в т числе и стертых), поступающих из бу ферного накопителя 12. В результате повторения информации с -передающей станции по сигналу переспрос во втором накопителе 8 происходит накопление кодовых блоко хотя бы раз принятых без ошибок в процессе первоначальной передачи и последующих повторений. При этом на копление блоков производится лишь в случае приема хотя бы одной команды запрос. Чем больше смещен момент приема команды запрос от начала блокировки, тем больше будет накапливаться блоков во втором накопителе 8 , При приеме в процессе повторения первого кодового блока без ошибки цикл блокировки заканчивается и анализатор 5 снимает сигнал блокировки со входа элемента 9 и со входа второго клапана 6, а так как на других выходах элемента 9 в это время отсутствуют блокировочные сиг налы, то снимается сигнал блокировк с управляющего входа первого клапан 3 и разрешается прохождение информа ции из первого накопителя 2 в приемник 4, Снятие сигнала с выхода эл мента 9 обнаруживается детектором 1 который сигналом со своего .выхода у танавливает.в нулевое состояние бло 15 и включает блок 7. Блок 7 после его включения выполняет -функции управления устройством при переспросе. Сигналом с выхода блока 7изменяется режим работы анализатора 5, который в этом случае осуществляет только анализ принимаемых кодовых блоков на наличие в них ошибок и команды запрос, а блокировку второго и первого клапанов б и 3 в течение времени приема п блоков, следующих за искаженным блоком или блоком с командой запрос, не производит. Если после передачи управления блоку 7 последующий второй кодовый блок принимается без ошибок, то он выводится через первый клапан 3 из первого накопителя 2 в приемник 4, при этом производится также сдвиг на один блок всей информации, хранимой во втором накопителе 8со стиранием выходного блока. Если и последуюиий блок принят без искажений, то осуществляются указанные выше действия по выводу информации и сдвигу второго накопителя 8, которые повторяются до полного освобождения второго накопителя 8 от накопленной информации, в результате чего второй накопитель 8 сигналом со своего выхода выключает блок 7 и передает управление вновь анализатору 5. Если же второй после разблокировки кодовый блок принимается с ошибкой, а во втором накопителе 8 хранится этот блок от предыдущей передачи, блок 7 производит считывание этого блока из второго накопителя 8 на приемник 4 взамен заблокированного сигналом ошибка из первого накопителя 2. Одновременно блок 7 выдает блокирующий сигнал на управляющий вход второго клапана 6, сигнал переспрос не выдается. Если второй кодовый блок принят с ошибкой, а во втором накопителе 8 он отсутствует, блок 7 выключается, передается управление вновь анализатору 5, второй клапан 6 разблокируется, на его выходе формируется сигнал переспрос и производится блокировка вывода информации до правильного приема этого кодового блока. В любом случае после первой попытки приема второго кодового блока (независимо от ее результата) блок 7 производит сдвиг на один блок всей информации во втором накопителе 8 со стиранием выходного блока. Прием третьего, четвертого и последующих кодовых блоков производится аналогично приему второго кодового блока. В предлагаемом устройстве накопление неискаженных кодовых блоков для их вывода в приемник 4 без переспросов и повторной передачи информации производится лишь в интервалы времени от начала блокировки приемника 4 до приема команды запрос, что совместно с обеспечением согласованной работы анализатора 5 и бпока 7 в режиме пересцроса исключает возможность вывода в приемник 4 вместо одних инфо мационных блоков других, а также з мены блока с искаженной-командой запрос на неискаженный информаци ный блок, хранящийся во втором нак пителе 8 и тем самым устраняет зам выпаде 1ия и вставки блоков информа ции, обусловленные применением накопления искаженной информации, и вышает достоверность принимаемой и формации . Формула изобретения Устройство для приема дискретной информации, содержащее объединенные по входу анализатор и декодер, выход которого подключен к пос ледовательно соединенным первому на пителю, первому клапану и приемнику информации, а также второй накопитель и последовательно соединенные блок управления и второй клапан, при этом управляющий выход анализатора подключен к первому входу второго клапана, а выходы ошибка и запрос анализатора подключены к второму и третьему входам второго клапана и первому и второму входам блока управления, второй выход которого подключен к первому управляющему входу второго накопителя, выход которого подключен к выходу п вого клапана, отличающее с я тем, что, с целью повышения достоверности принимаемой информации, введены элемент ИЛИ, детектор разблокировки, элемент задержки и буферный накопитель, а также последовательно соединенные счетчик, элемент И и блок памяти, выход которого подключен к второму управляющему входу второго накопителя, к информационному входу которого подключен выход буферного накопителя, вход которого объединен со входом первого клапана, к управлякнцему входу которого подключен выход элемента ИЛИ и вход детектора разблокировки, выход которого подключен к второму входу блока памяти и к первому дополнительному входу блока управления, к второму дополнительному входу которого подключен второй выход второго накопителя, при этом выход второго клапана подключен ко входу счетчика и первому управляющему входу буферного накопителя непосредственно и через элемент задержки, а к первому, второму, третьему и четвертому входам элемента ИЛИ подключены соответственно управляющий выход, выход ошибка, выход запрос анализатора и, первый выход блока управления, третий выход которого подключен к второму входу анализатора, причем второй вход элемента И, объединенный с вторым управлякхцим входом буферного накопи- . теля, подключен к выходу запрос анализатора, а третий управляющий вход буферного накопителя подключен к выходу ошибка анализатора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2547404/18-09, кл. Н L 1/16, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1977 |

|

SU692106A1 |

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство для приема дискретной информации | 1977 |

|

SU649156A1 |

| Стартстопно-синхронный передатчик | 1979 |

|

SU832762A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Передающее устройство системы с решающей обратной связью | 1979 |

|

SU866764A1 |

| Устройство приема дискретной информации | 1979 |

|

SU866775A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501296A1 |

| Стартстопно-синхронный передатчик | 1976 |

|

SU569045A1 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных с решающей обратной связью | 1971 |

|

SU468381A1 |

Авторы

Даты

1980-08-23—Публикация

1978-10-12—Подача