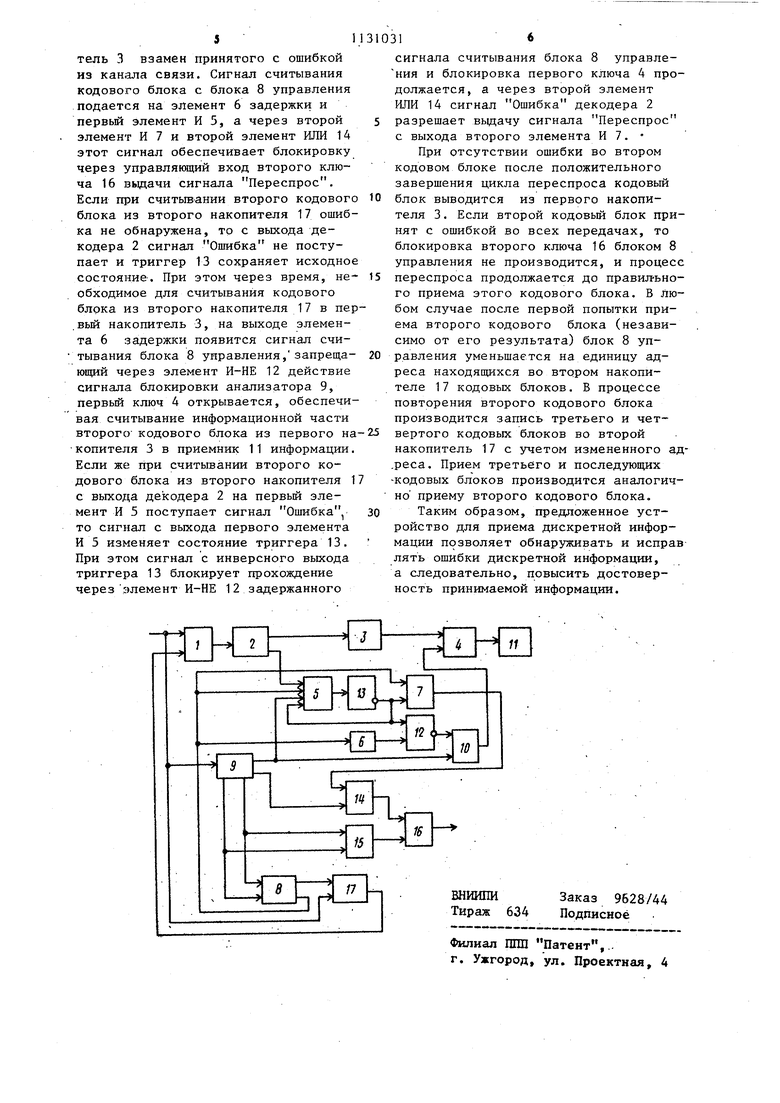

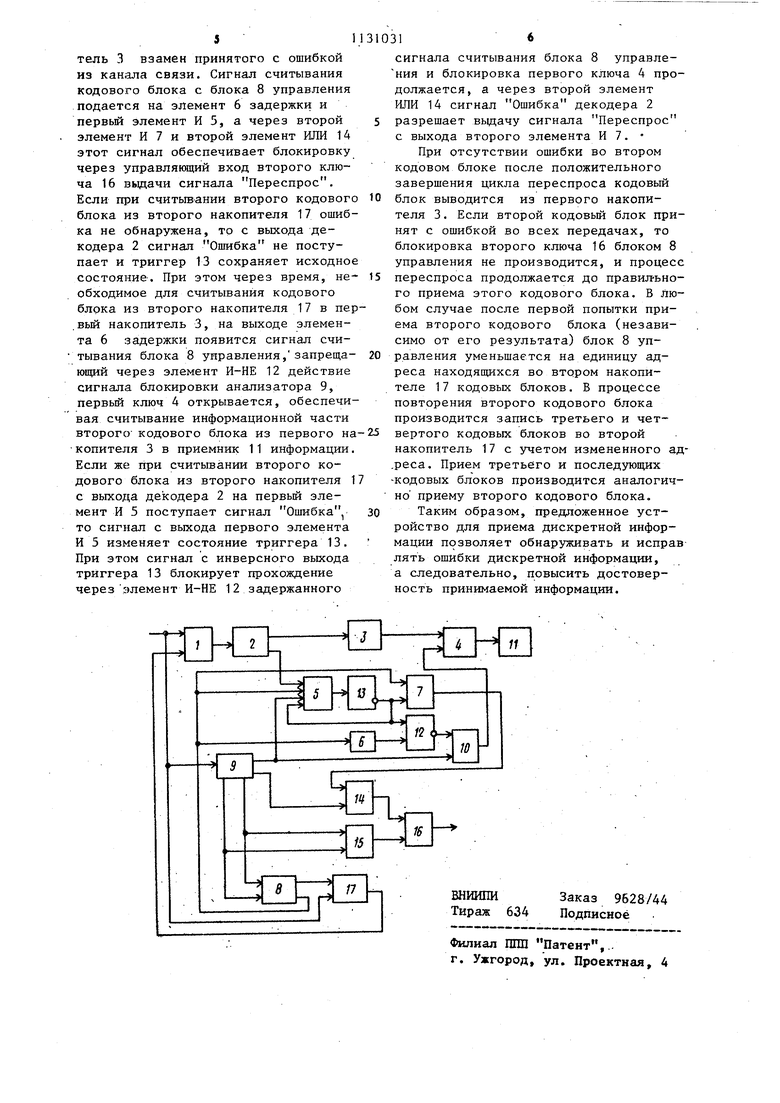

11 Изобретение относится к технике. передачи дискретной информации и может быть использовано при построе нии систем передачи информации с решающей обратной связью. Известно устройство анализа кодовых комбинаций для систем с решающей обратной связью, содержащее блоки обнаружения ошибок, динамические три геры, сдвигающие регистры на К разрядов, предназначенные для хранения комбинаций во время их .проверки в блоке обнаружения ошибок, сдвигающие регистры на К разрядов, предназначенные для хранения комбинаций, забракованных при переспросах, ячейки Запрет, логические эле менты И, инвертор и счетчик числа переспросов, при этом к входу устройства подключены одновременно вход сдвигающего регистра на К разрядов вход блока обнаружения ошибок и вход одного из сдвигающих регистров на k разрядов, причем входы и выходы последних соединены с входами трех логических элементов И, выходы которых подключены к входу второго регистра на к разрядов и второму блоку обнаружения ошибок,- выходы блоков обнаружения ошибок через ячейки памяти подключены к входу логического элемента И и к входу динамических триггеров,выходы которых подключены через ячейки Запрет к выходам сдвигающих регистров на К разрядов, при этом выход одной ячей ки Запрет подключен непосредствен но к информационному входу устройст ва, а другой через логический элемент И на второй вход последней через последовательно соединенные динамический триггер, счетчик числа переспросов и ячейку памяти подан сигнал с другого логического элемен та. И, объединяющий выходы блоков обнаружения ошибок, а к входу устро ства подключен сумматор по модулю два, на второй вход которого поданы сигналы с логических элементов И при этом вьпсод сумматора по модулю два через ячейку Запрет подключен к выходу устройства 1J. Однако данное устройство обладает низкой достоверностью приема информации. Наиболее близким к изобретению техническим решением является устг ройство для приема дискретной инфор мации с решакицей обратной связью. 12 содержащее последовательно соединенные декодер, первый накопитель, первый ключ и приемник информации, анализатор, выходы сигналов Ошибка и Переспрос которого подключены к соответствующим входам . первого элемента ИЛИ и входам блока управления, выход которого подключен к входу записи второго накопителя, а выход сигнала Блокировка анализатора подключен через второй элемент ИЛИ к одному из входов второго ключа, к другому входу которого подключен выход первого элемента Ш1И, причем выход второго ключа является выходом сигнала Переспрос устройства, а выход второго накопителя объединен с выходом первого ключа, первый вход которого объединен со вторым входом второго накопителя, а к управляющему входу первого ключа подсоединен выход анализатораС2. Однако известное устройство для приема дискретной информации обла-. дает низкой достоверностью приема информации. Цель изобретения - повьшгение достоверности приема информации. . Поставленная цель достигается . тем, что в устройство для приема дискретной информации с решающей обратной связью, содержащее последовательно соединенные декодер, первый накопитель, первый ключ и приемник информашш, анализатор, выходы, сигналов Ошибка и Переспрос которого подключены к соответствующим входам первого элемента ИЛИ и входам блока управления, выход которого подключен к входу записи второго накопителя, а выход сигнала Блокировка анализатора подключен через второй элемент ИЛИ к одному из входов второго клича, к другому входу которого подключен выход первого элемента ИЛИ, причем выход второго ключа является выходом сигнала Переспрос устройства, введены дополнительный элемент ШШ, элементы И, элемент И-НЕ, триггер и элемент .задержки, при этом дополнительньй выход декодера через последовательно соединенные первый элемент И, триггер и второй элемент И подключец к другому входу второго элемента ИЛИ,выход триггера подключен к второму входу первого элемента И и через последовательно соединенные элемент И-НЕ и третий элемент И к управляющему входу первого ключа, к третьему входу первого элемента И и к второму входу третьего элемента И подключен выход анализатора, вход которого объединен с входом второго накопителя и с первым входом дополнительного элемента ИЛИ, к второму входу которого подключен выход второго накопителя, а выход дополнительного элемента ИЛИ подключен к входу декодера, и второй выход .блока управления подключен к четвертому входу первого элемента И, ко второму входу второго элемента И и к второму входу элемента И-НЕ чере элемент задержки. На чертеже представлена структурная электрическая схема предлагаемог устройства для приема дискретной информации. Устройство для приема дискретной информации содержит дополнительный элемент ИЛИ 1, декодер 2, первый накопитель 3, первьш.ключ 4, первый элемент И 5, элемент 6 задержки, второй элемент,И 7, блок 8 управлени анализатор 9, третий элемент И 10, приемник 11 информации, элемент И-НЕ 12, триггер 13, первый и второй элементы ИЛИ 14 и 15, второй ключ 16 второй накопитель 17. Устройство для приема дискретной информации работает следующим образо В исходном состоянии триггер 13 установлен в состояние, при котором первый и второй элементы И 5 и 7 и .элемент И-НЕ 12 открыты по соответствующим управляющим входам потенциалом с инверсного выхода триг- гера 13, а потенциалом с одного из в ходов блока 8 управления первый и второй элементы И 5 и 7 заблокированы. При этом первьй элемент И 5 допо нительно блокируется потенциалом с выхода анализатора 9, обеспечивающим через третий элемент И 10 удержание первого ключа 4 в открытом состоянии Сигнал из канала связи поступает на анализатор 9 и через дополнитель ный элемент ИЛИ 1 в декодер 2 и одно временно подается со второй накопитель 17. С выхода декодера 2 информационная часть кодового блока запис вается в первый накопитель 3 в перво начальном коде. Если анализатор 9 не обнаружил ошибку в первом кодовом блоке, разрешается вывод информации из первого накопителя 3 чере первый ключ 4 на приемник 11 инфор114 мадии. В противном случае анализатор 9 вьщает сигнал Ошибка, поступающий на первьй вход блока 8 управления, а через первый элемент ИЛИ 15 и второй ключ 16 на выход сигнала Переспрос. Одновременно из анализатора 9 на первьш и третий элементы И 5. и 10 поступает сигнал, блокирующий первый ключ 4 по его управляющему входу с выхода третьего элемента И 10 и разрешающийработу первого и третьего элементов И 5 и 10. Блокирукяций сигнал действует также и на последующие кодовые блоки. Кодовые блоки, начиная со второго, по сигналам из блока 8 управления и вместе с избыточной частью записываются во второй накопитель 17. При этом адреса записываемых кодовых блоков соответствуют их порядковым номерам. По сигналу Переспрос из канала связи поступает комбинация переспроса в ряд последних кодовых блоков. При поступлении комбинации переспроса анализатор 9 вьщает на .второй вход блока8 управления сигнал Переспрос, прохождение которого через второй ключ 16 блокируется сигналом с выхода второго элемента ИЛИ 14, сформированным анализатором 9, Одновременно продолжается блокировка первого ключа 4, что предотвращает выдачу комбинации переспроса на приемник 11 информации, а сигналы из блока 8 управления, реализующиеiзапись кодовых блоков во второй накопитель 17, не поступают. Если при первом повторении первый кодовый блок вновь принимается с ошибкой, то процесс переспроса повторяется до его приема без ошибки. Одновременно сигналы из блока 8 управления обеспечивают запись во второй накопитель 17 кодовых блоков, следукщих за первым и хранятщихся в последнем как с ошибкой, так и без ошибки без стирания кодовых блоков, принятых после первоначальной передачи и последующих повторений. При приеме в процессе повторения первого кодового блока без ошибки цикл переспроса заканчивается. Если последующий (йторой) кодовый блок принимается с ошибкой, а во втором накопителе 17 этот блок хранится от предыдущей передачи без ошибки, то блок 8 управления производит считывание этого Кодового блока из второго .накопителя 17 через дополнительные элемент ИЛИ 1 и декодер 2 в первв1й накопи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство для приема дискретной информации | 1978 |

|

SU758544A1 |

| Устройство для приема дискретной информации | 1977 |

|

SU692106A1 |

| Устройство для приема дискретной информации | 1977 |

|

SU649156A1 |

| Устройство приема дискретной информации | 1979 |

|

SU866775A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1984 |

|

SU1197114A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501296A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ для систем связи с решающей обратной связью, содержащее последовательно соединенные декодер, первый накопитель, первый ключ и приемник информации, анализатор, выходы сигналов Ошибка и Переспрос которого подключены к сортветствунщим входам первого элемента ИЛИ и входом блока управления, выход которого подключен к входу записи второго накопителя, а выход сигнала блокировка анализатора подключен через второй элемент ИЛИ к одному из входов второго ключа, к другому входу которого подключен выход первого элемента ИЖ, причем выход второго ключа является выходом сигнала Переспрос устройства, о тли чающееся тем, что,, с целью повьш ения достоверности приема информации, в него введены дополнительньй элемент ИЛИ, элементы И, элемент И-НЕ, триггер и элемент за держки, при этом дополнительный выход декодера через последовательно соединенные первый элемент И, триггер и второй элемент И подключен к другому входу второго элемента ИЛИ, выход триггера подключен к второму входу первого элемента И и через последовательно соединенные элемент И-НЕ и третий элемент И к управляющему входу первого ключа, к i третьему входу первого элемента И и к второму входу третьего элемен(Л та И подключен выход анализатора, вход которого объединен с входом второго накопителя и с первым входом дополнительного элемента ИЛИ, к второму входу которого подключен выход второго накопителя, а выход дополнительного элемента ИЛИ подклюсо чен к входу декодера, а второй выход блока управления подключен к четвертому входу йервого элемента И. о со к второму входу второго элемента И и к второму входу элемента И-НЕ через элемент задержки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО АНАЛИЗА КОДОВЫХ КОМБИНАЦИ1 ДЛЯ СИСТЕМ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЬ)1|ПАМШ-ма1-гнд^вО€ООЮЗНАЯ&М&ЙЙОТЕКА | 0 |

|

SU330561A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для приема дискретной информации | 1977 |

|

SU692106A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-12-23—Публикация

1981-06-24—Подача