сл

3150

Изобре-теняе отнстсится к электро- спязи и может быть использовало в системах передачи дискретной информации с решающей обратно связью.

Цель изобретения - иовышение быстродействия ,

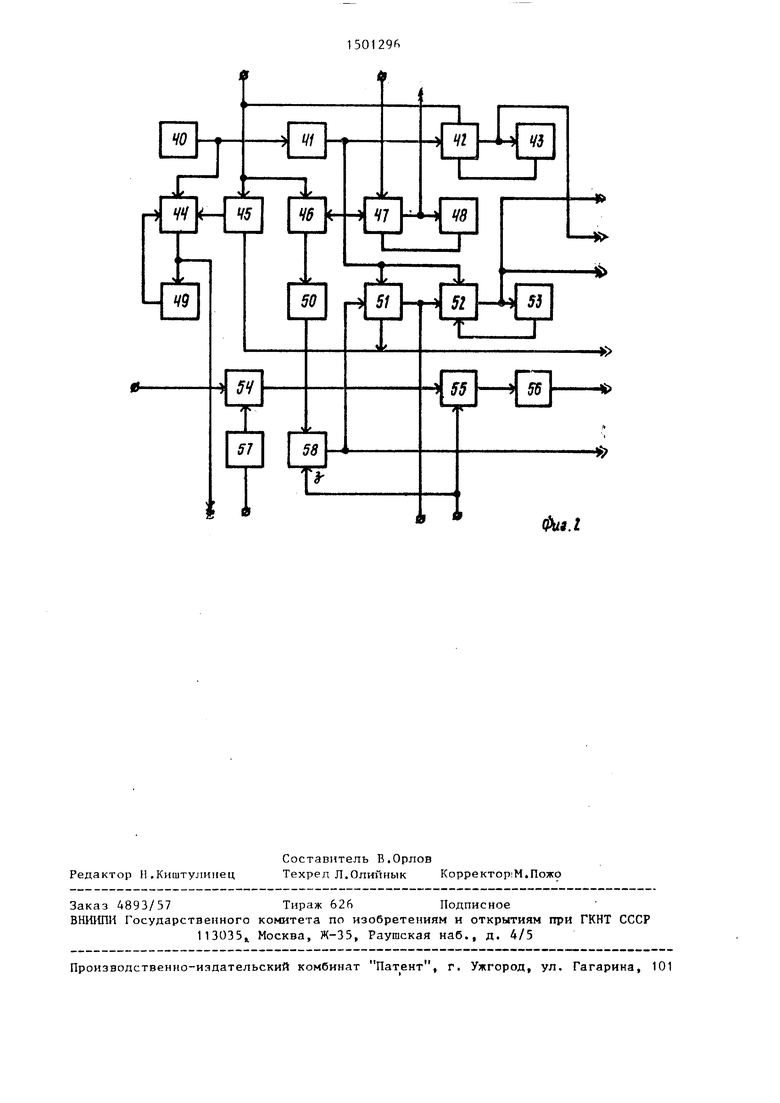

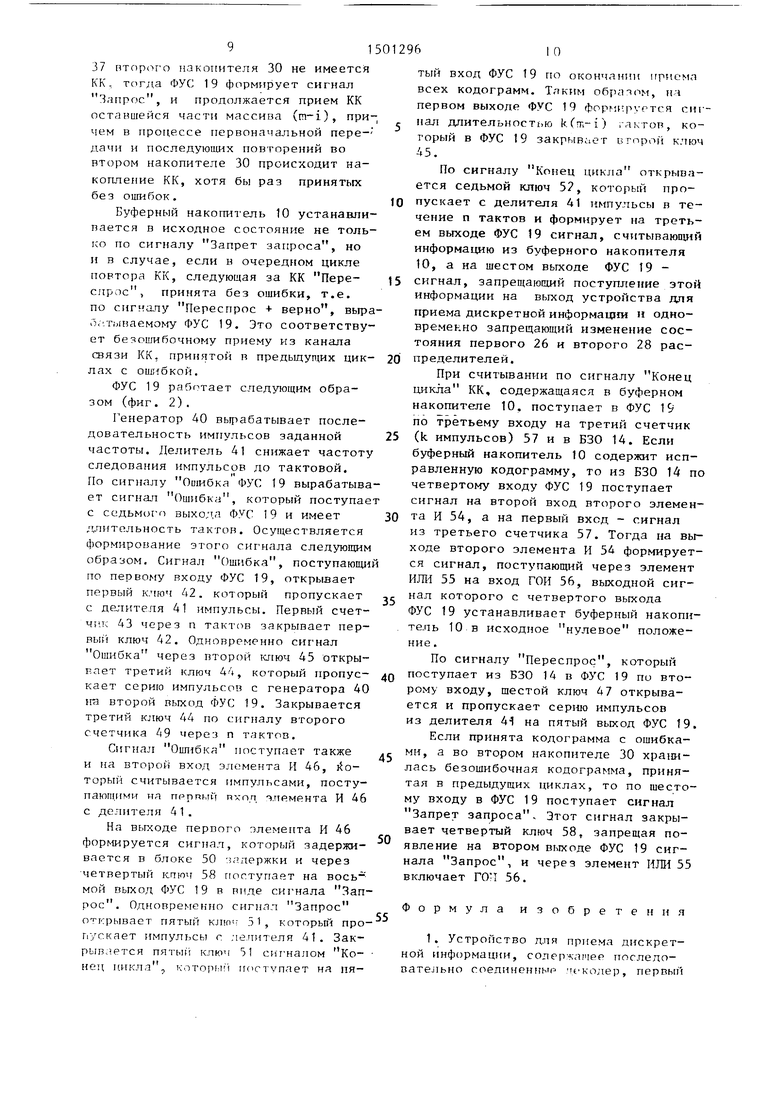

На фиг. 1 представлена структурная электрическая схема устройства для приема дискретной информации; на фиг. 2 - формирователь управляЕощих сигналов,

Устройство для приема дискретной информации содержит первый 1 и второй 2 регистры сдвига, блок 3 контроля канала (БКК), счетчик 4 импульсов, элемент И 5, первый 6 и второй 7 блоки элементов И, второй ключ 8, пятый дополнительный элемент ИЛИ 9, буферный накопитель 10, декодер 11, первый накопитель 12, первый ключ 13, блок 14 защиты от ошибок (БЗО), третий дополнительный элемент ПЛИ 15, второй дополнительный ключ 16, первый дополнительный счетчик 17 им- пульсов, элемент ИЛИ 18, формирователь 19 управляющих сигналов (ФУС), первый дополнительный элемент ИЛИ 20, первый дополнительный ключ 21, второ дополнительный элемент ИЛИ 22, чет- вертый дополнительный элемент ИЛИ 23, третий дополнительный ключ 24. второй дополнительный счетчик 25 импульсов, первый распределитель 26 импульсов, третий блок элементов И 27. второй распределитель 28 пк пульсов, четвертый блок элементов И 29, второй накопитель 30, блок ключей 31 , блок 32 задержки.

блок элементов И 6 содер- жит элементы И 33.

Второй блок элементом И 7 содержи элементы И 34.

Третий блок элементов И 27 содержит элементы И 35.

Четв-гртый блок элементов И 29 со- яержнт элементы И 36.

Второй накопитель 30 содержит регистры 37 сдвига и элемент ИЛИ 38. Блок ключей 31 содержит к:почи 39.

Формирователь 19 управляюимх сиг налов содержит генератор 40 импульсов, делитель 41 частоты, первый ключ 42, первый счетчик 43 импулТ)Сов, третий 44, второй 45 ключи, 1;с рвый элемент И 46, iiiecTovi ключ 47, четвертый счетчик 48, второй счетчик 49 импульсов, блок 50 задержки, пятый ключ 51, седьмой ключ 52, пятьи { ,счет

д

15 20 25 30

т

45

, 50

55

чик 53. гзторой элемент И 54, элемент И.П1 55, генератор 56 одиночных импульсов (ГОИ), третий счетчик 57 им- пульгоп, четвертый ключ 58.

УстроГтстРО для приема дискретной ипфоркшцпи работает следующим образом .

Принимаемые из капала связи входные кодовые комбинации (КК) через пятый дополнительный элемент 1-ШИ 9 пбступают на декодер 11 и БЗО 14 (фиг. 1). С выхода декодера 11 информационная часть КК поступает в первый накопитель 12. БЗО 14 проверяет принятые КК на наличие в них оигибки или команды Переспрос. Если БЗО 14 не обнаружил ни Ошибки, пи команды Переспрос в первой КК, то разре ша- ется вывод инфопмации И первого накопителя 12 через перв)1Й ключ 13 на выход, устрс.Г( таа .-т.ли приема дискретной информаггии. Одчояремепно информационная часть КК через третий дополнительный ключ 24 записывается во второй пакогштель 30.

Запись осутцествляется следующим образом.

В исходном состоянии в первый разряд первого распределителя 26 и второго распределителя 28 записана 1, ко1 орая поступает на соответствующие элеметгты И 36. Если ошибки в КК G jO 14 не обнаружил, то третий до- полнительпый ключ 24 открыт. Через пего КК из парного накопителя 12 поступает на элементы И 36. Однако только с выхода одного элемента И 36, соответствующего в начальный момент первому разряду, на вход со- ответстпующего регистра 37 второго накопителя 30 поступает КК. После окончания записи КК первый дополнительный счетчик 17, сосчитав п импульсов, через второй ключ 16 переписывает 1 из первого разряда второго распределителя 28 во второй разряд. Такой сдвиг 1 первого разряда в второй разряд происходит и в первом распределителе 26 сигналом с первого дополнительного счетчика 17 через второй дополнительный ключ 16, первый дополнительный 1слюч 21 и второй дополнительный элемент ИЛИ 22. Спедующая безошибочная КК записывается в другой соответствующий регистр 37 второго накопителя 30. Если все КК бьши приняты без ошибок, то 1 из последнего разряда

первого распределителя 26 по цепи обратной связи переписывается в первый разряд, а второй накопитель 30 устанавливается в О. Нл соответствующий элемент И 35 с первого разряда первого распределителя 26 и со второго распределителя 28 через блок 32 задержки поступают 1, в результате чего в первый разряд второго распределителя 28 записана 1 Таким образом, второй распределител 28 готов к новой работе, а процесс приема массива, состоящего из m ко- дoгpaм, заканчивается.

В сл учае возникновения ошибки в i-ч КК устройство для приема диск- рс 1 ной информации работает следующи образом,

БЗО 14 выдает на первый вход ФУС 19 и второй вход элемента И 5 сигнал Ошибка. По этому сигналу ФУС 19, начиная с момента выдачи первым накопителем 12 КК, формирует сигнал, по которому элемент ИЛИ 18 закрывает на время п импульсов первый ключ 13 и информация из первого накопителя 12 не поступает на вьгход устройства для приема дискретной информации; закрывает третий дополнительный ключ 24 через четвертый дополнительный элемент 1ШИ 23, поэтому запись КК во второГ; накопитель 30 не производится; закрывает первый дополнительный ключ 21 через первый дополнительный элемент ИЛИ 20, зап- .рещая выдачу считы)ыюше1 о сигнала в первый распределитель 26; открывает соответствующий (i-й) ключ 39 через соответствующий элемент И 36.

По сигналу Оишбка ФУС 19 формирует серию считывающих импульсов, которые через соответствующий (i-й) открытый ключ 39 считывают информаци из соответствующего (i-ro) регистра 37 второго накопителя 30. Если в. i-OM регистре 37 хранилась ранее за- писаннач КК, то она поступает на выход устройства для приема дискретной информации, а второй дополнительный счетчик 25 выдает п ФУС 19 сигнал Запрет запроса и через второй дополнительный элемент ИЛИ 22 - считывающий сигнал, KOTopbii i переписывает 1 из i-ro разряда в ()-й разряд первого распределителя 26. По ст гналу Запрет запроса ФУС 19 формирует сигнал Установка в О, который с четвертого выхоца ФУС 19 пос

10

5012966

тупает на установочный вход буферного накопителя 10. Если при возникновении ошибки в i-й КК в i-OM регистре 27 второго накопитепя 30 безошибочная КК не хранится, то устройстпо для приема ДИСГФРТНОЙ ин .Ьормации )а-- ботает следующиг. обрлчим.

Из-за отсутствия КК в i-ом регистре 37 второго накопителя 30 второй дополнительный 25 сигнал Запрет запроса не выдает и ФУС 19 формирует команду Запрос и формирует сигнал запрета длительностью 15 k(m-i), которым запрещает прохождение информации через первый ключ 23 . и первый дополнительный ключ 21 до окончания приема оставшихся КК.

Таким образом, в первом распреде- 2Q лителе 26 1 хранится в i-oM разряде до конца цикла передачи, а 1 во втором распределителе 28 продолжает продвигаться через каждые п импульсов. Когда 1 достигнет пос- 25 леднего разряда, на выходе переноса второго распределителя 28 возникает сигнал Конец Ц11кла, которьй через блок 32 задержки подается на пятый вход ФУС 19 и на вторые входы элементов И 35. По сигналу Конец цикла 1 из i-ro разряда первого распределителя 26 через соответствующий элемент И 35 записывается в i-й разряд второго распределителя 28.

По сигналу Запрос запрещается списание информации из регистров 37 второго накопителя 30 до прихода команды Переспрос, и второй накопитель 30 работает только на запись КК, принятых без ошибки. В регистры 37 второго накопителя 30, соответствующие номерам кодограмм, принятым с ошибками, информация не записывается .

Буферный накопитель 10 в процессе последующих циклов передачи m-i кодограмм, переданных на выход устройства для приема дискретной информации, исправляет первую ошнбоч 1ую КК. Процесс исправления происходит следующим образом.

Входная КК поступает во второй регистр 2 и в БКК 3, в котором принимается решение об уверенном либо неуверенном приеме элементарного символа КК. В случае уверенного приема в первый регистр 1 записывается 1, в противном случае - О. Счетчик 4 определяет момент заполнения вто30

35

40

45

50

55

рого регистра 2 кодовой и пы;;ает на элемент И 3 сигнал. Если п этот момент на HTopnii вход элемента И 5 поступил п БЗО 14 сигнал Ошибка, то с выхода элемента И 5 через DTOpoi i ключ 8, а на вторые входы второго б;гока элементов И 7 поступает 1, Одновременно по первым входам второго блока элементов И 7 с первого блока элементов И 6 поступают либо единицы, либо нули в зависимости от значения элементарных

и первого

ВУЮ11У1Х разрядах второго 2 1 регистров.

Таким образом, если в одном из разрядов второго регистра 2 содержится элементарный символ 1, а DKK 3 не зафиксировал ошибки в момент его приема, так как в соответствующем разряде первого регистра 1 также находится 1, то в соответст- вую1ццй разряд буферного накопителя 10 записывается если в разряде второго регистра 2 содержится элементарный симво;: О и ошибка не зафиксирована, то в соответствую1дий разряд буферного накопителя 10 записывается если БКК 3 зафиксировал ошибку, т.е. в соответствующем разряде первого регистра 1 записан О, то независимо, какой единичный символ содержится в соответствующем разряде второго регистра 2. в буферном накопителе 10 в этом разряде со держится в процессе приема следующих повторов этой же КК в буферном накопителе 10 осутцествляется исправление ошибочно принятых информационных элементарных символов КК путем записи достоверно принятых 1 в соответствующие разряды буферного накопителя 10.

Так как устро 1ство для приема дискретной информации рассчитано ил. исправление только одной первой ошибочно принятой КК, то прием остальных ошибочн1.: КК в одном цикле передачи блокируется до окончания цикла приема массипа кодограмм сигналом, формируемым ФУС 19.

БлокирующиГ сигнал поступает с первого выхода ФУС 19 на упрап тяющий (запрещающий) вход второго ключа 8 после выдачи команды Запрос с вось мого выхода ФУС 19.

По сигналу Конец цикла ФУС 19 вырабатывает серию (описывающих им

м10

5

20

25

30

35

- 55

40

45

50

ny.iibc:oB, которые поступают в uyipep- иый накопитель 10 и считывают информацию. КК буферного накопителя 10 по цепи обратг1ой связи восстанавливается в регистре буферного накопителя 10. поступает в ФУС 19 и одновременно через пятый дополнительный элемент ИЛИ 9 поступает в БЗО 14, а через декодер 11 - в первый накопитель 12. Прохождение КК из первого накопителя 12 на выход устройства для приема дискретной информации блокируется ФУС 19 по сигналу Конец цикла , Этот же сигнал через третий дополнительный элемент ИШ 15 закрывает второй дополнительный ключ 16, запрещая прохождение считывающего импульса в первый 26 и второй 28 распределители. Ес.п в проверяемой КК D30 14 оишбку не зафиксировал, то КК записывается в соответствующий (i-й) регистр 37 второго накопителя 30. В противном случае КК во вч ором накопителе 30 не записывается.

По сигналу Запрос на информационный вход устройства для приема дискретной информации поступает КК Переспрос и оставшаяся часть передаваемого массива, начиная с i-й кодовой комбинации. БЗО 14 определяет КК Переспрос и выдает на второй иход ФУС 19 соответствующий сигнал, по которому ФУС 19 Формирует запрещающий сигнал и закрывает второй дополнительный ключ 16, первый ютюч 13 и третий дополнительный ключ 24. Затем принимается --я КК, в которой при предыдущих приемах БЗО 14 обнаруживал ошибки. Если в i-й КК при повторном приеме ошибки не обнаружены, то ФУС 19 устанавливает буферный накопитель 10 в исходное состояние, т.е. в О. Если оиибки обнаружены, то в буферном накопителе, 10 проир- ходит дальнейший процесс исправления КК, а ФУС 19 считывает ин4 Орма- цию и:9 соответств асщего (i-ro) регистра 37 второго накопителя 30. Здесь возможны два случая: п i-M регистре 37 второго накопителя 30 имеется КК. тогда информация из i-ro регистра 37 поступает на выход устройства ,гц1я приема дискретной ин- формащш, а второй дополнительный счетчик 25 выдает в ФУС 19 сигнал .Запрет запроса, по которому ФУС 19 устанавливает буферный-накопитель 10 в исходное состояние,- в i-м регистре

91

37 накопителя 30 не имеется КК, тогда ФУС 19 формирует сигнал Запрос, и продолжается прием КК останшейся части массива (m-i), причем в процессе первоначадьной пере- дачи и последующих повторений во втором накопителе 30 происходит накопление КК, хотя бы раз принятых без ошибок.

Буферный накопитель 10 устанавли- пается в исходное состояние не только по сигналу Запрет запроса, но и в случае, если в очередном цикле повтора КК, следующая за КК Переспрос, принята без ошибки, т.е. по сигналу Переспрос - верно, выра ,ъ1ваемому ФУС 19. Это соответствует безошибочному приему из канала связи КК, принятой в предыдущих циклах с ошлбкой.

ФУС 19 работает следующим образом (фиг. 2).

Г енератор 40 вырабатывает последовательность импульсов заданной частоты. Делитель 41 снижает частоту следования импульсов до тактовой. По сигналу Оишбка ФУС 19 вырабатывает сигнал Ошибка, который поступае с седьмого выхода ФУС 19 и имеет ; пительность тактов. Осуществляется формирование этого сигнала следующим образом. Сигнал Ошибка, поступающи по первому входу ФУС 19, открывает первый к.мюч 42. который пропускает с делителя 41 импульсы. Первый счет- чи.к 43 через п тактов закрывает пер- Bbii f ключ 42. Одновременно сигнал Ошибка через второй югюч 45 открывает третий ключ 44, который пропускает серию импульсов с генератора 40 jra второй выход ФУС 19. Закрывается третий ключ 44 по сигналу второго счетчика 49 через п тактов.

Сигнал Ошибка поступает также и на второй вход элемента И 46, йо- торый считывается импульсами, посту- паюгцпми на пррпьгй nxon -элемента И 46 с делителя 41.

На выходе первого элемепта И 46 формируется сигнал, который задерживается в блоке 50 ,лержки и через четвертый кпюч 58 поступает на восьмой выход ФУС 19 в виде сигнала Запрос. Одновременно сигнал Запрос о крывает пятый ключ 51 , который про пускает импульсы с ле.гштеля 41. Зак- рыв;.ется пятый ключ 51 снг налом Ко

.

неп цикла

которы поступает на ня-

10

20

25

1296

30

I О

тый вход ФУС 19 по окончании приема всех кодограмм. Таким образ(1М, нч первом выходе ФУС 19 формируется сигнал длительностью k(m-i) ; чктов, который в ФУС 19 закрывает второй ключ 45.

По сигналу Конец цикла открывается седьмой ключ 5, который пропускает с делителя 41 импульсы в течение п тактов и формирует на третьем выходе ФУС 19 сигнал, считываюпшй информацию из буферного накопителя 10, а на шестом выходе ФУС 19 - 15 сигнал, запрещающий поступление этой информации на выход устройства для приема дискретной информацгт н одновременно запрещающий изменение состояния первого 26 и второго 28 распределителей.

При считывании по сигналу Конец цикла КК, содержащаяся в буферном накопителе 10, поступает в ФУС 19 по третьему входу на третий счетчик (k импульсов) 57 и в БЗО 14. Если буферный накопитель 10 содержит исправленную кодограмму, то из БЗО 14 по четвертому входу ФУС 19 поступает сигнал на второй вход второго элемента И 54, а на первый вход - сигнал из третьего счетчика 57. Тогда на выходе второго элемента И 54 формируется сигнал, поступающий через элемент ИЛИ 55 на вход ГОИ 56, выходной сигнал которого с четвертого выхода ФУС 19 устанавливает буферный накопитель 10 в исходное нулевое положение .

По сигналу Переспрос, который поступает из БЗО 14 в ФУС 19 по второму входу, шестой ключ 47 открывается и пропускает серию импульсов из делителя 41 на пятый выход ФУС 19.

Если принята кодограмма с ошибками, а во втором накопителе 30 хранилась безошибочная кодограмма, принятая в предыдущих циклах, то по шестому входу в ФУС 19 поступает сигнал Запрет запроса. Этот сигнал закрывает четвертый ключ 58, запрещая появление на втором выходе ФУС 19 сигнала Запрос, и через элемент ИЛИ 55 включает 56.

35

0

5

0

.-55

Формула изобретения

1. Устройство для приема дискретной информации, солер:-ь-аг11ее последовательно соединенные Н колер, первый

накопитель и первый ключ, последопа- тельно соединенные блок 3aimiT.i от ошибок, формирователь управлямишх сигналов, элемент ИЛ, выход которог подсоединен к упрапляющему входу первого ключа, последовательно соединенные счетчик импульсов и элемент И, а также буферный накогп1тель, второй накопитель, блок задержки и второй ключ, управляющий вход которого подключен к первому выходу формирователя yпpaвляющ ix сигналов, второй вход которого подключен к второму выходу блока защиты от ошибок, второй вход элемента И подключен к первому выходу блока защиты от ошибок, информационный вход которо го подключен к информационному входу декодера, причем объединенные тактовые входы блока защиты от ошибок, декодера, первого и второго накопителе и объединенные выходы второго накопителя и первого ключа являются соответстненпо тактовым входом и информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия, введены последовательно соединенные блок контроля канала, первый регистр сдвига, первый блок элементов И и BTopoi i блок элементов И, выходы которого подсг еди- нены к соответствующим информационным входам буферного naKonuTejiH, . последовательно соединенною перрь й дополнительный элемент fLTli, порпый дополнительный ключ, второй дополнительный элемент РШИ, первый распределитель импульсов, третий блок элементов И, второй распределитель импульсов, четверть1Й блок элементов И и блок ключей, 1П1формационный вход которого подключен к пторому выходу формирователя управляющих сигналов, последовательно соединенные третий дополнительный элемент ИЛИ и второй дополнительп лй ключ, выход которого подсоедш1е1 к информант онному входу первого дополнительного ключа и тактовому Е .ходу BTopoi o распределителя импульсов, последовательно соединенные четверть й дополнительный элемент ИЛИ и третий дополнительный ключ, информагшонный вход и выхогс которого подк,тночены соответственно к выходу первого накопителя и объединенным вторым входам четвертого блока элементов И, а также второй; регистр сдвига, выходы которого подсое

5

0

5

0

5

0

5

0

5

динены к соответствующим вторым входам первого блока элементов И, пятый дополнителтлгый элемент ИЛИ, выход которого подсоединен к 1П)формадион- ному входу декодера, и псрнь й и второй дополнительные счетчики импуз;ь- сов, входы которых подсоединены со- oTBeTCTBeifHO к выходам первого и второго накопителей, при этом информационный вход блока контроля канала подключен к информационному входу второго регистра сдвига и пepвo y входу пятого дополнительного элемента ИЛИ, второй вход которого объединен с дополнительным ин(1)орма1 щонным входом буферного накопителя п третьим входом формирователя упр.и ;1яюи их сигналов и подключен ; оыходу буферного накопителя. считывяк ;цй и уста- навлииак .ций BXO.IVI кот(фо1-о подключгз- ны соответственно :: 1р(ггт. :му и четвертому выходам форм роват тя управ- сигналов, чптверты вход и пятый выхол которого подключены соответственно к третьему выходу блока защиты от ошибок и объе/тинрнным пер- |Вому входу третьего допол1П1тельного j элемента 1-1ПИ и второму входу элемента гим, второй вход третьего дополни г.гльного элемента ИЛИ объедите: с третьим входом элемента 1УШ и Г1(,ьи л1очен к шестому выходу формироваг ;ля упрпвляш1 ;их сигналов, седьмой гл;гх:о1д которот о подсоединв - к четвертому входу элемента tLRlI, объединенным третьим входам четвертого блока элементов И и первым входам первого и четвертого дополнительных элементов ИЛ, BTopi-ie входы которых 1 одключены к первому выходу формирователя упрагшяющих сигнатюп, выход переноса второго распределителя импульсов через блок задержки подсоединен к объединенным вторым входам третьего блока элементов И и пятому входу формирователя упранляюьчих сигналов, шестой .вход которого объединен с вторым ВХ1ДОМ второго дополнительного элемента ИЛИ и подключен к выходу второго дополнительного I счетчика импульсов, выход переноса первого распределителя импульсов подсоединен к информационному входу первого распределителя импульсов и ycтaнoвbчнo ry входу вта|)ого накопителя, информационные входы котор ого подключены к соответствующим выходам

четвертого блока элементов И, считы13

пающне входы второго накопителя подключены к соответствующим выходам блока ключей, информационный вход и выход первого ключа подключены соответственно к выходу элемента И и объединенным вторым входам второго блока элементов И, тактовые входы первого и второго регистров сдвига подключены к тактовому входу первого накопителя, причем объединенные вход счетчика импульсов и информационный вход блока контроля канала и объединенные установочные входы первого и второго распределителей импульсов являются соответственно информационным и установочным входами устройства.

2. Устройство по п. 1, отличающееся тем, что формирователь управляющих сигналов содержит последовательно соединенные генератор импульсов, делитель частоты, первый ключ и первый счетчик импульсов, выход которого подсоединен к закрывающему входу первого ключа, последовательно соединенные второй и третий ключи и второй счетчик импульсов выход которого подсоединен к закрывающему входу третьего ключа, последовательно соединенные первый элемент И, блок задержки, четвертый и пятый ключи, последовательно соединенные третий счетчик импульсов, второй элемент И, элемент ИЛИ и генератор одиночных импульсов, после- .:довательно соединенные шестой ключ

012961и четвертый счетчик, выход которого подсоединен к закрывающему входу шестого ключа, последовательно соединенные седьмой ключ и пятый счет- о

чик импульсов, выход которого пол-соединен к закрывающему входу седьмого ключа, выход делителя частоты подсоединен к первом входу первого 10 элемента И и информационным входам пятого, шестого и седьмого ключей, закрывающий вход второго ключа подключен к выходу пятого ключа, открывающий вход первого ключа подключен 15 к информационному входу второго ключа и второму входу первого элемента И, причем информационный вход второ

го ключа, открывающий вход шестого ключа, вход третьего счетчика импульсов, второй вход второго элемента И, объединенные закрывающий вход пятпго ключа и открывающий вход седьмого ключа, объединенные закрывакяций вход четвертого ключа и второй вход элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым и шестым входами формирователя управляющих сигналов, а выход пятого ключа, выход второго счетчика импульсов, выход седьмого ключа, выход генератора одиночных импульсов, выход шестого ключа, выход седьмого ключа и выход первого ключа являются соответственно первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами формирователя управляющих сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для приема многократно повторяемых команд | 1984 |

|

SU1226510A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| УСТРОЙСТВО СИНХРОННОГО ПРИЕМА ДВОИЧНОЙ ИНФОРМАЦИИ ПО ДУБЛИРУЮЩИМ КАНАЛАМ СВЯЗИ | 2012 |

|

RU2528089C2 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

Изобретение относится к электросвязи. Цель изобретения - повышение быстродействия. Устройство содержит счетчик 4 им пульсов, эл-т И 5, ключи 8 и 13, буферный накопитель 10, декодер 11, накопители 12 и 30, блок 14 защиты от ошибок, эл-т ИЛИ 18, формирователь 19 управляющих сигналов и блок 32 задержки. Для повышения быстродействия в устройство дополнительно введены регистры 1 и 2 сдвига, блок 3 контроля канала, блоки эл-тов И 6,7,27 и 29, эл-ты ИЛИ 9,15,20,22 и 23, ключи 16, 21 и 24, счетчики 17 и 25 импульсов, распределители 26 и 28 импульсов и блок ключей 31. 1 з.п. ф-лы, 2 ил.

| Устройство контроля состоянияКАНАлА СВязи | 1979 |

|

SU809594A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для приема дискретной информации | 1978 |

|

SU758544A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-08-15—Публикация

1987-05-06—Подача