1

Изобретение относится к связи и может использоваться в приемниках многоканальных модемов с ортогоНсьльными канальными сигналами и двукратной фазоразностной модуляцией .

Известен частотно-фазовый дискриминатор, содержащий два перемножителя, первые входы которых объединены, а выходы - подключены к входам соответствующих интеграторов, первый блок определения знака, вход которого соединен с входом первого инвертора, выход ко-, торого подключен к первому входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого подключен первый вход четвертого перемножителя, второй вход которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и второго перемножителей поданы соответствующие опорные сигналы l .

Однако известный дискриминатор не обеспечивает высокую точность сравнения частот.

Целью изобретения является повышение точности сравнения частот.

Для этого в частотно-фазовый дискриминатор, содержащий два перемножителя, первыевходы которых объединены, а выходы подключены к входам соответствукяцих интеграторов, первый блок определения знака, вход которого соединен с входом первого

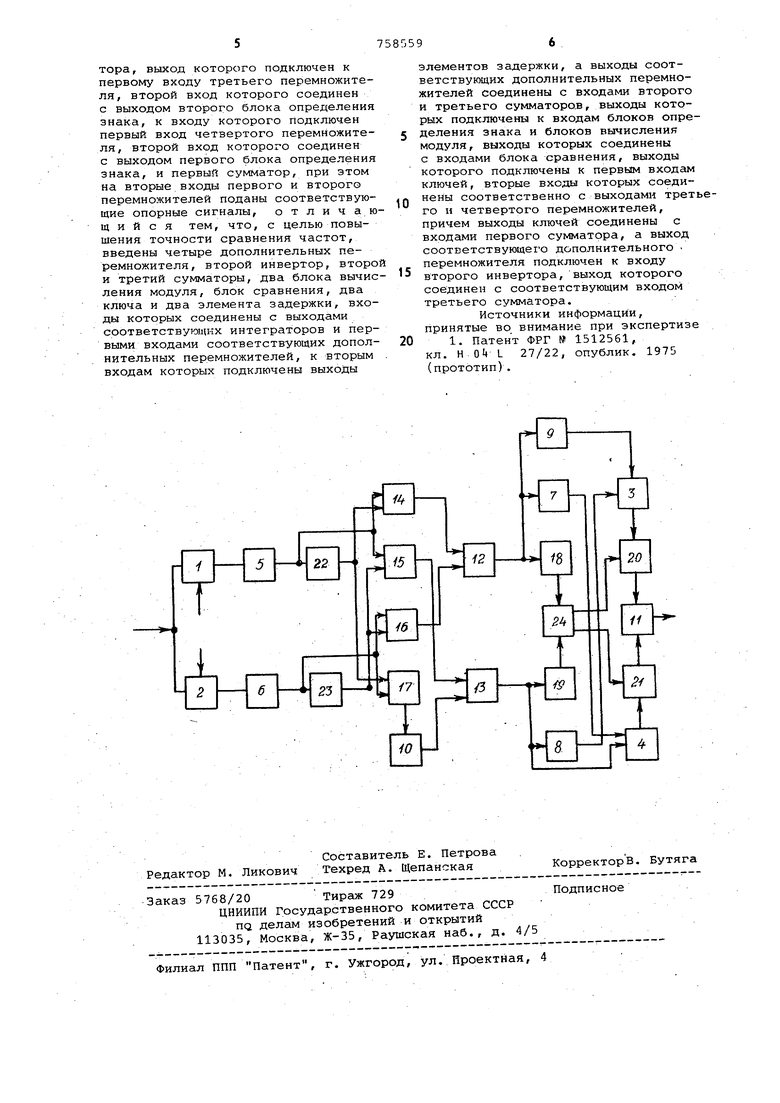

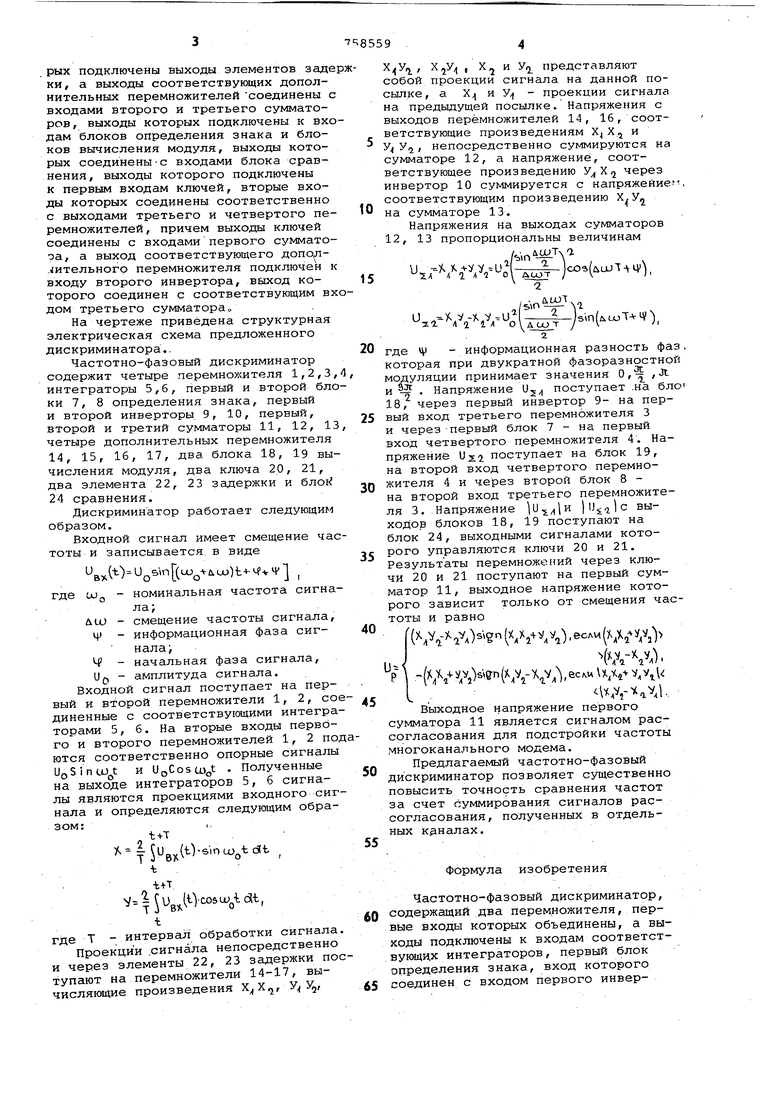

to инвертора, выход которого подключен к первому входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого подклю15чен первый вход четвертого перемножителя, второй вход которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и вто20рого перемножителей поданы соответствующие опорные сигналы, введены четыре дополнительных перемножителя, второй инвертор, второй и третий , сумматоры, два .блока вычисления мо25дуля, блок сравнения, два ключа и два элемента защержки, входы которых соединены с выходами соответст. вующих интеграторов и первьали входами соответствующих дополнительных 30 перемножителей, к вторим входам кото,рых подключены выходы элементов зад ки, а выходы соответствующих дополнительных перемножителей соединены входами второго и третьего сумматоров, выходы которых подключены к вх дам блоков определения знака и блоков вычисления модуля, выходы которых соединены-с входами блока сравнения, выходы которого подключены к первым входам ключей, вторые входы которых соединены соответственно с выходами третьего и четвертого пе ремножителей, причем выходы ключей соединены с входами первого суммато эа, а выход соответствующего допо/iчительногр перемножителя подключен входу второго инвертора, выход которого соединен с соответствующим в дом третьего сумматора На чертеже приведена структурная электрическая схема предложенного дискриминатора.. Частотно-Фазовый дискриминатор содержит четыре перемнохштеля 1,2,3 интеграторы 5,6, первый и второй бл ки 7, 8 определения знака, первый и второй инверторы 9, 10, первый, второй и третий сумматоры 11, 12, 1 четыре дополнительных перемножителя 14, 15, 16, 17, два блока 18, 19 вы числения модуля, два ключа 20, 21, два элемента 22, 23 задержки и бло 24 сравнения. Дискриминатор работает следующим образом. Входной сигнал имеет смещение ча тоты и записывается в виде () , где сОд - номинальная частота сигна ла; ли) - смещение частоты сигнала, Ц) - информационная фаза сигЧ - начальная фаза сигнала. Up - амплитуда сигнала. Входной сигнал поступает на первый и второй перемножители 1, 2, со диненные с соответствующими интегра торами 5, б. На вторые входы первого и второго перемножителей 1, 2 по ются соответственно опорные сигналы UoSinuJpt и UoCoscOot . Полученные на выходе интеграторов 5, б сигналы являются проекциями входного сиг нала и определяются следующим образом:г,,tdt , t .cosLUgtdi, t где Т - интервал обработки сигнала Проекции сигнала непосредственно и через элементы 22, 23 задержки пос тупают на перемножители 14-17, вычисляющие произведения ,, Х и У,З| представляют собой проекций сигнала на данной посылке , а Х и У - проекции сигнала на предыдущей посылке. Напряжения с выходов перёмножителей 14, 16, соответствующие произведениям Х Х, и У У, непосредственно суммируются на сумматоре 12, а напряжение, соответствующее произведению через инвертор 10 суммируется с напряжение соответствующим произведению X,У на сумматоре 13. Напряжения на выходах сумматоров 12, 13 пропорциональны величинам /.,-, . cos(a; 1 IV), .a-Va- V oUuJT (лсх)Т-Аг), где Ч - информационная разность фаз , которая при двукратной фазоразностной модуляции принимает значения 0, ,Л и Щ . Напряжение U поступает .на бло 18, через первый инвертор 9- на первый вход третьего перемнбжителя 3 и через первый блок 7 - на первый вход четвертого перемножителя 4. Напряжение 0-s.Ti поступает на блок 19, на второй вход четвертого перемножителя 4 и через второй блок 8 на второй вход третьего перемножителя 3. Напряжение с выходов блоков 18, 19 поступают на блок 24, выходными сигналами которого управляются ключи 20 и 21. Результаты перемножений через ключи 20 и 21 поступают на первый сумматор 11, выходное напряжение которого зависит только от смещения частоты и равно ()) () -h.- (w. v .v, . ,.. Выходное напряжение первого сумматора 11 является сигналом рассогласования для подстройки частоты многоканального модема. Предлагаемый частотно-фазовый дискриминатор позволяет существенно повысить точность сравнения частот за счет суммирования сигналов рассогласования, полученных в отдельных кдналах. . Формула изобретения Частотно-фазовый дискриминатор, одержащий два перемножителя, перые входы которых объединены, а выходь подключены к входам соответстующи,х интеграторов, первый блок определения знака, вход которого оединен с входом первого инвертора, выход которого подключен к nepBOiviy входу третьего перемножителя, второй вход которого соединен с выходом второго блока определения знака, к входу которого Подключен первый вход четвертого перемножителя, второй вход которого соединен с выходом первого блока определения знака, и первый сумматор, при этом на вторые входы первого и второго перемножителей поданы соответствующие опорные сигналы, отличающийся тем, что, с целью повышения точности сравнения частот, введены четыре дополнительных перемножителя, второй инвертор, второ и третий сумматоры, два блока вычисления модуля, блок сравнения, два ключа и два элемента задержки, входы которых соединены с выходами соответствующих интеграторов и первыми входами соответствующих дополнительных перемножителей, к вторым входам которых подключены выходы

элементов задержки, а выходы соответствующих дополнительных перемножителей соединены с входами второго и третьего сумматоров, выходы которых подключены к входам блоков определения знака и блоков вычисления модуля, выходы которых соединены с входами блока сравнения, выходы которого подключены к первым входгил ключей, вторые входы которых соединены соответственно с выходами третьего н четвертого перемножителей, причем выходы ключей соединены с входами первого сумматора, а выход соответствующего дополнительного перемножителя подключен к входу

5 второго инвертора, выход которого соединен с соответствующим входом третьего сумматора.

Источники информации, принятые во внимание при экспертизе

0

1. Патент ФРГ 1512561, кл. Н 014 L 27/22, опублик. 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство режекции узкополосных помех | 1982 |

|

SU1083369A1 |

| Устройство для некогерентного приема сигналов с относительной фазовой манипуляцией | 1985 |

|

SU1396291A1 |

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| Устройство для детектирования многочастотных сигналов с двукратной относительной фазовой манипуляцией | 1980 |

|

SU921115A2 |

| Демодулятор фазомодулированных сигналов | 1990 |

|

SU1748279A1 |

| Устройство передачи и приема шумоподобных сигналов | 1987 |

|

SU1631737A1 |

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1978 |

|

SU788427A1 |

| Адаптивный восстанавливающий фильтр в дельта-модуляторе с двойным интегрированием | 1990 |

|

SU1795553A1 |

| Частотный дискриминатор | 1977 |

|

SU708503A2 |

Авторы

Даты

1980-08-23—Публикация

1978-07-24—Подача