фигЛ

Изобретение относится к электросвязи и может быть Использовано в системах передачи сигналов с относи- тельной фазовой манипуляцией. .

Цель изобретения - повышение достоверности приема о

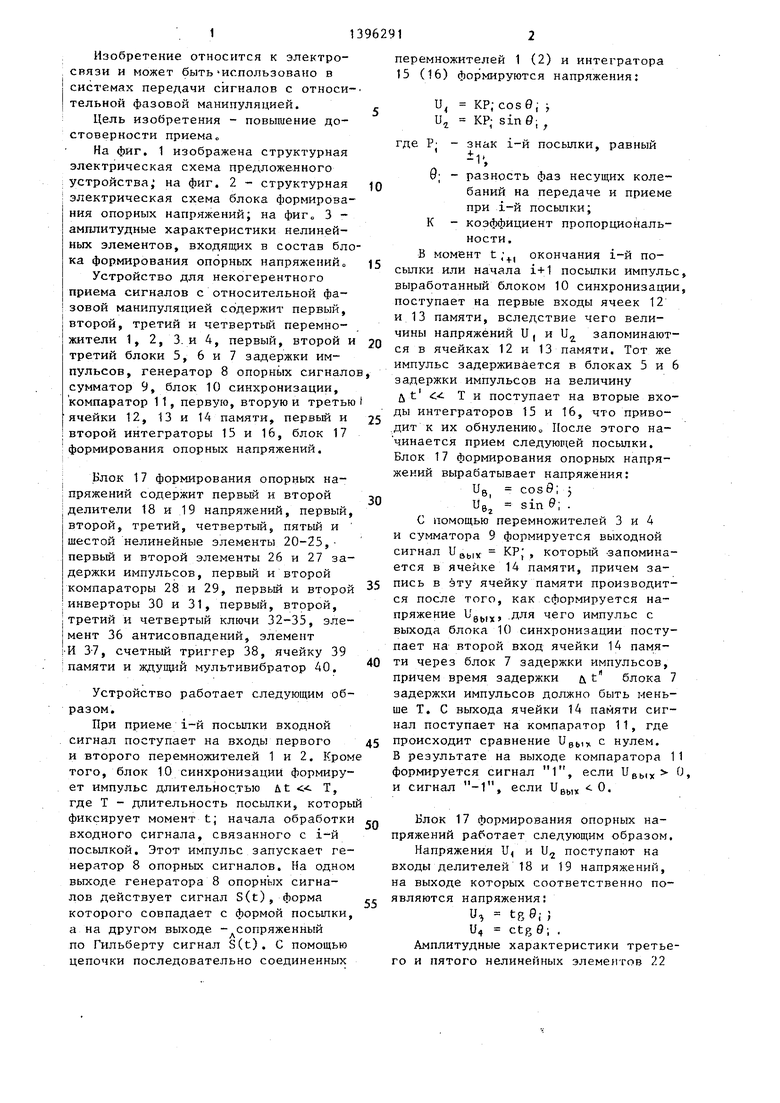

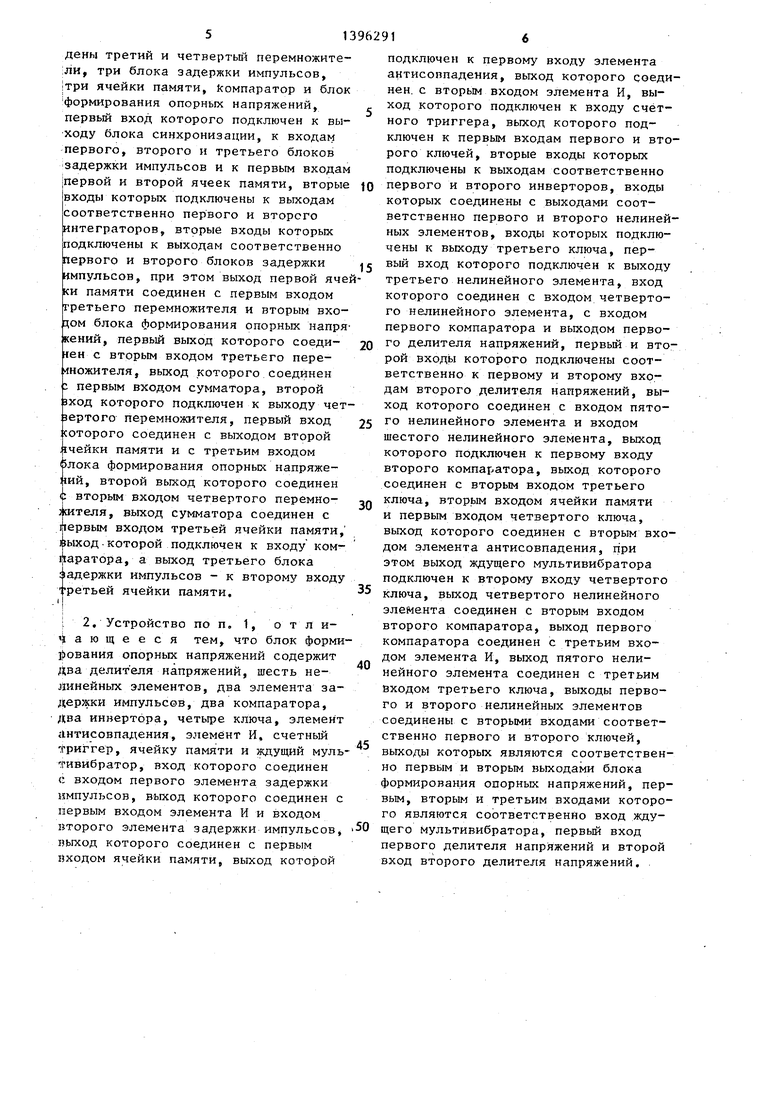

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная Q электрическая схема блока формирования опорных напряжений; на фиго 3 - амплитудные характеристики нелинейных элементов, входящих в состав блока формирования опорных напряжений 15

Устройство для некогерентного приема сигналов с относительной фазовой манипуляцией содержит первый, второй, третий и четвертый перемножители 1, 2, 3. и 4, первый, второй и 20 третий блоки 5, 6 и 7 задержки импульсов, генератор 8 опорных сигналов, сумматор 9, блок 10 синхронизации, компаратор 11, первую, вторую и третью t ячейки 12, 13 и 14 памяти, первый и 25 второй интеграторы 15 и 16, блок 17 формирования опорных напряжений.

Блок 17 формирования опорньгх напряжений содержит первый и второй делители 18 и 19 напряжений, первый, второй, третий, четвертый, пятый и шестой нелинейные элементы 20-25,- первый и второй элементы 26 и 27 задержки импульсов, первый и второй компараторы 28 и 29, первый и второй инверторы 30 и 31, первый, второй, третий и четвертый ключи 32-35, элемент 36 антисовпадений, элемент И 3-7, счетный триггер 38, ячейку 39 памяти и ждущий мультивибратор 40.

Устройство работает следующим образом.

При приеме i-й посьшки входной сигнал поступает на входы первого и второго перемножителей 1 и 2, Кром того, блок 10 синхронизации формирует импульс длительностью t « Т, где Т - длительность посылки, которы фиксирует момент t; начала обработки входного сигнала, связанного с i-й посылкой. Этот импульс запускает генератор 8 опорных сигналов. На одном выходе генератора 8 опорных сигналов действует сигнал S(t), форма

которого совпадает с формой посьшки, а на другом выходе - сопряженный по Гильберту сигнал S(t). С помощью цепочки последовательно соединенных

.

Q 5

0 25

30

5

0

5 п

5

перемножителей 1 (2) и интегратора 15 (16) формируются напряжения:

и KP;cos0; ; и КР; sine-

где PJ - знак i-й посьшки, равный

0; - разность фаз несущих колебаний на передаче и приеме при i-й посьшки; К - коэффициент пропорциональности.

В момент t;, окончания i-й посьшки или начала i+1 посьшки импульс, выработанный блоком 10 синхронизации, поступает на первые входы ячеек 12 и 13 памяти, вследствие чего величины напряжений U , и U, запоминаются в ячейках 12 и 13 памяти. Тот же импульс задерживается в блоках 5 и 6 задержки импульсов на величину U t Т и поступает на вторые входы интеграторов 15 и 16, что приво- ,дит к их обнулению После этого на- Чинается прием следующей посьшки. Блок 17 формирования опорных напряжений вырабатывает напряжения: Ug созб; j UB sin 9; .

С помощью перемножителей 3 и 4 и сумматора 9 формируется выходной сигнал Ugjjiv KPj , который -запоминается в ячейке 14 памяти, причем запись в эту ячейку памяти производится после того, как сформируется напряжение Ь д,, .для чего импульс с выхода блока 10 синхронизации поступает на второй вход ячейки 14 памяти через блок 7 задержки импульсов, причем время задержки и t блока 7 задержки импульсов должно быть меньше Т. С выхода ячейки 14 памяти сигнал поступает на компаратор 11, где происходит сравнение Ug, с нулем. В результате на выходе компаратора 11 формируется сигнал 1, если и сигнал -1, если УВЫХ 0.

Блок 17 формирования опорных напряжений работает следующим образом.

Напряжения U и U; поступают на входы делителей 18 и 19 напряжений, на выходе которых соответственно появляются напряжения; и, tg0; J и ctgQ; .

Амплитудные характеристики третьего и пятого нелинейных элементов 22

и 24 имеют соответственно следующий вид:

и и,

бык

arctg (и,)

.Е,ых arctg (и) .

С помощью четвертого и шестого нелинейных элементов 23 и 25, представляющих собой двухполупериодные выпрямители, и второго компаратора 29 осуществляется сравнение по модулю напряжений Uj и U. Если имеет место неравенство JU.(, то третий ключ 34 пропускает на выход напряжение, выработанное третьим нелинейным элементом 22, а при другом знаке неравенства на выход этого ключа поступает напряжение, выработанное пятым нелинейным элементом 24 Таким образом обеспечивается положение рабочей точки на кривой S, S , Э в пределах отрезка -1, 1 по оси абсцисс (фиг. 3).

Напряжение с выхода третьего ключа 34 поступает на входы первого и второго нелинейных элементов 20 и 21 имеющих соответственно следующие амплитудные характеристики:

вых

ЙЫК

sin(Uex) со5(и„Л

Эти напряжения поступают на входы первого и второго ключей 32- и 33 непосредственно и через первый и второй инверторы 30 и 31, В зависимости от выходного сигнала счетного триггера 38 на выходах блока 17 формирования опорных напряжений появляются весовые напряжения Ug, и U . При приеме 1-й посылки состояние счетного триггера 38 устанавливается произвольным. При приеме следующих посылок состояние счетного, триггера .38 устанавливается следующим образом

Импульс в момент tj с выхода блока 10 синхронизации поступает на вход блока 17 формирования опорных напряжений, вследствие чего запускается ЖДУ1ЦИЙ мультивибратор 40. Импульс с выхода этого мультивибратора длительностью Д t., Т замыкает четвертый ключ 35 и сигнал с выхода второго компаратора 29 поступает на вход элемента 36 антисовпадений. На первый вход элемента 36 антисовпадений поступает сигнал с выхода ячейки 39 памяти, в которой записан выходной сигнал второго компаратора 29, полученный при приеме предыдущей посыпки. На выходе элемента 36 антисовпадений появляется сигнал

1 , в том случае, когда при приеме i-й и i-1-й посьшок результаты сравнения по модулю напряжений Uj и U оказались различными. Первый компаратор 28 сравнивает напряжение Uj с нулем. Если Uj ; О, де появляется сигнал разом на входах элемента И 37 появлято на его выхо- 1. Таким об10 ются сигналы

It ,4 II

I Ч

в случае, если ра

бочая точка оказалась на отрезках S,9 или а , 1 (фиг. 3) .

Первый элемент 26 задержки импуль- сов имеет время задержки it « Л -лм и импульс с его выхода поступает на вход элемента И 37. Если рабочая точка оказалась на отрезках S ,9 или а, I , то на остальных входах элемента И 37 действуют сигналы 1 и на выходе этого элемента появляется импульс, перебрасывающий счетный триггер 38, Учитывая то, что состояние третьего ключа 34 при приеме рассматриваемой посылки изменится по сравнению с состоянием этого ключа при приеме предыдущей посьшки, мы имеем перескок рабочей точки с отрезка 5,3 на отрезок Q , 1 или наоборот с одновременной инверсией напряжений, полученных с помощью первого и второго нелинейных элементов 20 и 21 (фиг. 3).. Второй элемент 27 задержки импульсов обеспечивает запись выходного напряжения второго компаратора 29 в ячейку памяти 39 по окончании описанных процессов, причем время задержки элементом 27 задерж- ки импульсов должно удовлетворять

следующему неравенству:

f . . .С)

гК.М

f + д t

т.

Формула изобретения

1. Устройство для некогерентного 45 приема сигналов с относительной фазовой манипуляцией, содержащее сумматор, блок синхронизации, вход которого подключен к первым входам первого и второго перемножителей, выходы 50 которых соединены с первыми входами соответственно первого и второго интеграторов, при этом выход блока синхронизации соединен с входом генератора опорных сигналов, первый и вто- 55 рой выходы которого соединены с вторыми входами соответственно, первого и второго перемрожителей, отличающееся тем, что, с целью повышения достоверности приема, введены третий и четвертьш перемножите- :ЛИ, три блока задержки импульсов, |три ячейки памяти, Компаратор и блок сформирования опорных напряжений, первый вход которого подключен к выходу блока синхронизации, к входам первого, второго и третьего блоков задержки импульсов и к первым входам первой и второй ячеек памяти, вторые входы которых подключены к выходам соответственно первого и второго интеграторов, вторые входы которых подключены к выходам соответственно первого и второго блоков задержки «мпульсов, при этом выход первой ячеки памяти соединен с первым входом третьего перемножителя и вторым входом блока формирования опорных напря кений, первьй выход которого соеди- лен с вторым входом третьего пере- ножителя, выход которого соединен : первым входом сумматора, второй зход которого подключен к выходу чет зертого перемножителя, первый вход :соторого соединен с выходом второй лчейки памяти и с третьим входом ()лока формирования опорных напряжений, второй выход которого соединен вторым входом четвертого перемно- }Ытеля, выход сумматора соединен с рервым входом третьей ячейки памяти, ыход-которой подключен к входу ком паратора, а выход третьего блока ;)адержки импульсов - к второму входу третьей ячейки памяти,

L 2, Устройство по п, 1, о т л и- ающееся тем, что блок форми |)ования опорных напряжений содержит два делит еля напряжений, шесть нелинейных элементов, два элемента задержки импульсов, два компаратора, два инвертора, четьфе ключа, элемент антисовпадения, элемент И, счетный триггер, ячейку памяти и ждущий мультивибратор, вход которого соединен с входом первого элемента задержки импульсов, выход которого соединен с первым входом элемента И и входом второго элемента задержки импульсов ньгход которого соединен с первым входом ячейки памяти, выход которой

j- O с 05 Q

0

0

5

подключен к первому входу элемента антисоппадения, выход которого соединен, с вторым входом элемента И, выход которого подключен к входу счётного триггера, выход которого подключен к первым входам первого и второго ключей, вторые входы которых подключены к выходам соответственно первого и второго инверторов, входы которых соединены с выходами соответственно первого и второго нелинейных элементов, входы которых подключены к выходу третьего ключа, первый вход которого подключен к выходу третьего нелинейного элемента, вход которого соединен с входом четвертого нелинейного элемента, с входом первого компаратора и выходом первого делителя напряжений, первьй и второй входы которого подключены соответственно к первому и второму входам второго делителя напряжений, выход которого соединен с входом пятого нелинейного элемента и входом шестого нелинейного элемента, выход которого подключен к первому входу второго компаратора, выход которого соединен с вторым входом третьего ключа, вторым входом ячейки памяти и первым входом четвертого ключа, выход которого соединен с вторым входом элемента антисовпадения, при этом выход ждущего мультивибратора подключен к второму входу четвертого ключа, выход четвертого нелинейного элемента соединен с вторым входом второго компаратора, выход первого компаратора соединен с третьим входом элемента И, выход пятого нелинейного элемента соединен с третьим входом третьего ключа, выходы первого и второго нелинейных элементов соединены с вторыми входами соответственно первого и второго ключей, выходы которых являются соответственно первым и вторым выходами блока формирования опорных напряжений, первым, вторым и третьим входами которого являются соответственно вход ждущего мультивибратора, первьш вход первого делителя напряжений и второй вход второго делителя напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Корреляционный демодулятор сигналов с угловой модуляцией | 1983 |

|

SU1166338A1 |

| Частотный дискриминатор | 1986 |

|

SU1359899A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| СПОСОБ И УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ЛИНИЯМ РАСПРЕДЕЛИТЕЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ ПЕРЕМЕННОГО ТОКА | 2006 |

|

RU2338317C2 |

| Частотный дискриминатор | 1977 |

|

SU708503A2 |

| Многоканальный приемник с кодовым разделением каналов для приема квадратурно-модулированных сигналов повышенной структурной скрытности | 2016 |

|

RU2610836C1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

Изобретение относится к электросвязи и позволяет повысить достоверность приема. Устр-во содержит перемножители 1-4, блоки 3-7 задержки импульсов, генератор 8 опорных сигналов, сумматор 9, блок 10 синхронизации, компаратор 11, ячейки памяти (ЯП) 12-14, интеграторы 13,16 и блок 17 формирования опорных напряжений. Генератор 8 на одном выходе формирует сигнал S(t), форма которого совпадает с формой посылки, а на другом выходе - сопряженный по Гильберту сигнал S(t). По сигналу блока 10 сигналы, сформированные из входного сигнала с помощью перемножителей 1, 2и интеграторов 15,16, запоминаются в соотв. ЯП 12, 13. По следующему сигналу блока 10 интеграторы 15, 16 обнуляются. Перемножители 3, 4 умножают запомненные в соотв. ячейках значения на опорные сигналы, сформированные блоком 17. Сумматор 9 формирует выходной сигнал U, который запоминается в ЯП 14. Компаратор 11 формирует сигнал 1, если Ug,, О, и сигнал -1, если Ug -i 0. Поясняется работа блока 17. 1 з.п. ф-лы, 3ил. (Л С

| Борисов Ю.П | |||

| и др | |||

| Основы многоканальной передачи информации, М.: Связь, 1967, с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

Авторы

Даты

1988-05-15—Публикация

1985-08-13—Подача