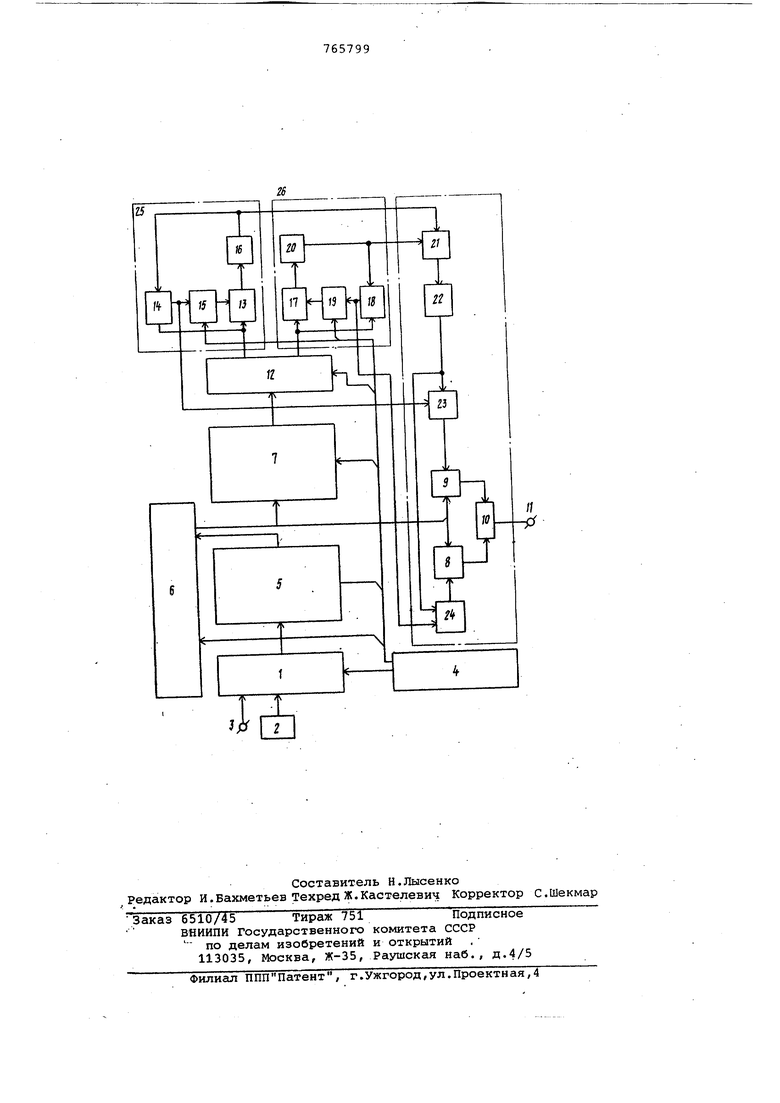

Изобретение относится к автоматизированным информационно-измерительным устройствам и может быть использовано в автоматических системах предварительной обработки информации от первичных преобразователей, а также Б телеметрических устройствах где требуется с.окращение избыточности передаваемых сообщений. Известно устройство 1 кусочно-линейной аппроксимации для сжатия данных, содер жащее ячейки памяти, арифметические блоки, ключи, блок управления, согласно которому измеряемые выборки, находящиеся в пределах полосы допуска, установленной относительно предБщущей существенной ординаты, как избыточные не передаются, а любая выборка, попаданляая на границу допуска или за его пределы передается как неизбыточная и фиксируется в качестве новой опорной величины. Основным недостатком известного устройства является малая степень сжатия для участков с большой крути ной и сравнительная сложность реали зации. Наиболее близким по технической сущности к предлагаемому является устройство для автоматической кусочно-линейной аппроксимации, содержащее задатчики отклонения, выходы которого подключены к соответствующим первым входам коммутатора, первый выход блока управления соединен со вторым входом коммутатора, выход которого подключен к первому входу арифметического блока, выход арифметического блока соединен с первым входом блока памяти, выход которого соединен с первыми входами делителя, первого и второго ключей, выход делителя подключен к первому входу блока сопряжения, второй выход блока управления соединен со вторыми входа-, ми блока памяти, арифметического блока, делителя и блока сопряжения, выходы первого и второго злёментов И подключены соответственно ко вторые входам первого и второго ключей, выходы которых соединены со входами элемента ИЛИ, выход элемента ИЛИ подключен к выходу устройства 2. Недостатком известного устройства является низкое быстродействие. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройстве введены сумматор, нуль-орган, первый и второй бло ки анализа, каждый из которьох выполнен на элементе памяти, элементе И, ключе записи и элементе сравнения, выход которого подключен к первому , входу элемента И, выход элемента И соединен с первым входом ключа записи, вькод которого подключен ко вход элемента памяти, выход элемента памяти соединен с первым входом элемента сравнения, выходы блока сопряжения подключены ко вторым входам элементов сравнения и ключа записи соответствующих блоков анализа, второй выход блока управления соединен со вторыми входами элементов И в бло ,ках анализа, выходы первого и второго элементов сравнения блоков анализа подключены к первым входам соот ветственно первого и второго элементов И, вторые входы которых соединены с выходом нуль-органа, выходы элементов памяти блоков анализа соединены с соответствующими входами сумматора, выход которого подключен ко входу нуль-органа. На чертеже показана схема устройства. Устройство содержит коммутатор 1, эадатчики.отклонения 2, вход коммута тора 3, блок управления 4, арифметический блок 5, блокпамяти б, делитель 7, первый и второй ключи 8 и 9, элемент ИЛИ 10, выход устройства 11, блок сопряжения 12, ключ записи 13, элемент сравнения 14, элемент И 15, элемент памяти 16, ключ записи 17-, элемент сравнения 18, элемент И 19, элемент памяти 20, сумматор 21, нуль орган -22, элементы И 23 и 24, первый и второй блоки анализа 25 и 26. Устройство работает следующим образом. Устройство работает следующим образом. Отфильтрованный от помех полезный сигнал подается на клеммы 3 коммутатора 1, управляемого блоком . управления 4. Посредством задатчика допустимого отклонения ординаты 2 задается величина отклонения, например в пределах 1+5% от максимального возможного значения уровня входного сигнала. Koм Iyтaтop 1 по очереди вводит выборки сигнала и сигнала с задатчика 2 в арифметический блок 5, где происходит центрирование исХОДН9ГО сигнала V4i Vi-Vc,, где у . - центрированное значение выборки сигнала на г -ом Vi исходная выборка сигнал X. - предшествующее существенное значение ординат После центрирования происходит уммирование последующих выборок . V tcf, V. V . сГ JU-l. Linin JUt: tmax ч -максимальное значение де : выборок сигнала , -минимальное значение выборок сигнала; -величина (апертура) допустимого отклонения ординаты. Полученные значения заносятся в устройство памяти верхнего и нижнего допустимых значений, откуда поступают в делитель 7, где и происходит деление на временной интервал от момента центриро:еания до соответствующих моментов времени выборок V.--.d .М.. . max &,-i т.е. определяют угол наклона аппроксимирующих прямых, соединяющих ординаты в момент времени, в который проведено центрирование с последующими центрированными выборками; в пределах допуска ±Б, При последующих операциях деления разность мейоду будет уменьшаться. При последующих выборках запоминается в устройстве памяти 16 только в тех случаях, когда он становится меньше предыду1иего,а запоминается в элементе памяти 20 только в тех случаях, когда он становится больше предыдущего. При таких ограничениях возникает ситуация, когдаigU, (Jgto(.,n,-f,, т.е. аппроксимирующие прямые, взятые по допускам, стремятся сойтись, и когда они сойдутся, необходимо фиксировать существанное значение ординаты. Это определяется сумматором 21. Равенство значений гтюк или превышение , над фиксируется нуль-органом 22, выходной сигнал которого поступает на элементы И 23 и 24, на вторые входы которых поступают сигналы с элементов сравнения 14 или-18, и в этом случае открываются ключи 8, выводя на выход 11 через элемент ИЛИ 10 существенное значение Vl-i-cf или через ключ 9, открываемый элементом И 23 при поступлении на его второй вход сигнала с элемента сравнения 18 существенное значение Vi, из блока памяти 6. Вывод или определяется знаком кривизны функции, но во всех случаях при минимальном значении между tgf trroix и Ключи 13 и 17 открываются, и записывается значение и tgi tnifi в элемента} памяти соответственно 16 и 20 при совпадении сигналов на элементах И 15 и 19 только в том слу|Чае, если содержимое в элементе паМ.ЯТИ 16 по величину больше наченкя поступающего на вход ключа ключа 13, что определяется эле.ментом сравнения 14 и аналогично, новое значение .. записывается в элементе памяти 20, если это эначенке больше чем предшестзуквдее зкс1чение, ранее занесенное в элемент памяти 20 т,е блоки 15 и 26 выполняют роль обратных клапанов, обеспечивающих обновление информации в элементе памяти 16 и 20 только в одностороннем изменении, т.е. соответстзенно в эл менте памяти 16 при уменьшения, а в элементе 20 при увеличении численных значений igfcA при таком ограничении возникает неизбежно ситуация, когда на выходе устройства формируется сигнал вывода существенной ординаты. Блок {сопряжения осуществляет сог ласование уровней и форм сигналов и делителя с БЫ.ХОДОМ блоков 25 к 26. Управление функционированием блоков и узлов ос 1дествляется блоком управ ления 4, который формирует управляю щие сигналы и определяет порядок и очередность работы. Блок управления 4, арифметический блок 5, делитель 7 и блок памяти 6 реализу}этся ка базе кжкропроцессо ра, а блоки 25 и 26 на отдельных интегральных схемах. Такое комбиниро ванное выполнение позволяет сохранит высокое быстродействие микропроцессору, что имеет существенное значени при обработке большого количества информации. Предлагаемое устройство южнo использовать в многоканальной системе сбора телеметрической информации, оно проще, оно не содержит дорогостоящих и сложных цифроаналоговык, и аналого-цифровых преобразователей, гибридный делитель/ элементы, преобразующие временные импульсы в цифровой код. Формула изобретения Устройство для кусочно-линейной аппроксимации, содержшдее задатчики отклонения, выходы которых подключены к соответств тощим первым входам коммутатора, первый выход рлока управления соединен со вторым входом кo мyтaтopa, выход которого подрслючен к первому входу арифметического блока, выход арифметического блока соединен с первым входом блока памяти, выход которого соединен с первьгми входам-г делителя,- первого и второго ключей, выход делителя подключен к первому входу блока сопряжения, второй выход блока управления соединен со вторы fи входами блока памяти, арифметического блока, делителя и блока сопряжения, зькоды первого и второго элементов И подключены соответственно ко вторым входам первого и вторюго ключей, ВЫХОДЫ которых соединены со входами элемента ИЛИ, выход эле-. Мента ИЛИ подключен к выходу устройства, о т л и ч а .ю-щ.е е с я тем, что, с целью гговышер1ия быстродействия устройства, в него введены сумматор, нуль-орган, первый и второй блоки анализа, каждый из- которых выполнен на элементе памяти, элемен-те н. ключе записи и элементе сравнения, выход которого подключен к первоNry входу элемента И, выход элемента if соединен с первым входом ключа записи, выход которого подключен ко входу элемента палштк, выход элемента памяти соединен с первым БХОДОМ элеГЖНта сравнения, -выходы блока сопряжения полключены ко вторым входам элементов сравкения и ключей записи соохветствую;дих блоков aHajiHsa, второй блока управления соединен со вторыми входами элементов И в. блоках анализа, выходы первого н второго элементов сравнения блоков анализа подключены к первым входам соответственно первого н второго элементов и, вторые входы которых соединеньт с выходом куль-органа, выходы элементов nsti-mtK блоков анализа соеинены с соответствукнцимй входами сумгзатора, выход которого подключен ко входу нуль-органа. Источники информации г принятые во внимак1 е при экспертизе 1. Pv ocesdin s of the IEEE том 55. № 3, март 1967,.стр. 10-14. 2.Патент США №.3311909, кл. 340-345,- 05„08.64 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА | 1991 |

|

RU2031375C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Устройство для сокращения избыточности информации | 1975 |

|

SU523438A1 |

| Устройство для временного сжатия входного сигнала | 1982 |

|

SU1100632A1 |

| Адаптивный коррелометр | 1977 |

|

SU732887A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Устройство для вычисления дискретного спектра действительного временного ряда | 1974 |

|

SU525960A1 |

Авторы

Даты

1980-09-23—Публикация

1978-09-18—Подача