1

Изобретение относится к вычисли тельной технике и предназначено для взаимнокорреляцириной обработки эхо-, сигналов.

Измерение взаимной корреляционной функции (ВКФ) между входным и опорным сигналами в реальном масштабе времени требует обработки всего массива N выборок (определяемого длительностью сигнала и точностньми пара метрами измерения) за время меж, двумя соседними выборками, поступающими на вход коррелятора.

Известен цифровой коррелятор, содержащий два аналого-цифровых преобразователя, два усредняющих и цеитриг рующих устройства, формирователь задержки, арифметический блок АБ, устройство управления и синхронизатор. Коррелятор обеспечивает последовательное вычисление ординат ВКФ по приращениям, причем.время, необходи- . мое на вычисление ВКФ, сокращается в

-32 раза по сравнению с традиционным последовательным вычислением ординат lj.

Данный коррелятор обладает существенньми недостатками - увеличивает погрешность вычисления ординат ВКФ и требует быстродействующих блоков памяти.

Наиболее близким по технической

to сущности и схемному решению к предлагаемому является цифровой коррелятор, содержащий два блока памяти с произвольной выборкой, адресный счетчик, соединенный с адресными входами бло15ков памяти, тактовое устройство, соединенное выходами с блоками памяти и адресным сметчиком и АБ, соединенный входами с выходами блоков памяти. При работе коррелятора цифровые

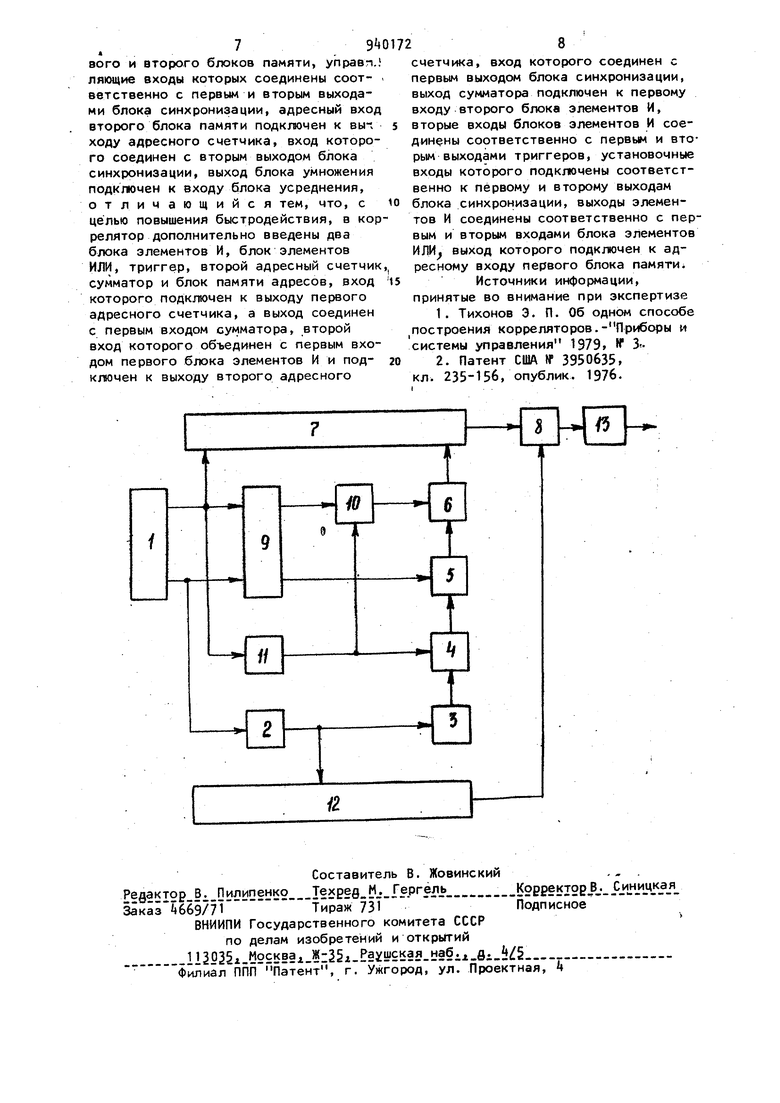

20 выборки входного сигнала последовательно поступают в блок памяти, где хранятся N текущих значений выборок входного. сигна.па, в другой блок памяти последовательно поступают N цифровых выборок опорного сигнала (запись опорных выборок обычно осуществляется в момент излучения зондирующего сигнала). Вычисление ординаты ВКФ между входньи и опорным сигналами осуществляется путем полного опроса памяти обоих блоков памяти,последо вательного образования N пар выбором за время между двумя соседними выборками входного сигнала. Дальнейшее вычисление ВКФ в АБ производится традиционными методами перемножения выбо рок, составляющих пары, и усреднения результатов умножения. Очередная вход мая выборка, поступающая в блок памяти, стирает самую старую по времени прихода в блок выборку и цикл вычисления очередной орди.наты ВКФ повто ряется. Адресный счетчик последоваг тельно формирует адреса обращения к N ячейкам памяти каждого блока памяти. Тактовое устройство обеспечивает; управление операциями во времени.При вычислении ординаты ВКФ используются равномерно расположенные по длине интервала суммирования (длительность зондирующего сигнала) дискретные значения сигнала. Интервал между данными выборками определяется исходя их поло сы сигнала и точности вычисления ВКФ, т.е. выбирается степень коррелированности выборок (2 1 Однако в ряде случаев, например, для сигнала с линейной частотой модуляцией (ЛЧМ) или гиперболической частотной модуляцией (ГЧМ) степень корре лированное ти между равномерно расположенными выборками будет неодинаков вой. Низкочастотные участки сигнала будут представлены выборками, степень корреляции которых во много раз может превосходить расчетную, выбранную исходя из верхней граничной частоты сигнала.Известно, что увеличение степени корреляции между выборками только до определенной величины дает выигрыш в точности вычисления, а дальнейшее увеличение корреляции приводит лишь к избыточности. Для сигнала, например широкополосного сигнала с ГЧМ, у которого низкочастотное заполнение составляет 85-90 длительности всего сигнала, избыточность числа выборок может достигать -больших значений. Цель изобретения - повышение быстродействия коррелятора при практически неизменной точности вычисления. Поставленная цель достигается тем, что в цифровой коррелятор, содержащий блок умножения, входы которого подключены соответственно к выходам первого и второго блоков памяти, управляющие входы которых соединены соответственно с первым .и вторым выходами блока синхронизации, адресный вход второго блока памяти подключен к выходу адресного счетчика, вход которого соединен с вторым выходом блока синхронизации, выход блока умножения подключен к входу блока усреднения, дополнительно введены два блока элементов И, блок элементов ИЛИ, триггер, второй адресный счетчик, сумматор и блок памяти адресов, вход которого подключен к выходу первого адресного счетчика, а выход соединен с первым входом сумматора, второй вход которого соединен с первым входом первого блока элементов И и подключен к выходу второго адресного счетчика ,вход которого соединен с первым выходом блока синхронизации,выход сумматора подключен к первому входу второго блока элементов И, вторые входы блоков элементов И соединены соответственно с первым и вторым выходами триггера, установочные входы которого подключены соответственно к первому и второму выходам блока синхронизации выходы элементов И соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого подключен к адресному входу первого блока памяти. Сущность изобретения зактючается в том, что при вычислении ординаты ВКФ используются выборки с одинаковой степенью корреляции между собой, т.е. интервал между ними определяется не верхней граничной частотой сигнала (максимальная частота заполнения), а частотой, соответствующей данному участку опорного детерминированного сигнала, что позволяет устранить, избыточность количества выборок, участвующих в процессе вычисления ординаты ВКФ, и, как следствие этого, увеличить быстродействие коррелятора. На чертеже изображен цифровой коррелятор. Коррелятор содержит последовательно соединенные блок 1 синхронизации, адресный счетчик 2, блок 3 памяти адресов (БПА), сумматор k, первый блок 5 элементов И, блок 6 элементов ИЛИ, первый блок 7 памяти и блок 8 умножения, триггер Э, прямым выходом подключенный через блок 0 элементов И к вторым входам блока 6 элементов ИЛИ, инверсным выходом подключенный к вторым входам первого блока 5 элементов И, адресный счетчик 11, входом подключенный с первьм установочным входом триггера 9, с управляющим входом первого блока 7 памяти и с вторым выходом блока 1 синхронизации, выходы адресного счетчика 11 подключены к вторым входам второго блока 10 элементов И и сумматора , второй установочный вход триггера Э подключен к входу первого счетчика 2 и к управляющему входу второго блока 12 памяти, адресные входы которого подключены к выходам первого адресного счетчика 2, а выход - к второму входу блока 8 умножения, выход которого соединен с входом блока 13 усреднения.

Цифровой коррелятор работает следующим образом.

Каждая выборка входного сигнала (интервал дискретизации входного сигнала определяется исходя из верхней граничной частоты опорного сигнала, записывается в первый блок 7 памяти, где хранится в течение N циклов вычисления ординат ВКФ, т.е. всегда в памяти хранится N текущих значений выборок входного сигнала. В блок 12 памяти записываются п прореженных, как правило, неравномерно (в соответствии с законом модуляции) выборок опорного детерминированного сигнала. В паузе между входными (непрореженными) выборками входного сигнала происходит опрос всего объема памяти (п выборок) блока 12. Адреса ячеек опроса последовательно формируются адресным счетчиком 2 как для опроса блока 12 памяти, так и блока 3 памяти адресов,, в котором записаны адреса п ячеек памяти блока 7, подлежащих опросу в первом цикле - вычислении первой ординаты ВКФ. Код адреса ячейки опроса через сумматор k, блок 5 элементов И и блок 6 элементов ИЛИ поступает на адресные входы блока 7 памяти. Значение выборки с выхода блока 7 памяти поступает в блок умножения 8, на второй вход которого синхронно поступает соответствующая ей.выборка опорного сигнала с выхода блока

12 памяти. Таким образом, осуществляется выбор п выборок (из массива N) входного сигнала. В следующем цикле вычисления очередной ординаты ВКФ адреса опроса ячеек памяти блока 7 изменяются на единицу, т.е. в каждом цикле вычислени ординаты ВКФ к адресам хранящимся в блоке 3 памяти адресов прибавляется в сумматоре k порядковый номер вычисляемой ординаты ВКФ формируемый адрес1 ым счетчиком 11-. Код адреса, формируемый последним, также поступает через блок 10 элементов И и блок Б элементов ИЛИ на адресные входы блока 7 памяти в момент записи входных выборок в данный блок 7 памяти. Триггер 9 по тактовым импульсам, поступающим с тактового устройства управляет работой двух блоков (5 и 10) элементов И и блоком 6 элементов ИЛИ, которые коммутируют коды адресов записи (с адресного счетчика 11) и коды адресов считывания (с сумматора

Ю.

В корреляторе в каждом цикле вычисления ВКФ количество операций умножения уменьшается в N/n раз. Уменьшение количества обращений к блокам памяти снижает требования по быстродействию к ним. Введение дополнительного блока памяти адресов объемом п компенсируется уменьшением объема памяти блока в опорном канале в N/n раз. Точность вычисления ординат ВКФ практически остается неизменной, т.е. а процессе вычисления используются выборки с равной степенью корреляции, практически обеспечивающие максимальные или заданные точностные параметры. Устраненные из процесса вычисления выборки с сильной степенью корреляции практически не улучшили бы точностные параметры. К достоинствам предлагаемого устройства относится тот факт, что корреляционная функция по-прежнему вычисляется с шагом, равным интервалу дискретизации входного процесса. Кроме того, использование в процессе вычисления неравномерно расположенных выборок устраняет возможность появления синхронной помехи.

формула изобретения

Цифровой коррелятор, содержащий блок умножения, входы которого подключены соответственно к выходам перг

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1980 |

|

SU959091A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой коррелятор | 1986 |

|

SU1336031A1 |

| Цифровой коррелятор для обнаружения эхосигналов | 1979 |

|

SU879595A1 |

| Цифровой коррелятор | 1984 |

|

SU1264200A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

Авторы

Даты

1982-06-30—Публикация

1980-12-26—Подача