(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИНХРОИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсов | 1983 |

|

SU1223218A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Устройство для контроля считываемой информации | 1986 |

|

SU1312579A1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| Устройство для обучения | 1986 |

|

SU1345234A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| Устройство для ввода информации | 1983 |

|

SU1119000A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

I

Устройство относится к вычислительной технике и может быть использовано при проектировании цифровых вычислительных устройств с изменяемым быстродействием.

Известно вычислительное устройство, в котором используется двойная синхронизация устройств, обеспечивающая переработку данных с различным быстродействием 1.

В известном устройстве производится выбор одной из двух тактовых сеток,в зависимости от типа конструкции. Для этого имеется два генератора тактовых импульсов, подключаемых через коммутатор. При выполнении быстрой инструкции подключается более высокочастотный генератор, при выполнении медленной - низкочастотный.

Недостатком такого устройства является ограниченный диапазон регулировки, так как можно использовать только два тактовых набора импульсов.

Более широкий набор тактирующих сигналов позволяет реализовать устройство для формирования последовательности внешних сигналов 2. Устройство содержит в каждом канале счетчик времени с дешифратором, схемы И, ИЛИ, формирователь синхроимпульсов.

Недостатком данного устройства является то, что оно не позволяет изменить параметры импульсов в процессе работы уст. 5 ройства.

Наиболее полно задача перестройки параметров синхроимпульсов Б процессе работы решена в устройстве формирования синхроимпульсов 3. Устройство содержит задающий генератор, блок счетчиков-дешиф10раторов, формирователь синхроимпульсов. К входам блока счетчиков подключен задающий генератор, выходы блока счетчиков - к, формирователю синхроимпульсов. Устройство позволяет изменять параметры 5 синхроимпульсов в процессе работы.

Недостаток данного устройства в том, что оно не позволяет изменить временное положение и длительность каждого синхроимпульса независимо от других. 20 Цель изобретения - обеспечение независимости изменения временных параметров каждого синхроимпульса путем расширения диапазона фазовых соотношений синхроимпульсов.

767747

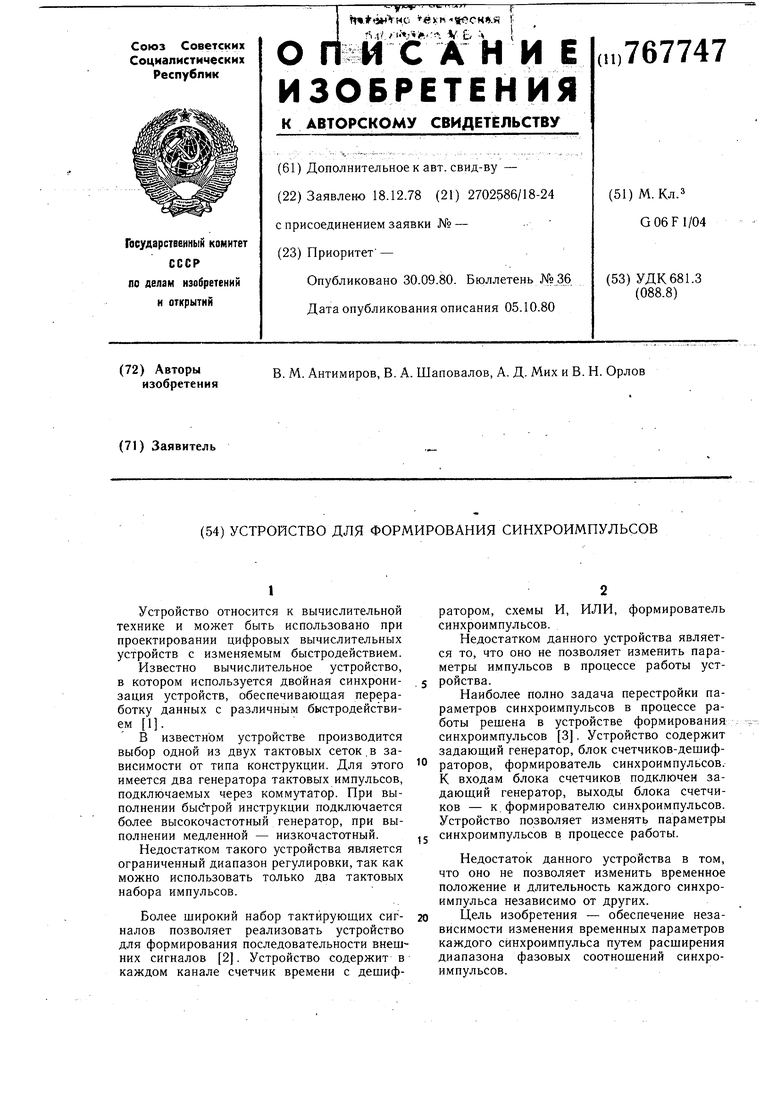

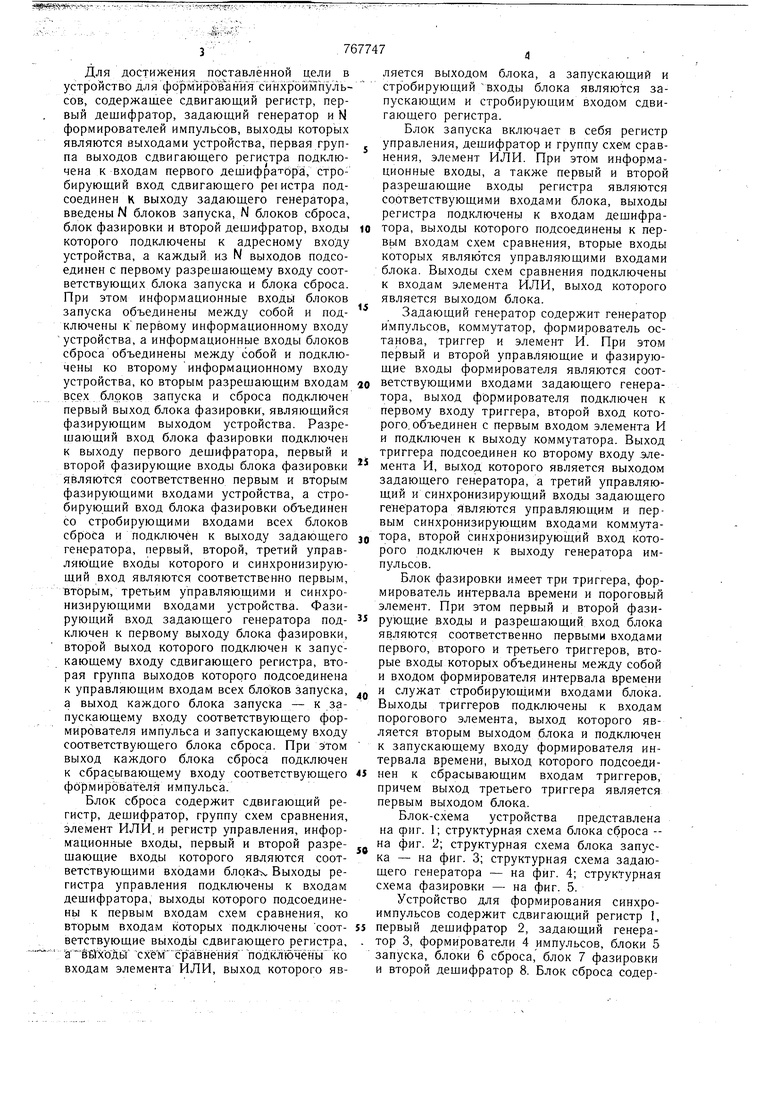

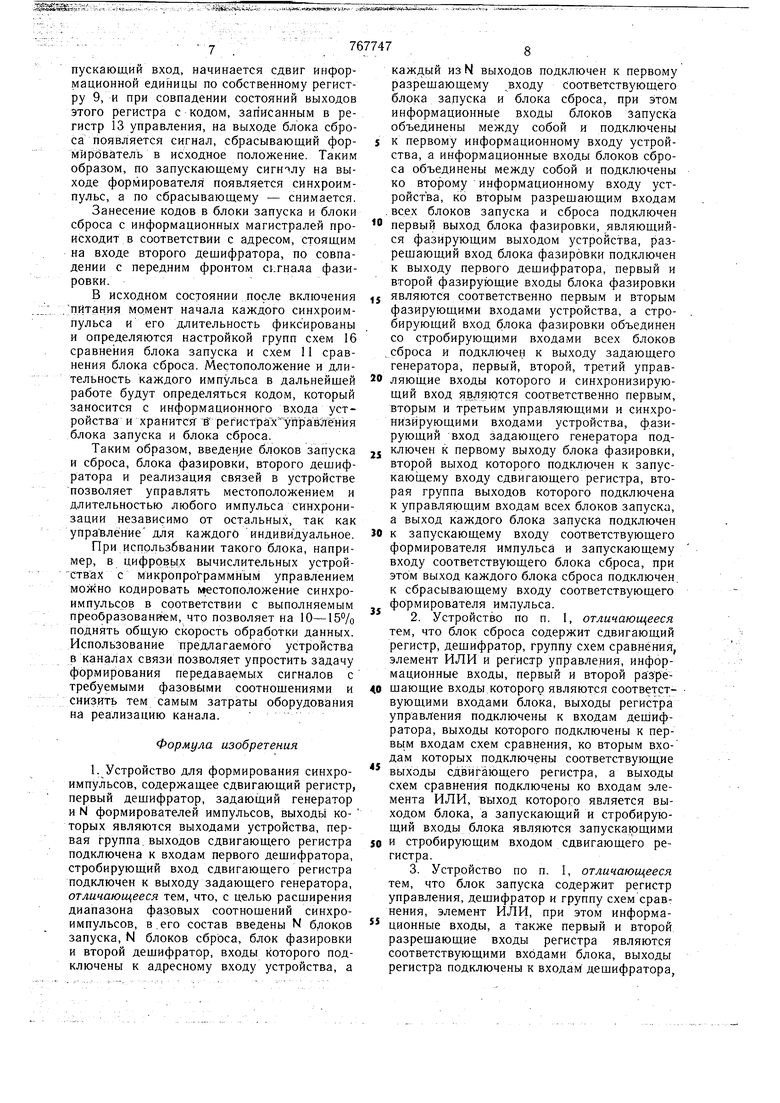

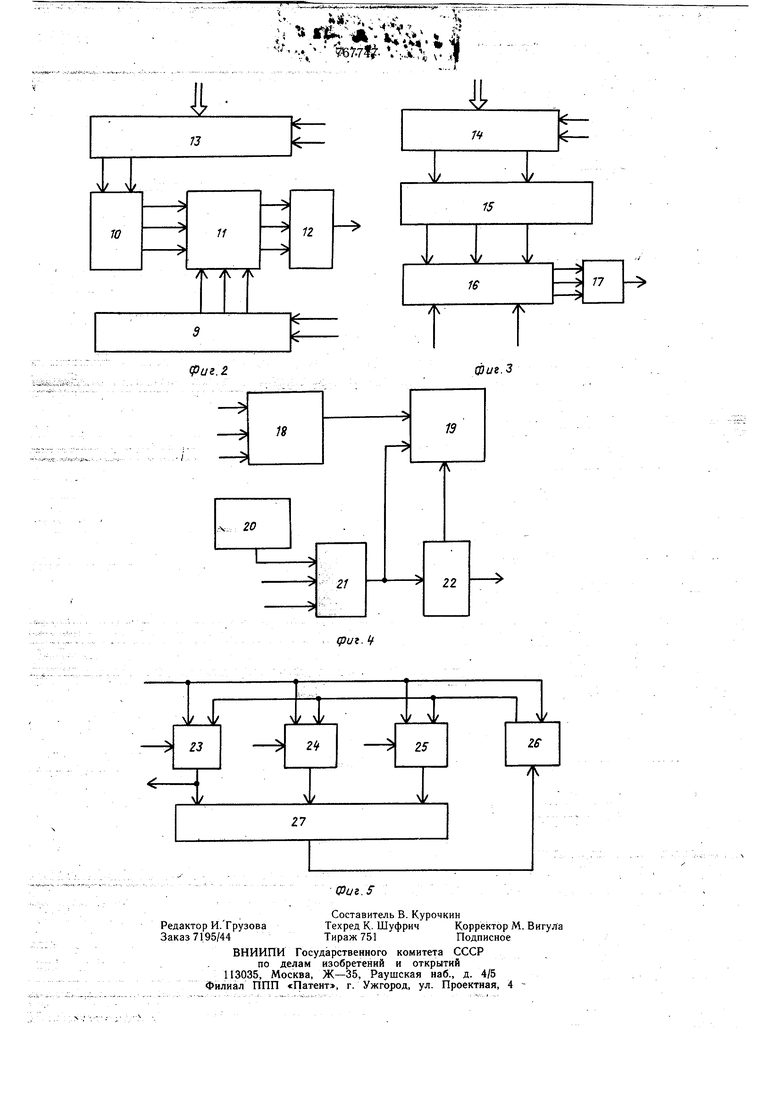

3 Для достижения поставленной цели в устройство для фо рмирбванйяс инхроимпульсов, содержащее сдвигающий регистр, первый дещифратор, задающий генератор и N формирователей импульсов, выходы которых являются выходами устройства, первая группа выходов сдвигающего регистра подключена к входам первого дешифратора, стробирующий вход сдвигающего регистра подсоединен К выходу задающего генератора, введены N блоков запуска, N блоков сброса, блок фазировки и второй дещифратор, входы которого подключены к адресному входу устройства, а каждый из N выходов подсоединен с первому разрешающему входу соответствующих блока запуска и блока сброса. При этом информационные входы блоков запуска объединены между собой и подключены кпервому информационному входу устройства, а информационные входы блоков сброса объединены между собой и подключены ко второму информационному входу устройства, ко вторым разрещающим входам всех блоков запуска и сброса подключен первый выход блока фазировки, являющийся фазирующим выходом устройства. Разрешающий вход блока фазировки подключен к выходу первого дещифратора, первый и второй фазирующие входы блока фазировки являются соответственно первым и вторым фазирующими входами устройства, а стробирующий вход блока фазировки объединен со стробирующими входами всех блоков сброса и подключен к выходу задающего генератора, первый, второй, третий управляющие входы которого и синхронизирующий вход являются соответственно первым, вторым, третьим управляющими и синхронизирующими входами устройства. Фазирующий вход задающего генератора подключен к первому выходу блока фазировки, второй выход которого подключен к запускающему входу сдвигающего регистра, вторая группа выходов которого подсоединена к управляющим входам всех блоков запуска, а выход каждого блока запуска - к запускающему входу соответствующего формирователя импульса и запускающему входу соответствующего блока сброса. При этом выход каждого блока сброса подключен к сбрас гвающему входу соответствующего формирователя импульса. Блок сброса содержит сдвигающий регистр, дешифратор, группу схем сравнения, элемент ИЛИ. и регистр управления, информационные входы, первый и второй разрещающие входы которого являются соответствующими входами блоках Выходы регистра управления подключены к входам дещифратора, выходы которого подсоединены к первым входам схем сравнения, ко вторым входам которых подключены соответствующие выходы сдвигающего регистра, а вдаодьг с хШ с равнения по;аключены ко входам элемента ИЛИ, выход которого является выходом блока, а запускающий и стробирующий входы блока являются запускающим и стробирующим входом сдвигающего регистра. Блок запуска включает в себя регистр управления, дещифратор и группу схем сравнения, элемент ИЛИ. При этом информационные входы, а также первый и второй разрешающие входы регистра являются соответствующими входами блока, выходы регистра подключены к входам дещифратора, выходы которого подсоединены к первым входам схем сравнения, вторые входы которых являются управляющими входами блока. Выходы схем сравнения подключены к входам элемента ИЛИ, выход которого является выходом блока. Задающий генератор содержит генератор импульсов, коммутатор, формирователь останова, триггер и элемент И. При этом первый и второй управляющие и фазирующие входы формирователя являются соответствующими входами задающего генератора, выход формирователя подключен к первому входу триггера, второй вход которого, объединен с первым входом элемента И и подключен к выходу коммутатора. Выход триггера подсоединен ко второму входу элемента И, выход которого является выходом задающего генератора, а третий управляющий и синхронизирующий входы задающего генератора являются управляющим и первым синхронизирующим входами коммутатора, второй синхронизирующий вход которого подключен к выходу генератора импульсов. Блок фазировки имеет три триггера, формирователь интервала времени и пороговый элемент. При этом первый и второй фазирующие входы и разрещающий вход блока являются соответственно первыми входами первого, второго и третьего триггеров, вторые входы которых объединены между собой и входом формирователя интервала времени и служат стробируюш ими входами блока. Выходы триггеров подключены к входам порогового элемента, выход которого является вторым выходом блока и подключен к запускающему входу формирователя интервала времени, выход которого подсоединен к сбрасывающим входам триггеров, причем выход третьего триггера является первым выходом блока. Блок-схема устройства представлена на фиг. 1; структурная схема блока сброса -на фиг. 2; структурная схема блока запуска - на фиг. 3; структурная схема задающего генератора - на фиг. 4; структурная схема фазировки - на фиг. 5. Устройство для формирования синхроимпульсов содержит сдвигающий регистр 1, первый дешифратор 2, задающий генератор 3, формирователи 4 импульсов, блоки 5 запуска, блоки 6 сброса, блок 7 фазировки и второй дещифратор 8. Блок сброса содержит сдвигающий регистр 9, дешифратор 10, группу схем 11 сравнения, элемент ИЛИ 12, регистр 13 управления. Блок 5 запуска включает в себя регистр 14 управления, дешифратор 15, группу схем 16 сравнения и элемент ИЛИ 17. Задающий генератор 3 содержит формирователь 18 останова, триггер 19, генератор 20 импульсов, коммутатор 21, элемент И 22. Блок 7 фазировки имеет три триггера: третий 23, первый 24, второй 25 формирователь 26 интервала времени, пороговый элемент 27.

В блоке 6 сброса информационные входы являются входами регистра 13 управления, первый и второй разрешающие входы которого являются соответствующими входами блока сброса и выходы подключены к входам дешифратора 10. Выходы дещифратора подключены к первым входам схем сравнения, ко вторы-м входам схем сравнения подсоединены выходы сдвигающего регистра 9, выходы схем сравнения - к элементу ИЛИ 12, выход которой является выходом блока сброса. При этом запускающий и стробирующий входы блока сброса являются соответствующими входами регистра 9.

В блоке 5 запуска, информационные входы, а также первый и второй разрещающие входы регистра 14 управления являются соответствующими входами блока запуска. Выходы регистра управления подключены к входам дещифратора 15, выходы которого подсоединены к первым входам схем 16 сравнения, вторые входы которых являются управляющими входами блока запуска, а выходы подключены к входам элемента ИЛИ 17, выход которого служит выходом блока запуска.

В задающем генераторе 3 первый и второй управляющие и фазирующие входы являются соответствующими входами формирователя 18 останова, выход которого подключен к первому входу триггера 19, второй вход которого объединен с первым входом элемента И 22 и подключен к выходу коммутатора 21. Второй вход элемента И подсоединен к выходу триггера, выход которого является выходом задающего генератора, синхронизирующий и третий управляющий входы которого служат соответственно первым синхронизирующим и управляющим входами коммутатора 21, второй синхронизирующий вход которого подключен к выходу генератора 20 импульсов.

В блоке 7 фазировки первый и второй фазирующие и разрешающие входы являются первыми входами соответственно первого 24, второй 25 и третьего 23 триггеров. Стробирующий вход блока является входом формирователя 26 интервала времени и объединен со вторыми входами триггеров. Выходы триггеров подключены к входам порогового элемента 27, выход которого служит вторым выходом блока и подключен к запускающему входу формирователя 26 интервала времени, выход которого подсоединен к сбрасывающим входам всех триггеров При этом выход третьего триггера является первым выходом блока фазировки.

При работе устройства можно выделить режим, работы на внутренней частоте и режим работы на внёщней. В первом случае импульсы высокой частоты берутся от встроенного генератора 20, во втором - от внещнего, по отнощению к устройству, генератора сигналы с которого поступают на синхронизирующий вход задающего генератора 3. Переключение с одного режима на другой осуществляется коммутатором 21 по внещнему управляющему сигналу, поступающему на третий управляющий вход задающего генератора 3. В любом из этих режимов работы возможно прекращение формирования импульсов, т. е. сохранение определенного и неизменного состояния выходных щин устройства на время действия внешнего сигнала «Останов, поступающего на первый управляющий вход задающего генератора 3. Момент начала «замораживания выходного состояния может начинаться или с очередных импульсов высокой частоты, которые перестают поступать на выход задающего генератора, или с очередного фазирующего импульса, поступающего на фазирующий вход задающего генератора.

При отсутствии сигнала «Останов импульсы с выхода задающего генератора поступают на вход сдвигающего регистра. По совпадению с импульсом от блока фазировки, поступающим на запускающий вход сдвигового регистра, в его первый разряд заносится информационная единица, которая сдвигается последовательно с интервалом, равным периоду импульсов высокой частоты. После прохождения единицей всего регистра все его разряды имеют нулевое значение. При этом состоянии регистра сраТУатывает первый дешифратор, с его выхода поступает сигнал на блок фазировки и появляется сигнал на первом выходе этого блока. При наличии сигнала хотя бы на одном из двух внешних фазирующих входов, на втором выходе блока фазировки появляется сигнал, разрещающий занесение очередной единички в первый разряд регистра, после чего цикл повторяется. Комбинацию сигналов на внещних фазирующих выходах можно организовать в режиме внутренней и вн€щней фазировки.

При продвижении единицы по сдвигающему регистру 1 на управляющие входы блоков запуска поступают сигналы. При совпадении кода, записанного в эти блоки с первой информационной магистрали, с состоянием управляющих входов блока запуска этот блок вырабатывает сигнал запуска, по которому включаются соответствующие формирователи импульсов и одновременно запускаются блоки сброса. В блоке сброса по сигналу, поступающему на за7

пускающий вход, начинается сдвиг информационной единицы по собственному регистру 9, и при совпадении состояний выходов этого регистра с кодом, записанным в регистр 13 управления, на выходе блока сброса появляется сигнал, сбрасывающий формирователь в исходное положение. Таким образом, по запускающему сигналу на выходе формирователя появляется синхроимпульс, а по сбрасывающему - снимается.

Занесение кодов в блоки запуска и блоки сброса с информационных магистралей происходит в соответствии с адресом, стоящим на входе второго дешифратора, по совпадении с передним фронтом сигнала фазировки.

В исходном состоянии после включения питания момент начала каждого синхроимпульса и его длительность фиксированы и определяются настройкой групп схем 16 сравнения блока запуска и схем 11 сравнения блока сброса. Местоположение и длительность каждого импульса в дальнейшей работе будут определяться кодом, который заносится с информационного входа устройства и хранится в регистра1(упраблёния блока запуска и блока сброса.

Таким образом, введен,ие блоков запуска и сброса, блока фазировки, второго дешифратора и реализация связей в устройстве позволяет управлять местоположением и длительностью любого импульса синхронизации независимо от остальных, так как управлёние для каждого индивидуальное.

При испрльзбвании такого блока, например, в цифровьгх вычислительных устрой ствах с микропрограммным управлением можно кодировать местоположение синхроимпульсов в соответствии с выполняемым преобразованием, что позволяет на 10-IS /o поднять общую скорость обработки данных. Использование предлагаемого устройства в каналах связи позволяет упростить задачу формирования передаваемых сигналов с требуемыми фазовыми соотношениями и снизить тем самым затраты оборудования на реализацию канала.

Формула изобретения

767747

каждый из N выходов подключен к первому разрешающему входу соответствующего блока запуска и блока сброса, при этом информационные входы блоков запуска объединены между собой и подключены

к первому информационному входу устройства, а информационные входы блоков сброса объединены между собой и подключены ко второму информационному входу устройства, ко вторым разрешающим входам . всех блоков запуска и сброса подключен

первый выход блока фазировки, являющийся фазирующим выходом устройства, разрешающий вход блока фазировки подключен к выходу первого дешифратора, первый и второй фазирующие входы блока фазировки

являются соответственно первым и вторым фазирующими входами устройства, а стробирующий вход блока фазировки объединен со стробирующими входами всех блоков сброса и подключен к выходу задающего генератора, первый, второй, третий управляющие входы которого и синхронизирующий вход являются соответственно первым, вторым и третьим управляющими и синхронизирующими входами устройства, фазирующий вход задающего генератора подJ ключен к первому выходу блока фазировки, второй выход которого подключен к запускаюш,ему входу сдвигающего регистра, вторая группа выходов которого подключена к управляющим входам всех блоков запуска, а выход каждого блока запуска подключен

O к запускающему входу соответствующего формирователя импульса и запускающему входу соответствующего блока сброса, при этом выход каждого блока сброса подключен, к сбрасывающему входу соответствующего формирователя импульса.

выходы сдвигающего регистра, а выходы схем сравнения подключены ко входам элемента ИЛИ, выход которого является выходом блока, а запускающий и стробирующий входы блока являются запускающими

0 и стробирующим входом сдвигающего регистра.

Ь. at:-:i . . о К « - 2 г л

1

Авторы

Даты

1980-09-30—Публикация

1978-12-18—Подача