Изобретение относится к вычислительной технике и может быть использовано при создании программного обеспечения (ПО) управляющих вычислительных машин (УВМ) и бортовых вычислительных систем (БВС) на их основе, которые являются центральным звеном систем автоматического управления (САУ) робототехническими комплексами (РТК) и изделиями ракетно-космической техники (РКТ). Одним из важных этапов создания ПО этих систем является этап отработки программ и подтверждения их корректной работы для различных наборов исходных параметров (задания на работу САУ) и состава обрабатываемой информации, что является достаточно трудоемким и продолжительным процессом, занимающим значительную часть времени проектирования системы и требующим существенных материальных затрат. Поэтому во всем мире уделяется серьезное внимание как методике, так и средствам верификации ПО. Особенно большие сложности верификации ПО возникают при создании программ реального времени для УВМ и БВС, входящих в состав САУ изделий РКТ и РТК. Примерами таких систем являются УВМ, разработки ФГУП НПОА, входящие в состав РТК «Сура», работавшего при ликвидации последствий аварии на Чернобыльской АЭС, а также БВС различных предприятий, входящие в состав САУ изделий РКТ. Сложность создания ПО для таких САУ усугубляется необходимостью введения в его состав задач самоконтроля исправности УВМ и БВС. Большой объем занимают задачи нейтрализации возникающих в процессе работы собственных отказов УВМ и САУ и отказов в смежной аппаратуре, а также задачи сохранения работоспособности САУ при деградации из-за дозовых факторов параметров компонентов (элементной базы) устройств и сохранения работоспособности САУ за счет снижения производительности вычислительных средств путем снятия с решения части задач меньшей важности. В результате ПО должно быть работоспособным в условиях изменения вычислительных ресурсов (быстродействия, в частности) в процессе работы и адаптироваться к этим изменениям. Известны принципы отладки ПО, используемые американскими специалистами для ЭВМ общего назначения (См. монографию «Наука отладки», авторы Мэтт Тэллес и Юань Хсих / перевод с английского / изд. КУДИН - ОБРАЗ, Москва, 2003, с.217). В основе отладки лежит анализ результатов вычислений самим разработчиком ПО путем выдачи на внешние носители, например на цифровую печать, промежуточных результатов вычислений при фиксированном наборе входных параметров. Для этого в тексте программы делаются технологические вставки, обеспечивающие выдачу результатов для анализа. Недостатком такой отладки для систем реального времени является необходимость последующей коррекции программ БВС с целью экономии ресурсов времени и памяти БВС после завершения отладки для устранения не нужных в штатной работе технологических вставок, что требует повторения проверок. Такая отладка совершенно непригодна для верификации программ, работающих в реальном масштабе времени с непрерывно меняющейся входной информацией, так как любые вставки в программу искажают реальное время обменов и вычислений. Достаточно полное решение задачи отработки ПО реального времени для УВМ предлагают отечественные специалисты (См. Б.А.Микрин. «Бортовые комплексы управления космическими аппаратами и проектирование их программного обеспечения», изд. МГТУ им. Н.Э.Баумана, 2003, с.243-249, рис.4.1). Для отработки аппаратуры и ПО предлагается комплексный моделирующий стенд (KMC), содержащий бортовую вычислительную систему с отрабатываемым программным обеспечением, пульт управления стендом, моделирующую вычислительную платформу на основе ЭВМ общего назначения и полный комплект реальных датчиков и исполнительных устройств, связанных с БВС соответственно через аналого-цифровые и цифроаналоговые преобразователи. В состав КMC входит также комплект штатной аппаратуры космического аппарата, включая рабочие места экипажа.

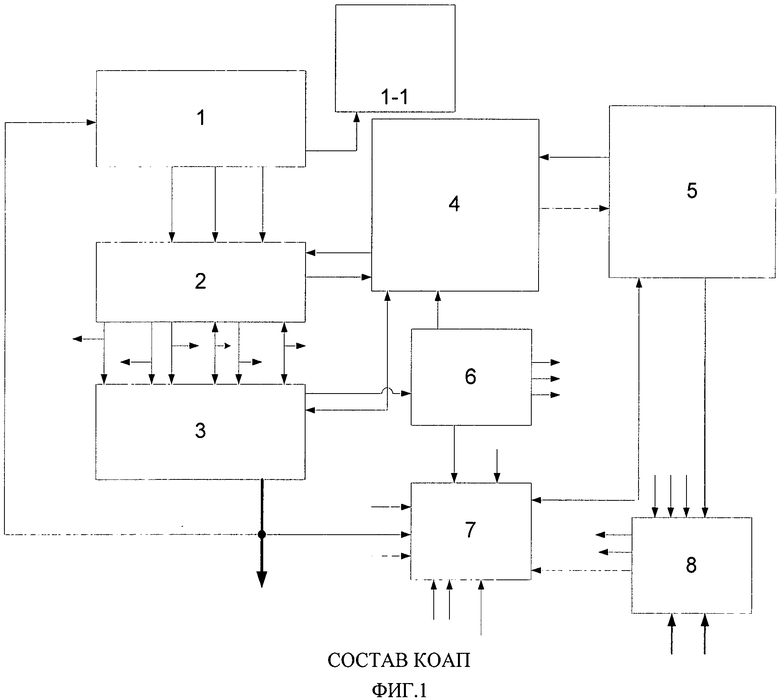

Такой состав аппаратуру комплексного стенда достаточно полно обеспечивает проверку правильности функционирования аппаратуры БВС и ее программного обеспечения в реальном времени, но в случае обнаружения ошибок не позволяет выполнить их направленный поиск, так как из-за наличия аналоговой аппаратуры не обеспечивается идентичность результатов в повторных включениях стенда. КMC не позволяет также проверить работу программного обеспечения для вариантов с нейтрализацией возникающих в процессе штатной работы катастрофических отказов или сбоев в аппаратуре БВС и САУ, так как недопустимо внесение неисправностей в штатную аппаратуру стенда из экономических соображений. Близкое по техническому содержанию решение в виде стенда полунатурного моделирования предлагают сотрудники Саратовского технического университета Авакумов A.B., Блескина Е.В. и Шкаев А.Е. (См. www. ). Предлагаемый ими стенд содержит собственно САУ, пульт управления и модель внешней среды, от которой идет управление через цифроаналоговые преобразователи на реальные датчики для формирования нужной входной информации БВС, а выходные управляющие сигналы и команды САУ воздействуют на реальные исполнительные механизмы, имеющие, кроме того, внутреннее управление от датчиков обратной связи, информация от которых также идет в модель. Такое построение стендов позволяет вести совместную проверку правильной работы аппаратуры САУ и ее ПО. В то же время в случае неправильного функционирования САУ из-за ошибок ПО поиск причин возникновения ошибок в этом стенде так же затруднен, как и у предыдущего комплекса. Это связано с наличием штатной аппаратуры с датчиками входной информации, цифроаналоговых и аналого-цифровых преобразователей, что не позволяет провести несколько повторений программного цикла управления с полностью идентичной входной информацией, а это является обязательным условием для обнаружения места ошибки в программе. Кроме того, в такой системе тоже недопустимы проверки функционирования при возникновении неисправностей в бортовой аппаратуре по тем же экономическим причинам. Нельзя проверить ПО при изменении производительности УВМ в процессе работы, например при снижении быстродействия процессоров, из-за деградации параметров комплектующих элементов, так как нельзя вносить изменения в штатную аппаратуру САУ. Более того даже просто создание такого стенда и поддержание его в рабочем состоянии требует существенных финансовых затрат, что ограничивает возможности верификации ПО. Наибольшие возможности для обеспечения оперативности и полноты проверки программ БВС с возможностью имитации неправильной работы аппаратуры САУ предоставляет КОМПЛЕКС ОТЛАДКИ (См. патент №2448363 от 20.04.2012). Данный комплекс можно принять за прототип. Комплекс содержит собственно бортовую УВМ, пульт управления комплексом (ПУК), управляющую ЭВМ общего назначения (ПЭВМ) и имитаторы входной информации, подключенные выходами к УВМ. Такое построение обеспечивает стабильность и повторяемость результатов вычислений УВМ от «прогона» к «прогону», обеспечивает имитацию отказов путем формирования соответствующей входной информации, но требует предварительной подготовки массивов входной имитирующей информации и контрольных результатов для проверки с применением модели внешней среды (объекта управления) и алгоритмов управления, для чего создается отдельный моделирующий комплекс. Такое этапное построение отладки позволяет вести проверку программ только в разомкнутом цикле, что снижает оперативность, увеличивает сроки и стоимость отработки. Кроме того, в этом комплексе затруднен поиск ошибок, связанных с неправильной работой аппаратуры, так как отсутствуют средства регистрации и детального визуального анализа с помощью устройств отображения (например, осциллографа или логического анализатора) выдаваемых на управление сигналов, команд и информации, передаваемой по линиям связи. Для анализа требуется введение дополнительной аппаратуры регистрации и средств синхронизации развертки регистраторов с анализируемым моментом времени, обеспечивающих связь времени работы регистрирующей аппаратуры с моментами выдачи управляющих сигналов и передачи данных. Комплекс не позволяет провести проверку ПО при изменении производительности (быстродействия) вычислительных средств. Для оптимизации сроков отработки и обеспечения регистрации и анализа ошибок в работе аппаратуры САУ (в программах и аппаратуре БВС) предлагается моделирующий комплекс отработки аппаратуры и программ (Моделирующий КОАП). Далее просто комплекс. Комплекс содержит моделирующую ПЭВМ с устройством отображения, на которое выводятся текущие параметры состояния объекта и управляющие воздействия (при создании соответствующих программ может отображаться движение объекта по траектории с изменением состояния объекта при отделении его составных частей типа обтекателей и разгонных блоков), имитаторы подсистем и технологическую БВС с отрабатываемой программой, выход которой в реальной САУ поступает на исполнительные устройства объекта, а в комплексе - на входы моделирующей ЭВМ и регистратора. БВС является не штатной, а технологической. Технологичность обусловлена тем, что в ее состав введены дополнительные (технологические) схемные средства в виде останавливаемых формирователей синхроимпульсов с перестраиваемыми генераторами и буферных усилителей для выдачи состояния внутренних связей и магистралей на внешние шины. Технологические связи введены с целью регистрации передаваемой информации и ее обработки пультом управления и управляющей ЭВМ. Эти связи не влияют на работу программ, но облегчают поиск ошибок ПО. Для управления комплексом есть пульт управления комплексом (ПУК) и управляющая ЭВМ общего назначения, в качестве которой так же, как и в известном комплексе, может использоваться ПЭВМ типа IBM PC. Введены дополнительно синхронизатор, регистратор, имитатор датчика времени, управляемые формирователь синхроимпульсов (ФСИ) и управляемый источник вторичного электропитания (ИВЭП), входы которого являются входами силового питания (промышленная сеть переменного тока или генератор постоянного тока). Выходы ИВЭП и ФСИ подключены к соответствующим входам БВС и имитаторов. ИВЭП включает управляемый модуль постоянного питания (МПП) и модуль импульсного питания (МИП). ИВЭП и ФСИ имеют входы установки от управляющей ЭВМ, а ИВЭП, кроме того, имеет синхронизацию тремя управляющими сигналами от синхронизатора. Управление МПП и ФСИ обеспечивает изменение номинала выходного напряжения «прокачку» и имитацию изменения быстродействия элементов из-за набора дозы от ионизирующего излучения, что позволяет проверить работоспособность штатной аппаратуры в диапазоне изменения напряжения питания и быстродействия для выявления неустойчивых дефектов и проверку работы ПО при изменении быстродействия с изменением напряжения питания вычислительных средств, чего нет в известных комплексах. При этом пульт управления подключен к технологическим выходам (адресным и информационным шинам модулей БВС) и связан установочным входом с управляющей ЭВМ. Входы БВС подключены к имитаторам входной информации. Входы имитаторов подключены к моделирующей ЭВМ, вход прерывания которой объединен с управляющим входом (входом сигнала останова) БВС и подключен к выходу «останова» ПУК, синхронизирующий вход которого подключен к синхронизирующему (тактовому) выходу БВС. Технологическая БВС содержит системный модуль, к которому через троированную системную магистраль подключены системное запоминающее устройство, специализированные вычислительные устройства (СВУ) подсистем инерциальной навигации (ПИН), аппаратуры спутниковой навигации (ACH), СВУ подсистемы обработки изображений (ПОИ), а также вычислительных модулей, каждый из которых содержит подключенный к системной магистрали процессор и подключенное к нему через свою двунаправленную связь, имеющую технологический выход, локальное запоминающее устройство. В составе системы имеется перестраиваемый формирователь синхроимпульсов (ФСИ). В штатном СВУ ПИН частотные входы являются входами от датчика линейного ускорения и трех датчиков угловых скоростей, которые в составе комплекса отладки подключены к выходам соответствующих имитаторов. Пульт управления комплексом содержит регистр адреса, вход которого является входом пульта, на который подключены адресные шины запоминающих устройств того вычислителя, анализ программ которого ведется в данный момент. ПУК содержит также контрольный регистр адреса, установочный вход которого является входом пульта, подключенным к управляющей ЭВМ. В этот регистр заносится адрес ячейки памяти, при обращении к которой оператор хочет приостановить вычисления и списать в управляющую ЭВМ из анализируемого вычислителя информацию для анализа. Выходы регистра адреса подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы контрольного регистра адреса. Выход схемы сравнения подключен к входу счетчика событий, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы регистра номера цикла, вход которого является входом пульта, подключенного к управляющей ЭВМ. В этот регистр заносится номер цикла, в котором оператор хочет провести анализ результатов. Этот регистр необходим в связи со спецификой построения ПО БВС. ПО организовано повторяющимися циклами и адрес обращения к памяти в процессе выполнения программы встречается многократно, а результаты для анализа необходимы после определенного промежутка времени. Для этого в пульте имеется счетчик времени (счетчик тактов), установочный вход которого является входом пульта, подключенным к управляющей ЭВМ, а счетный вход является входом пульта, подключенным к синхронизирующему выходу БВС. Информация в этот счетчик заносится в дополнительном коде. Счетчик считает тактовые импульсы, поступающие на его счетный вход, подключенный к технологическому выходу формирователя синхроимпульсов БВС. При переполнении счетчика, т.е. истечении заданного интервала времени (тактов), на его выходе, подключенном к первому входу элемента ИЛИ, ко второму входу которой подключен выход схемы сравнения, появляется сигнал. Выход элемента подключен к запускающему входу триггера останова, выход которого является выходом «останова» пульта, подключенного к входам останова формирователя синхроимпульсов БВС, имитатора датчика времени и входу прерывания управляющей ЭВМ. К сбрасывающему входу триггера останова подключен сбрасывающий выход управляющей ЭВМ, сигнал на котором появляется после завершения списывания информации из БВС. Наличие узлов анализа кодов адреса и текущего реального бортового времени позволяет без технологических вставок и коррекций текста штатной программы получать оператору информацию в интересующий его момент времени. Использование сигнала останова в регистраторе позволяет зафиксировать в нем данные, записанные в память регистратора на интервале времени, предшествующем моменту анализа. Все это, т.е. возможность приостановки вычислений для списывания данных из памяти вычислителей БВС, а также наличие регистратора, позволяет получать необходимую для поиска ошибок ПО информацию без внесения технологических вставок в штатные программы, и, следовательно, без нарушения работы программ в реальном времени. СВУ ПИН включает процессор обмена с подключенным к нему через двустороннюю связь с технологическим выходом специализированным запоминающим устройством ПИН. Вход-выход этого процессора объединен с входом-выходом блока связи по магистрали и имеет технологический выход. Выход процессора обмена подключен к установочному входу формирователя синхроимпульсов ПИН и входу буферного регистра. Выход этого регистра подключен к входам n последовательно соединенных шинами переноса умножителей, выходы которых подключены к входам сумматора, подключенного выходом к блоку связи по магистрали, к синхронизирующим входам которого, как и к синхронизирующим входам других блоков и узлов СВУ, подключены выходы формирователя синхроимпульсов ПИН. СВУ ПОИ содержит управляющий микропроцессор с подключенным к нему через двунаправленную связь обрабатывающим запоминающим устройством (ОЗУ). К этому микропроцессору через первую магистраль подключено k вычислительных микропроцессоров, подключенных через вторую магистраль к ОЗУ. Входы микропрограммного управления всех микропроцессоров подключены к выходам блока микропрограммного управления (БМУ), установочный вход которого подключен к выходу управляющего микропроцессора, а входы признаков БМУ подключены к выходам признаков всех микропроцессоров. Вход-выход управляющего микропроцессора и обе магистрали имеют технологический выход для подключения к регистратору. Перестраиваемый формирователь синхроимпульсов содержит три перестраиваемых генератора импульсов, соответственно первый, второй и третий. Выход каждого из генераторов подключен к входу своего блока фазирования, соответственно первого, второго и третьего. Выходы каждого из этих блоков подключены к блоку мажоритации, выходы которого являются выходами формирователя. При этом фазирующий выход каждого из блоков подключен к фазирующим входам двух других блоков. Вход останова формирователя и входы останова блоков фазирования являются внешним входом, подключенным к выходу пульта управления. Блок фазирования содержит логический элемент, первый вход которого является входом блока, подключенным к своему генератору импульсов. Выход элемента подключен к входу реализованного на динамических триггерах динамического счетчика и входу сдвигового регистра. Выходы счетчика подключены к входам фазирующего дешифратора, выход которого подключен к запускающему входу триггера приостановки, выход которого является фазирующим выходом блока и подключен ко второму входу логического элемента и первому входу мажоритарного элемента, выход которого подключен к первому входу элемента И, второй вход которого является входом останова блока, а выход элемента подключен к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера приостановки. Ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, стробирующий вход которых объединен с первым входом двухвходового элемента, а входы являются фазирующими входами блока. При этом выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам f триггеров формирователей, выходы которых являются выходами блока. Имитатор ПИН содержит блок связи с моделирующей ЭВМ, вход-выход которого является входом-выходом имитатора, а установочные выходы блока связи подключены к установочным входам формирователя частоты канала линейного ускорения и трех формирователей (первого, второго и третьего) каналов углового ускорения, выходы формирователей являются выходами имитатора, подключенными к входам СВУ ПИН. Генератор частоты формирователей имитатора содержит группу последовательно включенных инверторов. Выходы инверторов подключены к входам первого мультиплексора, выход которого подключен к входу первого инвертора, образуя тем самым кольцевой генератор, и входу первого счетчика частоты. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты. Инкрементный и декрементный выходы этой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора, а установочный вход первого счетчика кода частоты и установочный вход первого регистра кода частоты являются установочным входом формирователя и имитатора подсистемы, подключенным к моделирующей ЭВМ. Заданием кодов в регистр и счетчик кода частоты управляющая ЭВМ задает номинал частоты, формируемой кольцевым генератором, состоящим из инверторов и мультиплексора. Эта частота поступает в счетчик частоты, код которого сравнивается с заданным в регистре кода значением номинала, и, в зависимости от знака сравнения, схемой сравнения вырабатывается сигнал инкрементации или декрементации счетчика кода частоты, исправленный код которого поступает на управляющие входы мультиплексора. Последний в соответствии с этим кодом изменяет номер подключаемого инвертора из группы, меняя тем самым время прохождения сигнала по кольцу и, следовательно, корректируя выходную частоту в сторону приближения к заданному номинальному значению, что позволяет компенсировать дрейф параметров элементов кольцевого генератора, например, из-за изменения температуры помещения, что позволяет обойтись без дорогостоящих и ненадежных кондиционеров в помещении комплекса. Имитатор датчика времени реализован на основе стабилизированного кварцем таймерного генератора, выход которого подключен к счетному входу таймерного счетчика, останавливающий вход которого является входом имитатора, подключенного к выходу останова пульта управления. Входы счетчика подключены к входам таймерного регистра периода, вход которого является входом имитатора, подключенным к управляющей ЭВМ. Заданием кода в этот регистр задается период следования меток времени. Метка формируется циклически, так как после отработки записанного в счетчик дополнительного кода и формирования сигнала переноса, поступающего на выход, происходит перезапись кода в счетчик из регистра. Для этого выход счетчика подключен к управляющему входу регистра. Код из регистра переписывается в счетчик и цикл формирования повторяется, если отсутствует сигнал на остановочном входе счетчика. Код в регистре периода может изменяться оператором и соответственно период формирования метки, а наличие в основе стабилизированного кварцем генератора частоты обеспечивает высокую стабильность периода метки времени, не зависящую от температуры помещения. Имитатор датчиков подсистемы обработки изображений содержит устройство связи с моделирующей ЭВМ, вход-выход которого является входом-выходом имитатора, подключенным к моделирующей ЭВМ, а выходы устройства связи подключены к входам блоков памяти, выход каждого из которых через свое приемно-передающее устройство подключен к шине связи с БВС. В большинстве своем датчиками этой подсистемы являются или лучи высотомера, и (или) выходы оптических каналов видимого, инфракрасного и ультрафиолетового диапазона. Снятая информация этих датчиков представлена в виде двумерной матрицы, что позволяет реализовать этот имитатор на основе блоков памяти, в которые имитирующая информация заносится моделирующей ЭВМ, а считывается БВС в соответствии со своей диаграммой опроса датчиков. Регистратор содержит стабилизированный генератор импульсов, выход которого подключен к первому входу регистра сдвига, выход последнего разряда которого подключен ко второму входу регистра сдвига, обеспечивая тем самым его циклическую работу. Выходы разрядов этого регистра являются стробирующими выходами, выходы которых подключены к стробирующим входам триггеров регистрирующих регистров, обеспечивая последовательную запись во времени с дискретом периода генератора импульсов одного сигнала, если на все информационные входы триггеров подключен один и тот же сигнал, или параллельную запись нескольких сигналов, если каждый из них подключен к входу своего триггера. Увеличивая количество триггеров в регистрирующих регистрах, можно увеличить количество опросов, т.е. растянуть интервал анализа одного какого-то избранного сигнала (например, сигнала синхронизации какой-то важной команды), или, подключив сигналы к разным триггерам, можно увеличить число одновременно регистрируемых сигналов. Содержимое регистра один раз в цикл записывается в регистрирующее запоминающее устройство. Адрес для записи формируется счетчиком адреса, который считает циклы сдвига, для чего его счетный вход подключен к дополнительному выходу регистра сдвига, который останавливается по сигналу останова пульта управления, подключенного к запрещающему входу регистра сдвига. Начальное значение адреса в счетчике, подготовка (очистка регистрирующего запоминающего устройства), а также чтение их содержимого производит управляющая ЭВМ, для чего и счетчик, и запоминающее устройство через двунаправленные свои связи подключены к шине связи регистратора с управляющей ЭВМ. Модуль постоянного питания содержит последовательно включенные входной фильтр, трансформатор с установленным в первичную обмотку транзистором прерывателем, выпрямительный диод и выходной фильтр нижних частот. На выходе фильтра установлены последовательно соединенные резистор и диод, обеспечивающие параллельное включение нескольких модулей на общую нагрузку. Выход диода является выходом модуля. Выходные шины модуля подключены к входу преобразователя напряжения в частоту, который через элемент развязки подключен к частотному входу формирователя частоты, установочный вход которого является установочным входом модуля и источника питания, по которому управляющая ЭВМ задает код номинала выходного напряжения, а выход формирователя подключен к базе транзистора прерывателя, частота срабатывания которого определяет частоту смены тока в первичной обмотке трансформатора, а следовательно, и во вторичной, который после выпрямления и фильтрации превращается в выходное напряжение модуля и источника. Наличие обратной связи с выхода модуля через преобразователь напряжения в частоту со сравнением полученной частоты (фактически выходного напряжения) с заданным на вход формирователя требуемым значением обеспечивает стабилизацию выходного напряжения при изменении тока потребления. Формирователь частоты МПП содержит стабилизированный задающий генератор, группу последовательно соединенных инверторов, второй мультиплексор, второй счетчик частоты, интервальный счетчик, интервальный дешифратор, подключенный выходом к стробирующему входу второй схемы сравнения, второй регистр кода частоты и второй счетчик кода частоты. Выходы инверторов подключены к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом формирователя, вход частоты которого подключен к входу второго счетчика частоты, выходы которого подключены к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам второго счетчика кода частоты, установочный вход которого и вход второго регистра кода частоты являются установочным вводом модуля и источника питания. Через эти входы управляющая ЭВМ задает начальное значение частоты прерываний в счетчик кода частоты и контрольное значение частоты в регистр кода, а фактически задает выходное напряжение, которое превращается в частоту преобразователем напряжения в частоту. В этой реализации задающий генератор, счетчик и регистр являются формирователями опорного значения напряжения, с которым сравнивается выходное напряжение после перевода его в частоту. Такое построение формирователя частоты, управляющей частотой прерывания тока в первичной обмотке трансформатора с опорой на стабилизированный кварцем задающий генератор, а не на обычно используемый в таких модулях питания источник опорного напряжения (стабилитрон), не имеющий хорошей температурной стабильности, обеспечивает работу источника питания с высокой стабильностью выходного напряжения в широком диапазоне изменения температур, позволят, как и ряд описанных выше решений по реализации предлагаемого комплекса, обойтись в помещении комплекса без дорогостоящих и ненадежных кондиционеров, а также обеспечить изменение номинала питающего напряжения (прокачку) для выявления потенциально ненадежных или неверно спроектированных узлов аппаратуры и поиска причин неустойчивых отказов, что является достаточно сложной задачей, не имеющей решения в известных комплексах. Модуль импульсного питания содержит три параллельные ветви, в каждой из которых последовательно включены два МОП транзистора, объединенные истоки первых транзисторов которых подключены к шине силового питания, а объединенные стоки вторых транзисторов являются выходом модуля. При этом три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, включенных в разных ветвях, образуя выборку «2 из 3». Динамический триггер реализован как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя подключена в качестве элемента памяти IX цепь. Индуктивность этой цепи кроме рабочей обмотки имеет намотанную поверх нее встречно-компенсационную, концы которой закорочены. Такая реализация триггера обеспечивает его высокую помехоустойчивость к внешним электромагнитным помехам, которые могут быть вызваны искрением двигателей вентиляторов, работой городского транспорта с электрической тягой, включением и выключением бытового электрооборудования, ламп дневного света или испытательных климатических камер.

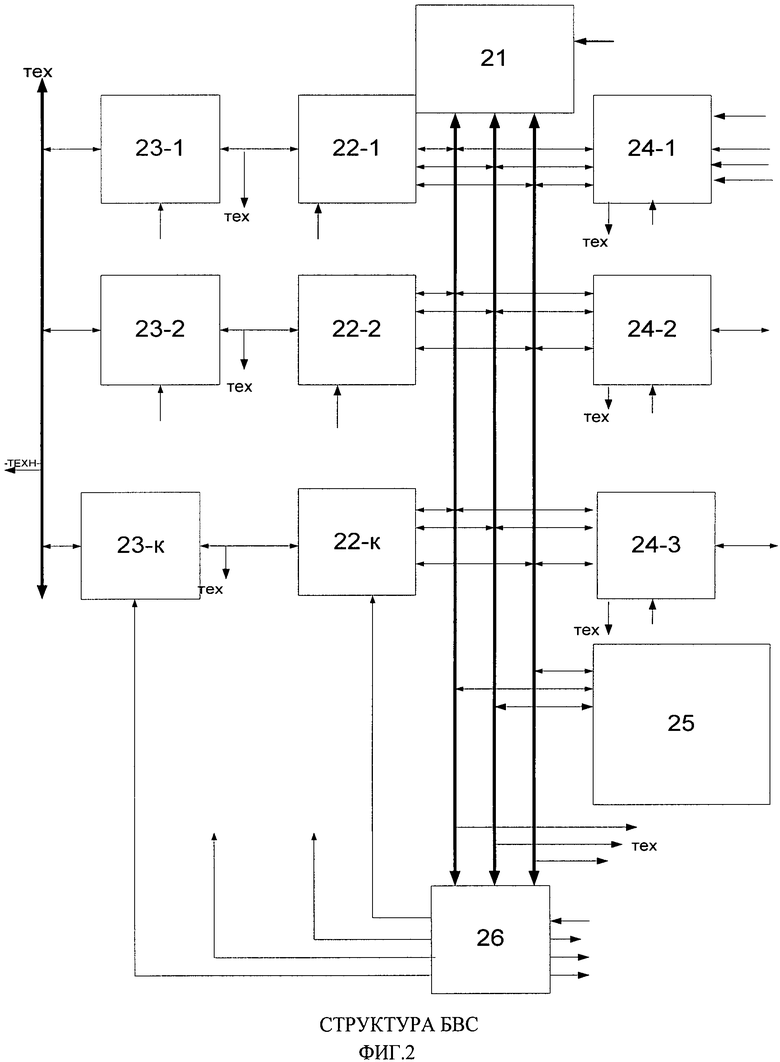

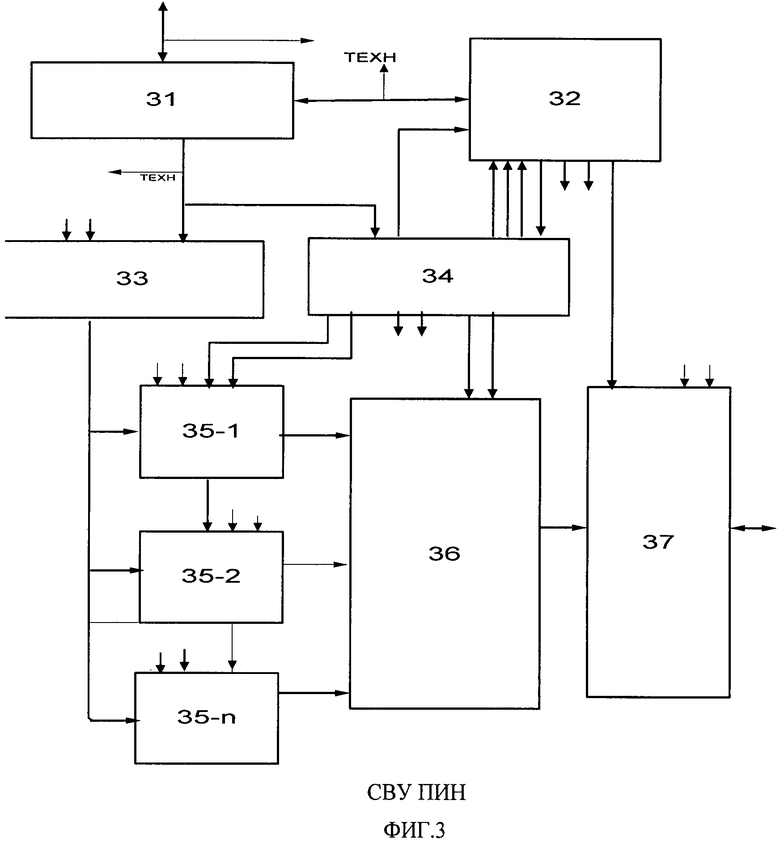

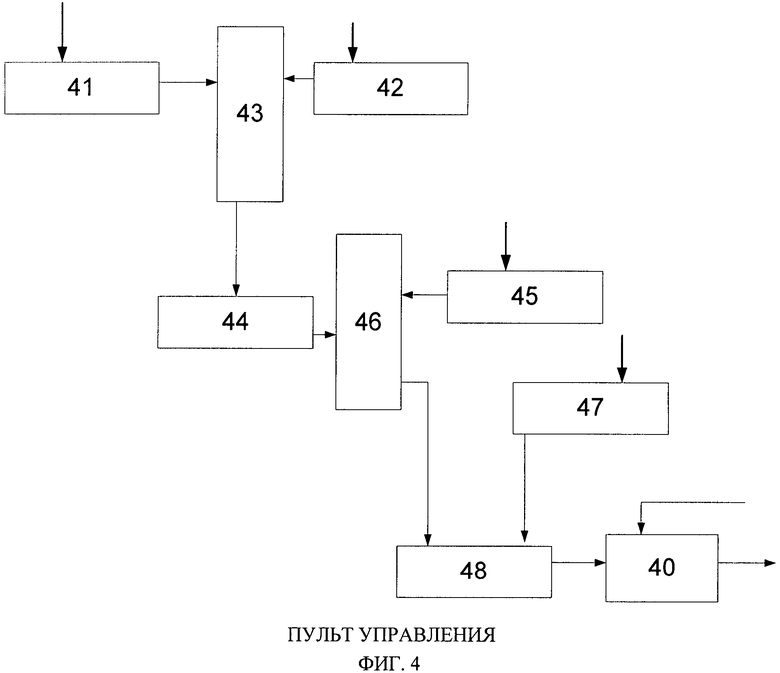

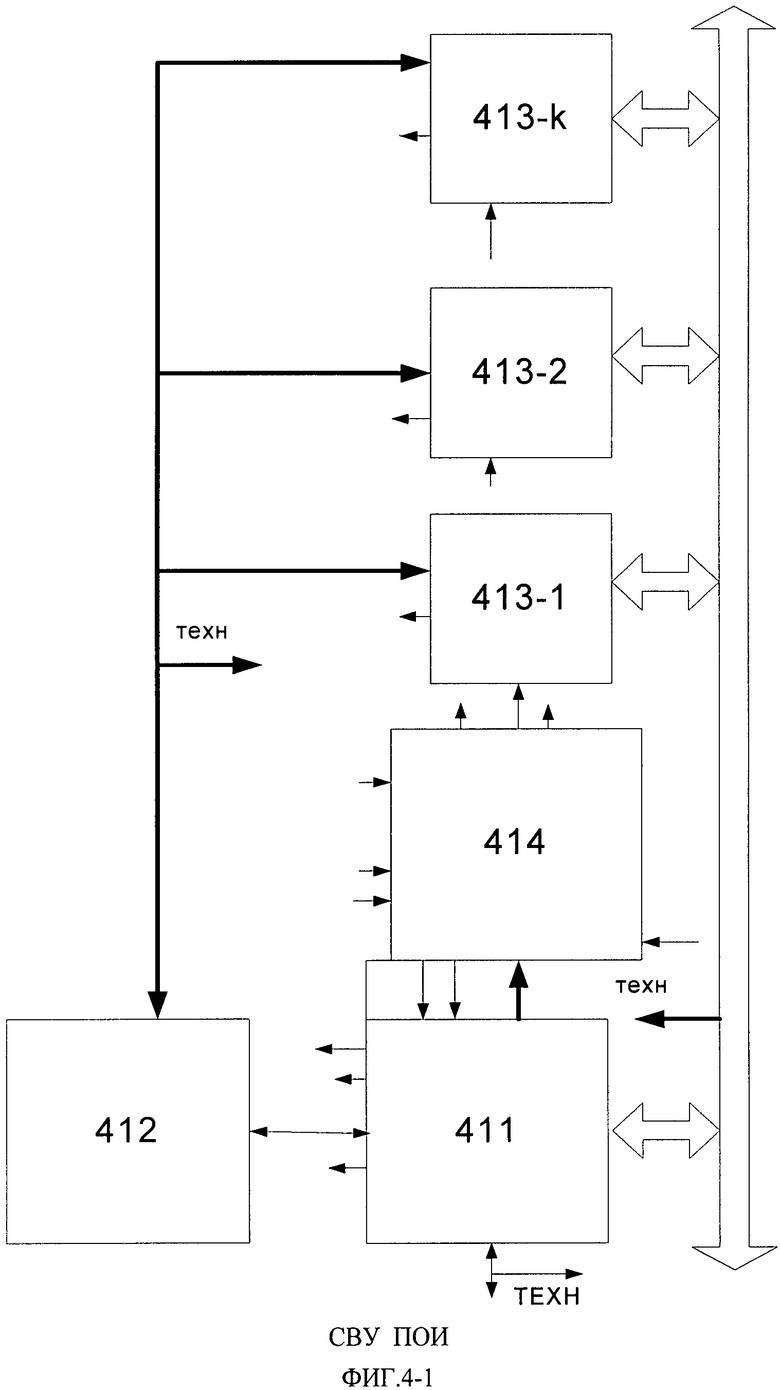

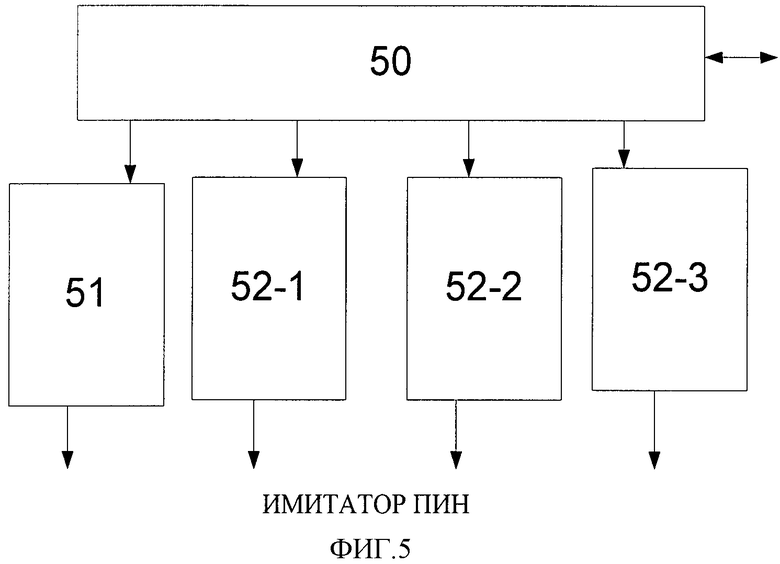

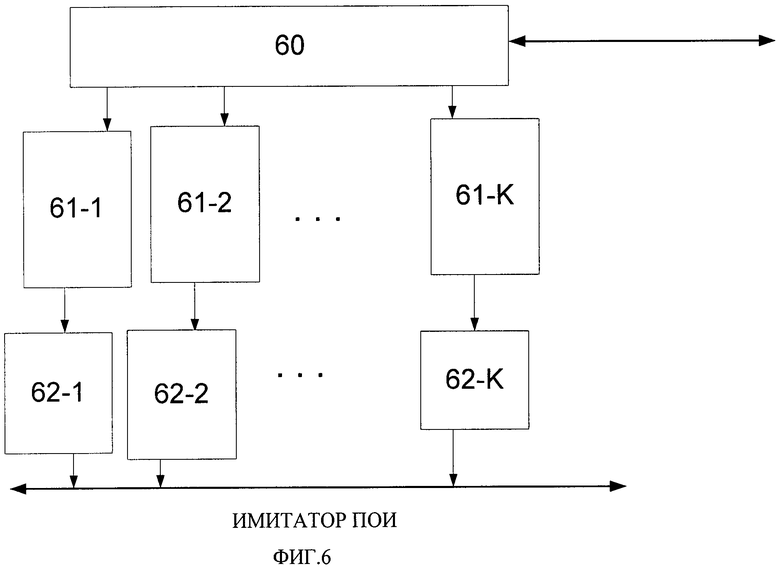

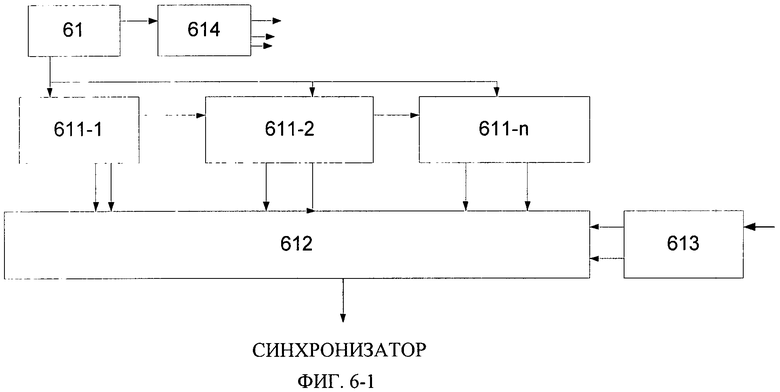

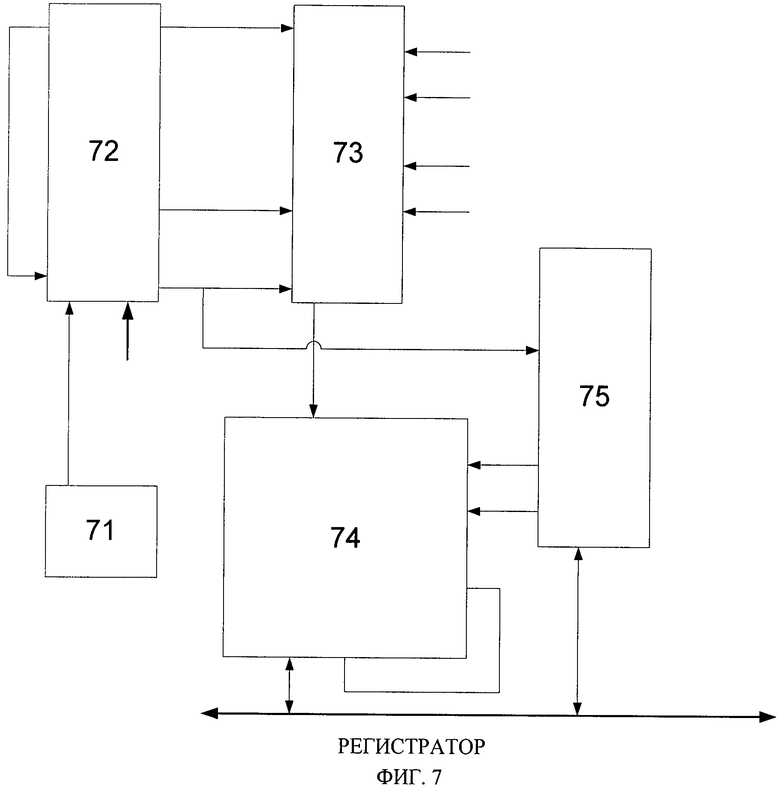

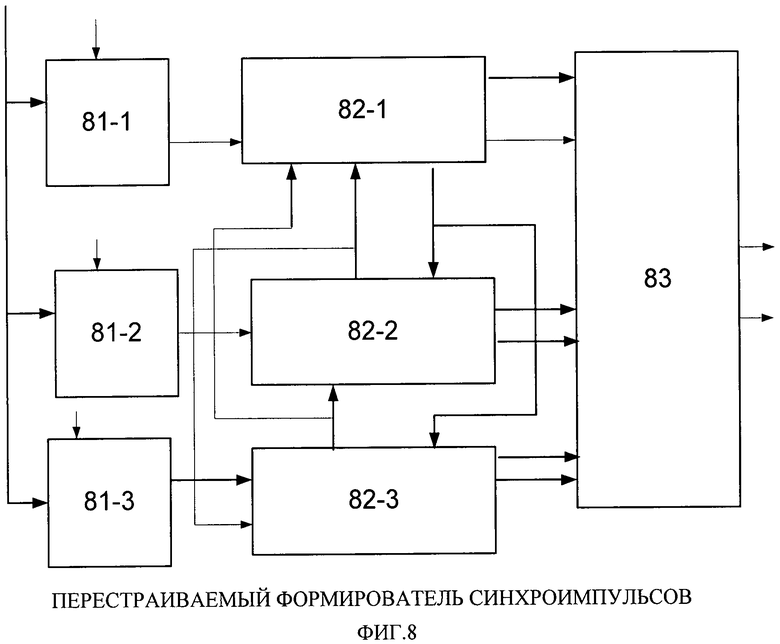

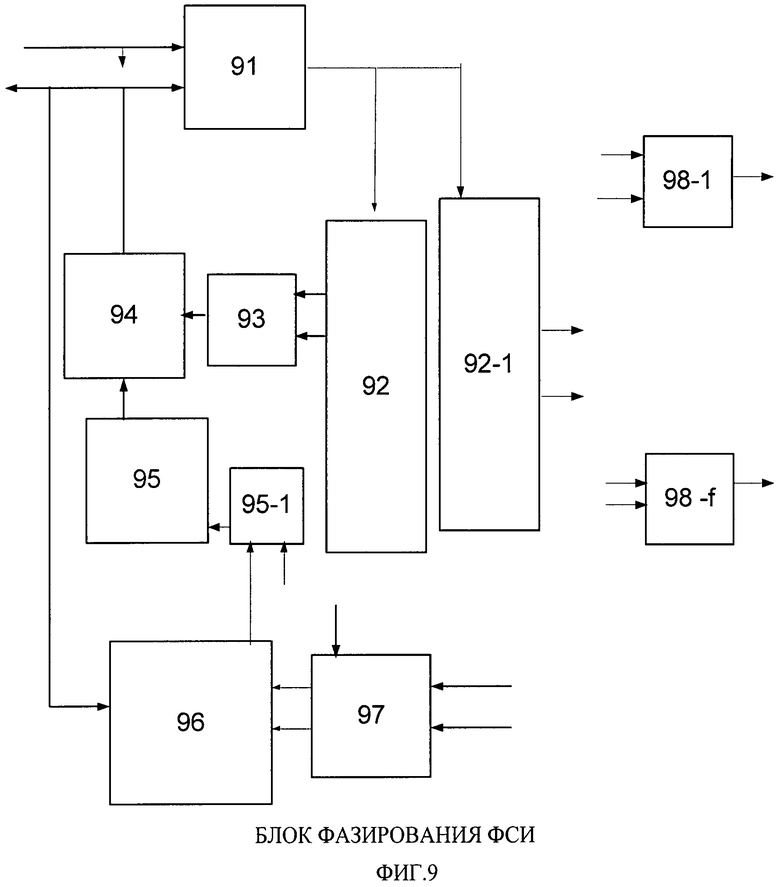

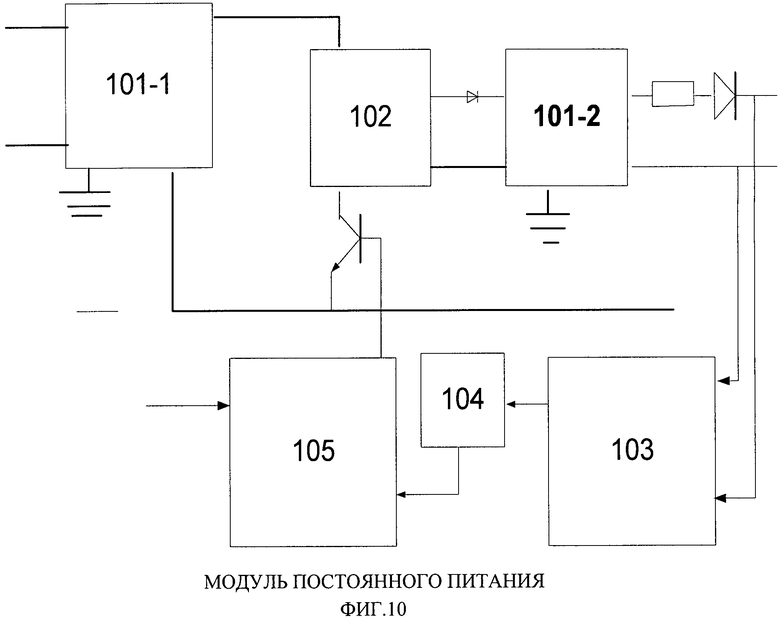

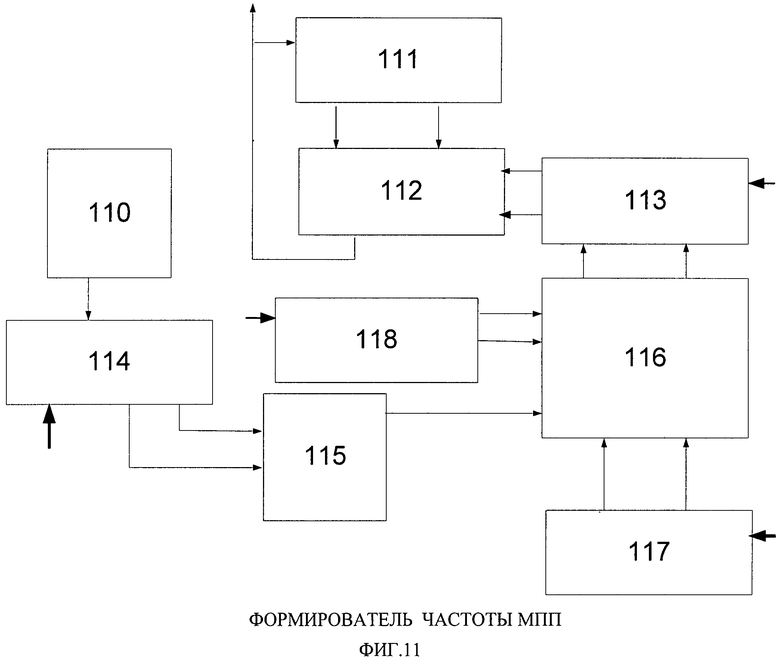

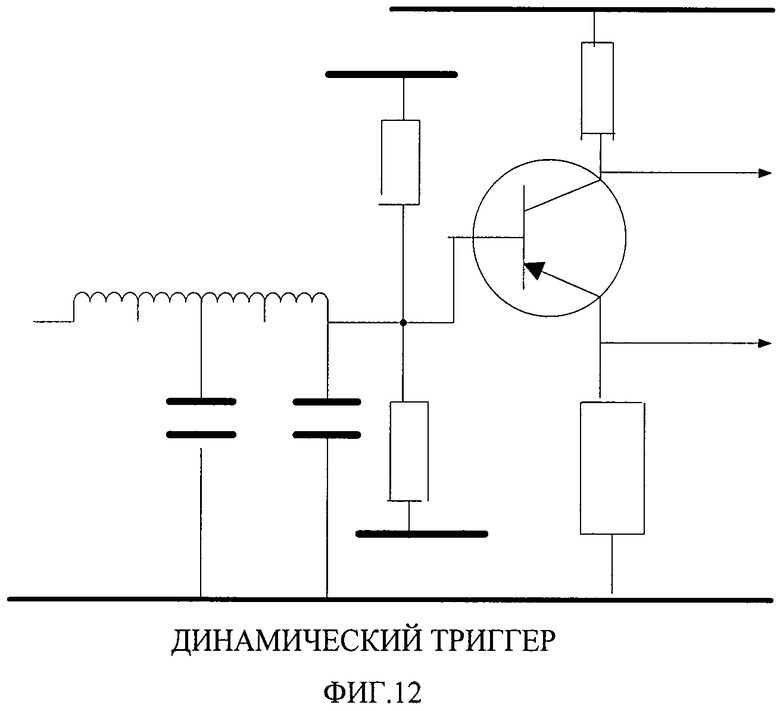

На фигурах с 1 по 12 приведен состав комплекса и входящих в него компонентов, блоков, узлов и элементов. На фигуре 1 приведен состав комплекса. Цифрой 1 обозначена моделирующая ПЭВМ, а цифрой 1-1 ее устройство отображения. Цифрой 2 обозначены имитаторы, цифрой 3 - технологическая БВС. Цифрой 4 обозначен ПУК, цифрой 5 - управляющая ЭВМ. Цифрой 6 обозначен синхронизатор, цифрой 7 - регистратор и цифрой 8 обозначен управляемый источник питания. На фигуре 2 приведена структура БВС. Здесь цифрой 21 обозначен системный модуль. Цифрами с 22-1 по 22-к обозначены процессоры, а цифрами с 23-1 по 23-к обозначены их локальные запоминающие устройства. Цифрами 24-1, 24-2 и 24-3 обозначены соответственно СВУ ПИН, ACH и СВУ ПОИ, цифрой 25 обозначено системное запоминающее устройство, а цифрой 26 обозначен перестраиваемый ФСИ. На фигуре 3 приведено СВУ ПИН, где цифрой 31 обозначен процессор обмена, цифрой 32 - запоминающее устройство ПИН. Цифрой 33 обозначен буферный регистр, цифрой 34 - формирователь синхроимпульсов ПИН. Цифрами с 35-1 по 35-n обозначены умножители, цифрой 36 - сумматор и цифрой 37 обозначен блок связи по магистрали. На фигуре 4 приведен пульт управления. Здесь цифрой 40 обозначен триггер останова, цифрой 41 обозначен регистр адреса, цифрой 42 - контрольный регистр адреса. Цифрой 43 обозначена первая схема сравнения. Цифрой 44 обозначен счетчик событий, цифрой 45 - регистр номера цикла, цифрой 46 обозначена вторая схема сравнения, цифрой 47 обозначен счетчик тактов и цифрой 48 обозначен элемент ИЛИ. На фигуре 4-1 приведено СВУ ПОИ, где цифрой 411 обозначен управляющий микропроцессор, цифрой 412 - обрабатывающее запоминающее устройство. Цифрами с 413-1 по 413-к обозначены вычислительные микропроцессоры, цифрой 414 - блок микропрограммного управления. На фигуре 5 приведен имитатор ПИН. Здесь цифрой 50 обозначен блок связи. Цифрой 51 обозначен формирователь частоты канала линейного ускорения и цифрами 52-1, 52-2 и 52-3 обозначены формирователи частоты каналов углового ускорения. На фигуре 5-1 приведен формирователь частоты имитатора ПИН. На этой фигуре цифрой 511 обозначена группа последовательно включенных инверторов, цифрой 512 - первый мультиплексор, цифрой 513 обозначен первый счетчик частоты, цифрой 514 - первая схема сравнения и цифрами 515 и 516 обозначены соответственно первый счетчик кода частоты и первый регистр кода частоты. На фигуре 5-2 показан имитатор датчика времени, где цифрой 521 обозначен таймерный генератор, цифрой 522 - таймерный счетчик и цифрой 523 обозначен таймерный регистр периода. На фигуре 6 приведен имитатор ПОИ, где цифрой 60 обозначено устройство связи. Цифрами с 61-1 по 61-к обозначены блоки памяти и цифрами от 62-1 до 62-к обозначены приемно-передающие устройства. На фигуре 6-1 приведен синхронизатор, где цифрой 61 обозначен синхронизаторный генератор. Цифрами с 611-1 по 611-n обозначены шины переноса синхронизирующих счетчиков, цифрой 612 - синхронизирующий дешифратор, цифрой 613 - регистр кода интервалов, цифрой 614 - формирователь трех управляющих сигналов. На фигуре 7 приведен регистратор. Здесь цифрой 71 обозначен высокочастотный генератор импульсов, цифрой 72 - регистр сдвига, цифрой 73 - триггеры регистрирующих регистров, цифрой 74 обозначено регистрирующее ЗУ и цифрой 75 обозначен счетчик адреса. На фигуре 8 приведен перестраиваемый формирователь синхроимпульсов, где цифрами 81-1, 81-2 и 81-3 обозначены соответственно первый, второй и третий генераторы импульсов, цифрами 82-1, 82-2 и 82-3 обозначены соответственно первый, второй и третий блоки фазирования и цифрой 83 обозначен блок мажоритации. На фигуре 9 приведен блок фазирования ФСИ, цифрой 91 обозначен логический элемент, цифрой 92 - динамический счетчик, цифрой 92-1 - сдвиговый регистр, цифрой 93 - фазирующий дешифратор, цифрой 94 - триггер приостанова, цифрой 95 - триггер пуска, цифрой 95-1 - элемент И, цифрой 96 - мажоритарный элемент, цифрой 97 - триггер привязки. Цифрами с 98-1 по 98-f обозначены триггеры формирователя. На фигуре 10 приведен модуль постоянного питания, где цифрами 101-1 и 101-2 обозначены соответственно входной фильтр и выходной фильтр нижних частот, цифрой 102 обозначен трансформатор, цифрой 103 - преобразователь напряжения в частоту, цифрой 104 обозначен элемент развязки и цифрой 105 обозначен формирователь частоты. На фигуре 11 приведен формирователь частоты МПП. Здесь цифрой 110 обозначен задающий генератор, цифрой 111 - группа инверторов, цифрой 112 обозначен второй мультиплексор, цифрой 113 - второй счетчик кода частоты, цифрой 114 обозначен счетчик интервала, цифрой 115 - интервальный дешифратор, цифрой 116 обозначена вторая схема сравнения, цифрой 117 - второй регистр кода частоты и цифрой 118 обозначен второй счетчик частоты. На фигуре 12 приведена схема динамического триггера.

Комплекс может быть реализован следующим образом. В качестве моделирующей и управляющей ЭВМ можно использовать персональные ЭВМ типа IBM PC со встроенными платами расширения. В качестве процессорных элементов БВС и имитаторов используются БИС серий 1867, а для запоминающих устройств БИС серий 1537 и 1620. Формирователи синхроимпульсов реализуются на основе БИС 1825 ВБ1, дополненной БИС на основе базовых матричных кристаллов серий 1516 и 1517 или 1537 ХМ2. Преобразователи напряжения в частоту могут быть реализованы на БИС ADFC32 фирмы Analog Devices или ее аналога, гальваническая развязка реализуется на основе оптрона 249 ЛП5 или планарного трансформатора. Остальные узлы источника питания и динамический триггер реализуются на дискретных элементах (диодах-транзисторах, конденсаторах и резисторах).

Комплекс работает следующим образом.

Перед началом отладки программ из моделирующей ЭВМ в запоминающие устройства и регистры имитаторов ПИН и ПОИ загружаются массивы заранее рассчитанной информации, соответствующие работе системы управления в отрабатываемом режиме. В управляющие регистры имитаторов ПИН заносятся коды, задающие номиналы выходных частот. В пульт управления посылается адрес, на котором требуется провести остановку работы программ и списать информацию для анализа. Задается также номер цикла, в котором нужно сделать остановку по заданному адресу, или код времени, по истечении которого также следует сделать остановку. В процессе проведения отладки ПО информация с технологических выходов БВС фиксируется в регистраторе, из которого считывается управляющей ЭВМ для анализа оператором. После завершения анализа по заданию оператора в пульте управления выключается триггер останова, формирователь синхроимпульсов БВС начинает работу, и программы продолжают выполняться без нарушения реального времени. Наличие в комплексе моделирующей ЭВМ обеспечивает подготовку необходимых имитационных массивов для подсистемы обработки изображений и кодов управления частотой имитаторов подсистемы инерциальной навигации. Все это, сохраняя основные достоинства прототипа, т.е. получение диагностической информации без внесения технологических вставок в штатные программы и обеспечения полной повторяемости хода программы от включения к включению, повышает оперативность отладки за счет получения большого объема диагностических данных из регистратора, а также имитирующей и контрольной информации в данном комплексе без задействования дополнительных стендов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| КОМПЛЕКС ОТЛАДКИ | 2010 |

|

RU2448363C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

Изобретение относится к вычислительной технике, а именно к комплексу отработки аппаратуры и программ управляющих вычислительных машин. Технический результат - повышение эффективности отладки управляющих вычислительных машин. Моделирующий комплекс отладки аппаратуры и программ, содержащий моделирующую ЭВМ, к которой подключены имитаторы входной информации, подключенные выходами к отрабатываемой бортовой вычислительной системе, пульт управления, подключенный к управляющей ЭВМ, устройство отображения информации моделирующей ЭВМ, управляемый источник питания, имитатор подсистемы спутниковой навигации, имитатор подсистемы инерциальной навигации, имитатор подсистемы обработки изображений, имитатор датчика времени, синхронизатор и регистратор, синхронизирующий вход которого подключен к выходу синхронизатора, а входы подключены к технологическим шинам отрабатываемой бортовой вычислительной системы и выходным шинам имитаторов, а управляющий вход - к выходу останова пульта управления, который также подключен к входу останова отрабатываемой бортовой вычислительной системы, входу прерывания моделирующей ЭВМ общего назначения и входу останова имитатора датчика времени. 18 з.п. ф-лы, 16 ил.

1. Моделирующий комплекс отладки аппаратуры и программ, содержащий моделирующую ЭВМ, к которой подключены имитаторы входной информации, подключенные выходами к отрабатываемой бортовой вычислительной системе, пульт управления, подключенный к управляющей ЭВМ, отличающийся тем, что в его состав включены устройство отображения информации моделирующей ЭВМ, управляемый источник питания, имитатор подсистемы спутниковой навигации, имитатор подсистемы инерциальной навигации, имитатор подсистемы обработки изображений, имитатор датчика времени, синхронизатор и регистратор, синхронизирующий вход которого подключен к выходу синхронизатора, а входы подключены к технологическим шинам отрабатываемой бортовой вычислительной системы и выходным шинам имитаторов, а управляющий вход - к выходу останова пульта управления, который также подключен к входу останова отрабатываемой бортовой вычислительной системы, входу прерывания моделирующей ЭВМ общего назначения и входу останова имитатора датчика времени.

2. Комплекс по п.1, отличающийся тем, что имитатор подсистемы инерциальной навигации содержит блок формирования частоты канала линейного ускорения и три блока формирования частот каналов угловых скоростей, каждый из которых соответствует одному из углов пространственной ориентации, при этом установочный вход каждого из формирователей подключен к соответствующему выходу блока связи, вход-выход которого является входом-выходом имитатора, а выходы формирователей подключены к шине связи имитатора с отрабатываемой системой.

3. Комплекс по п.1, отличающийся тем, что имитатор подсистемы обработки изображений содержит k блоков памяти, по одному на канал, вход каждого из которых подключен к выходу блока связи с моделирующей ЭВМ, а выходы через свои приемно-передающие устройства подключены к шине связи с отрабатываемой вычислительной системой и входами регистратора.

4. Комплекс по п.1, отличающийся тем, что имитатор датчика времени содержит таймерный задающий генератор, подключенный выходом к счетному входу таймерного счетчика, запрещающий вход которого является входом останова имитатора, выход является выходом имитатора, а установочные входы подключены к выходам таймерного регистра, установочный вход которого является входом имитатора, подключенным к моделирующей ЭВМ.

5. Комплекс по п.1, отличающийся тем, что имитатор подсистемы спутниковой навигации содержит модуль памяти, подключенный входом к шине связи с моделирующей ЭВМ, а выходом - к шине связи с отрабатываемой вычислительной системой и регистратором.

6. Комплекс по п.1, отличающийся тем, что синхронизатор содержит синхронизаторный генератор, подключенный выходом к формирователю трех управляющих сигналов, выходы которого являются управляющими выходами синхронизатора, и к входам первого, второго и третьего последовательно соединенных между собой шинами переноса синхронизирующих счетчиков, выходы которых подключены к входу синхронизирующего дешифратора, выход которого является выходом синхронизатора, а управляющий вход подключен к выходам регистра кода интервала, вход которого является установочным входом синхронизатора.

7. Комплекс по п.1, отличающийся тем, что регистратор содержит высокочастотный генератор импульсов, подключенный выходом к входу регистра сдвига, запрещающий вход которого является входом останова регистратора, первый выход этого регистра подключен к счетному входу счетчика адреса, остальные выходы подключены к стробирующим входам триггеров регистрирующих регистров, выходы которых подключены к входу регистрирующего запоминающего устройства, к адресным входам которого подключены выходы счетчика адреса, вход-выход которого и вход-выход запоминающего устройства подключены к шине связи регистратора с управляющей ЭВМ.

8. Комплекс по п.1, отличающийся тем, что отрабатываемая вычислительная система содержит системный модуль, к которому через резервированную системную магистраль подключены системное запоминающее устройство, подсистема спутниковой навигации с встроенным вычислителем подсистемы, подсистема инерциальной навигации с встроенным вычислителем подсистемы, подсистема обработки изображений с встроенным вычислителем подсистемы и m модулями связи по последовательным магистралям, а также управляемый формирователь синхроимпульсов, выходы которого подключены к остальным модулям системы, а его вход останова является одноименным входом системы, которая, кроме того, содержит k вычислительных модулей, процессоры которых подключены к системной магистрали, а к каждому из них подключено собственное локальное запоминающее устройство, при этом системная магистраль и шины связи процессоров встроенных в подсистемы вычислителей с их запоминающими устройствами поступают на внешние технологические связи вычислительной системы.

9. Комплекс по п.1, отличающийся тем, что источник питания содержит модуль постоянного питания, установочный вход которого является одноименным входом источника, подключенным к управляющей ЭВМ, и модуль импульсного питания, три управляющих входа которого являются входами источника, подключенными к соответствующим выходам синхронизатора.

10. Комплекс по п.1, отличающийся тем, что пульт управления содержит регистр адреса, подключенный входом к технологическим выходам вычислительной системы, а выходом - к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы контрольного регистра адреса, подключенного входом к управляющей ЭВМ, а выход первой схемы сравнения подключен к входу счетчика событий, выходы которого подключены к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы регистра номера цикла, подключенного входом к управляющей ЭВМ, а выход второй схемы сравнения подключен к первому входу элемента ИЛИ, ко второму входу которой подключен выход счетчика тактов, подключенного входом к тактовому выходу вычислительной системы, при этом выход элемента ИЛИ подключен к запускающему входу триггера останова, сбрасывающий вход которого подключен к управляющей ЭВМ, а выход является выходом останова пульта.

11. Комплекс по п.8, отличающийся тем, что встроенный вычислитель подсистемы обработки изображений содержит управляющий микропроцессор, к которому через первую магистраль подключены k вычислительных микропроцессоров, подключенных через вторую магистраль к обрабатывающему запоминающему устройству, подключенному через двунаправленную связь к управляющему микропроцессору, вход-выход которого является входом-выходом вычислителя.

12. Комплекс по п.8, отличающийся тем, что встроенный вычислитель подсистемы инерциальной навигации содержит микропроцессор с универсальной системой команд, к которому через двунаправленную связь подключено первое системное запоминающее устройство, подключенное, кроме того, к технологическому выходу вычислителя, частотные входы которого являются частотными входами микропроцессора, выход которого через регистр подключен к установочному входу инерциального блока микропрограммного управления и первым входам n матричных умножителей, последовательно соединенных шинами переноса, а выходами подключенными к входам сумматора, выходы которого подключены к входам первого блока связи, вход-выход которого объединен с входом-выходом микропроцессора и является входом-выходом вычислителя, подключенным к системной магистрате, причем выходы инерциального блока микропрограммного управления, содержащего останавливаемый формирователь синхроимпульсов, подключены ко всем блокам вычислителя, а его вход останова является одноименным входом вычислителя.

13. Комплекс по п.8, отличающийся тем, что формирователь синхроимпульсов содержит три перестраиваемых генератора импульсов, управляющие входы которых являются входом формирователя, а выход каждого из них подключен к входу своего блока фазирования, входы останова которых являются одноименным входом формирователя и вычислительной системы, фазирующий выход каждого из блоков подключен к фазирующим входам двух других блоков, а синхронизирующие выходы подключены к входам блока мажоритации, выходы которого являются выходами формирователя.

14. Комплекс по п.9, отличающийся тем, что модуль постоянного питания содержит последовательно соединенные входной фильтр, трансформатор с включенным в первичную обмотку транзистором прерывателем, выпрямительный диод и выходной фильтр, к выходу которого подключены последовательно соединенные резистор и диод, выход которого является выходом модуля, причем выходные шины модуля подключены к входу преобразователя напряжения в частоту, выход которого через элемент развязки подключен к входу формирователя частоты, установочный вход которого является одноименным входом модуля, а выход подключен к базе транзистора прерывателя.

15. Комплекс по п.9, отличающийся тем, что модуль импульсного питания содержит три параллельно соединенные ветви, каждая из которых содержит два последовательно соединенных полевых транзистора, истоки первых из которых объединены и подключены к шине силового питания, а объединенные стоки вторых транзисторов являются выходом модуля, при этом три управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

16. Комплекс по п.13, отличающийся тем, что перестраиваемый генератор содержит группу последовательно соединенных инверторов, выходы которых подключены к входам генераторного мультиплексора, выход которого подключен к входам первого инвертора и генераторного счетчика частоты, выходы которого подключены к первым входам генераторной схемы сравнения, ко вторым входам которой подключены выходы генераторного регистра кода частоты, а инкрементный и декрементный выходы схемы подключены к одноименным входам генераторного счетчика кода частоты, выходы которого подключены к управляющим входам генераторного мультиплексора, а установочный вход этого счетчика и установочный вход генераторного регистра кода частоты являются управляющим входом генератора.

17. Комплекс по п.13, отличающийся тем, что блок фазирования содержит логический элемент, первый вход которого является входом блока, а выход подключен к входам сдвигового регистра и динамического счетчика, выходы которого подключены к входам фазирующего дешифратора, подключенного выходом к запускающему входу триггера приостанова, выход которого является фазирующим выходом блока и подключен ко второму входу логического элемента и первому входу мажоритарного элемента, подключенного выходом к первому входу элемента И, второй вход которого является входом останова блока и формирователя, а выход подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера приостанова, а ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, стробовый вход которых объединен с первым входом логического элемента, а входы являются фазирующими входами блока.

18. Комплекс по п.14, отличающийся тем, что формирователь частоты содержит несколько последовательно соединенных инверторов, выходы которых подключены к входам формирующего мультиплексора, выход которого подключен к входу первого инвертора и является выходом формирователя, вход которого подключен к входу формирующего счетчика частоты, выходы которого подключены к первым входам формирующей схемы сравнения, ко вторым входам которой подключены выходы формирующего регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам формирующего счетчика кода частоты, выходы которого подключены к входам формирующего мультиплексора, а его установочный вход и установочный вход формирующего регистра кода частоты являются управляющим входом формирователя.

19. Комплекс по п.17, отличающийся тем, что динамический триггер реализован как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя подключена являющаяся элементом памяти LC цепь, индуктивность которой имеет две обмотки: рабочую и намотанную поверх нее встречно-компенсационную, концы которой закорочены.

| КОМПЛЕКС ОТЛАДКИ | 2010 |

|

RU2448363C1 |

| СПОСОБ ПРОИЗВОДСТВА И СОПРОВОЖДЕНИЯ ИНДИВИДУАЛЬНОГО ПРОГРАММНОГО ПРОДУКТА - ТЕХНОЛОГИЯ "ESC-M" | 2002 |

|

RU2195016C2 |

| Способ осушения верхних сдоев торфяной залежи | 1947 |

|

SU77061A1 |

| Агрегат для непрерывного крашения, промывки и сушки тканей в расправку | 1957 |

|

SU113035A1 |

| Экономайзер | 0 |

|

SU94A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2014-05-20—Публикация

2013-01-29—Подача