Изобретение относится к вычислительной технике и может быть использовано для создания вычислительных систем, к которым предъявляются повышенные требования по надежности при длительной работе в неблагоприятных внешних условиях (внешние механические, электромагнитные и ионизирующие воздействия), например при работе в космосе.

Известна трехканальная вычислительная система (См. АС №1156273), содержащая в каждом канале внешнее устройство и вычислительное устройство, информационный выход которого подключен к первому входу первого мажоритарного элемента и к первому входу первого элемента сравнения всех каналов. Второй вход первого элемента сравнения соединен с выходом первого мажоритарного элемента и с входом внешнего устройства, выход которого подключен к первому информационному входу второго мажоритарного элемента всех каналов, второй и третий информационные входы которого соединены соответственно со вторым и третьим информационными входами вторых мажоритарных элементов других каналов и с выходами внешних устройств соответственно. Выход второго мажоритарного элемента подключен к первому входу второго элемента сравнения и к первому входу вычислительного устройства. Второй вход второго элемента сравнения соединен с первым входом второго мажоритарного элемента, а выход - с выводом связи.

В каждом канале содержится также регистр номера канала, четыре блока анализа, группа элементов И, контрольный регистр и элемент ИЛИ, выход которого подключен ко входу прерывания вычислительного устройства. Первый вход контрольного регистра соединен с выходом последовательной передачи информации вычислительного устройства.

Входы контрольного регистра соединены с выходами группы элементов И. Вторые выходы соединены со входами элемента ИЛИ. Кроме того, каждый канал содержит элемент НЕ, а каждый блок анализа выполнен в виде дешифратора, связанного входами с выходами элементов сравнения.

Это известное устройство благодаря установке мажоритарных элементов в выходных информационных шинах вычислителей обеспечивает нейтрализацию неисправности, возникающей в одном из каналов при правильной работе двух других каналов. Кроме того, благодаря введению схем сравнения, подключенных к связям внешних устройств, обеспечивается обнаружение неправильной работы одного из каналов по отличию его информации от двух других, что позволяет диагностировать отказы внешних устройств путем анализа состояний контрольного регистра вычислительным устройством. Эти свойства являются достаточно положительными. Особенно важным является нейтрализация первой неисправности, возникающей в одном из каналов вычислительного устройства.

В то же время после возникновения неисправности в одном из каналов надежность дальнейшей работы системы резко снижается, так как возникновение неисправности в любом из двух оставшихся исправными вычислительных устройств приводит к полной неработоспособности системы. Это происходит потому, что интенсивность отказа в двух каналах в два раза больше, чем у одноканального вычислителя. Целесообразно максимально полно использовать имеющуюся избыточность в виде двух дополнительно введенных каналов для сохранения работоспособности системы после возникновения второй неисправности.

Задача сохранения работоспособности системы при возникновении двух неисправностей в системе частично решена в резервированном вычислительном устройстве (См. АС №1200292). В данном устройстве для повышения надежности между блоками памяти и процессора введен коммутатор, переключающий блоки по сигналам встроенных средств оперативного контроля.

Общим недостатком известных вычислительных устройств является то, что как для работы схем мажоритации, так и для работы коммутатора, переключающего блоки в процессе работы, требуется синхронная и синфазная работа всех каналов устройства, что обеспечивается наличием единого генератора синхроимпульсов, кроме того, использование только встроенных в модули средств контроля не обеспечивает требуемую вероятность обнаружения отказов.

При такой реализации резервирования отказ общего генератора приводит к отказу устройства в целом. Кроме того, наличие временного рассогласования одноименных сигналов разных каналов резервированного устройства требует постоянного снижения быстродействия с целью учета межканальных рассогласований, вызванных отличиями задержек элементов разных каналов. Более того в процессе работы в блоках вычислительного устройства под влиянием температуры и особенно из-за воздействия внешнего ионизирующего излучения, например космического пространства, происходит деградация параметров комплектующих элементов и особенно широко применяемых КИОП БИС, учесть которую при проектировании невозможно.

С целью устранения отмеченных недостатков в части критичности отказа единого генератора синхроимпульсов, а также обеспечения максимально возможного быстродействия вычислительного устройства на каждом интервале времени работы в основном режиме

Предлагается вычислительная система, содержащая несколько (К) модулей процессоров (ПР), несколько (L) модулей запоминающих устройств (ЗУ) и несколько (М) модулей устройств обмена (УО) для обмена с периферийными подсистемами последовательным кодом.

Для организации взаимодействия процессоры связаны с ЗУ и УО через коммутаторы.

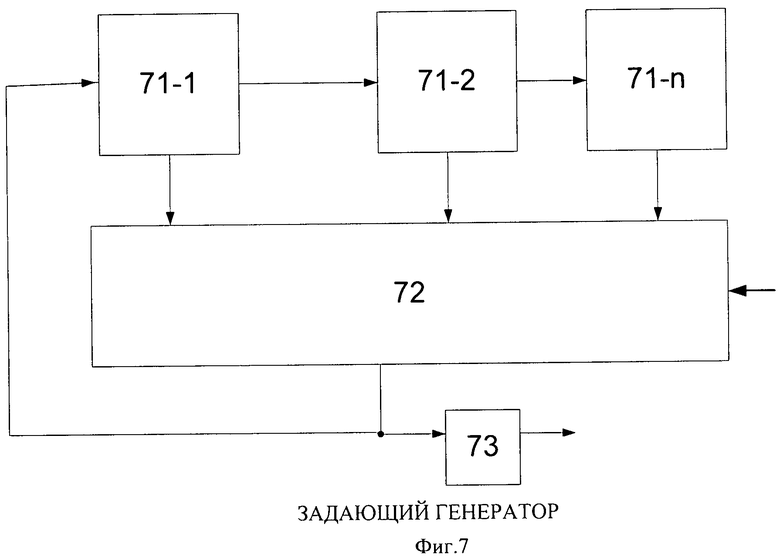

На фиг.1 изображена структурная схема предлагаемой системы, цифрами от 1-1 до 1-К обозначены процессоры от ПР №1 до ПР №К соответственно, цифрами от 2-1 до 2-L обозначены запоминающие устройства от ЗУ №1 до ЗУ №L соответственно. Цифрами от 3-1 до 3-М обозначены устройства обмена. Цифрами 4-1 4-2 и 4-3 соответственно обозначены первая, и вторая, и третья группы коммутаторов (ГК). Цифрой 5 обозначен блок контроля и управления (БКУ). Цифрой 6 обозначен формирователь синхроимпульсов (ФСИ).

Первые выходы и первые входы процессоров подключены соответственно к первой группе входов и выходов первой группы коммутаторов, ко вторым группам входов и выходов которой подключены выходы и входы запоминающих устройств, а вторые выходы и вторые входы процессоров подключены соответственно к первым входам и первым выходам второй группы коммутаторов, вторые входы и выходы которой подключены к выходам и входам УО, а их последовательный и синхронизирующие выходы подключены к информационному и синхронизирующему входам третьей группы коммутаторов, одноименные выходы которой являются соответствующими выходами системы, а и входам устройств обмена (УО). Информационный выход синхронизирующий выход УО являются одноименными входом системы.

Информационные и сигнальные контрольные выходы запоминающих устройств, процессоров и устройств обмена подключены к соответствующим входам БКУ, у которого первая, вторая и третья группы управляющих выходов подключены соответственно к управляющим входам первой, второй и третьей групп коммутаторов. Синхронизирующие выходы ФСИ подключены к одноименным входам процессоров, ЗУ, УО иБКУ.

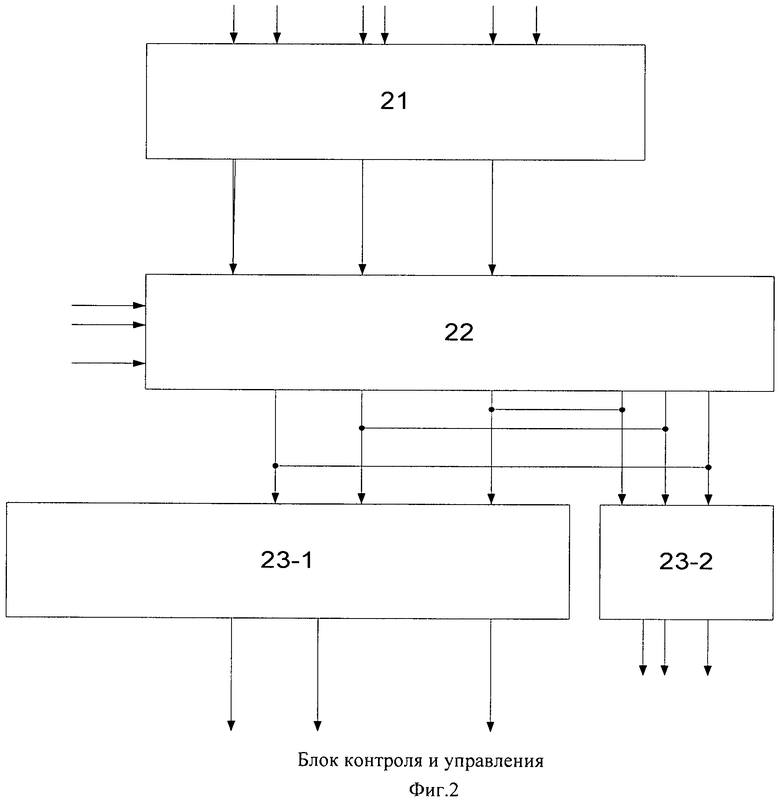

На фиг.2 изображена структура БКУ, где цифрой 21 обозначен регистр состояния, фиксирующий сигналы контрольных устройств модулей, подключенных к его входам. Цифрой 22 обозначена группа элементов (И, ИЛИ, НЕ), вырабатывающая сигналы управления коммутаторами и частой, которые фиксируются в регистре управления структурой 23-1 и регистре управления частотой 23-2, выходы которых являются выходами БКУ.

БКУ использует как сигнальные контрольные выходы встроенного аппаратного контроля модулей (например mod 3), так и информационные контрольные выходы модулей, поступающие на внутренние схемы сравнения информации модулей между собой, при этом при контроле процессоров используются только 2 младших и знаковый разряды, что, как показывают результаты моделирования, обеспечивает достаточно высокую вероятность обнаружения отказа (не менее 0,8), вполне достаточную для практического применения. Контроль ЗУ по mod 3 также вполне достаточен, а контроль УО ведется сравнением на выдаваемом последовательном коде, что не требует заметных аппаратурных затрат. Таким образом, сочетание встроенных в модули средств контроля и сравнения информации модулей между собой обеспечивает необходимую для практических применений обнаруживающую способность.

При формировании признака неисправности какого-либо модуля используются сигналы встроенных в модули контрольных устройств, которые обозначим как КУi, и сигналы, вырабатываемые схемами сравнения контрольной информации модулей, которые обозначим через ССi, тогда общий сигнал неисправности модуля Hi, который фиксируется в регистрах управления 23-1 и 23-2, будет сформирован по логике Hi=КУi∧CCi,

где CCi=Иi∧(Иi-1∧Иi+1)∨(jИi∧(Иi-1∧Иi+1)). При этом Иj, Иj-1 и Иj+1 соответствуют прямым значениям информации модуля данного канала, предшествующего и последующего, а при наличии символа j впереди - их инверсным значениям.

После записи информации в регистр управления 23-1 в коммутаторах происходит замещение сигналов неисправного модуля сигналами предшествующего, и в регистре 23-2 формируется соответствующий код понижения частоты.

Причем при наличии признаков неисправности у идентичного модуля предшествующего канала сохраняется подключение информации собственного модуля и работа на номинальной частоте, что позволяет избежать «тупиковой ситуации» при неопределенности принятии решения, поскольку выбор надо делать из модулей, забракованных аппаратурой контроля. Это в некоторых случаях с учетом конечной вероятности обнаружения отказов может привести к ложному забракованию и «развалу» потенциально работоспособной системы.

На фиг.3 изображена структурная схема ГК. ГК содержит n двухвходовых мультиплексоров, обозначенных цифрами от 31-1 до 31-k. Мультиплексоры соединены таким образом, что их первый информационный вход подключен к выходу функционального модуля (ПР, ЗУ, УО), а второй вход объединен с выходом соседнего мультиплексора, являющегося выходом ГК, образуя при этом включение по кольцу, при котором информационный выход своего блока можно обозначить как Иi, предыдущего через Иi и последующего через Иi+1. Такое включение позволяет наращивать количество модулей только за счет введения связей. При этом мультиплексоры конструктивно размещаются в модуле процессора.

Каждый мультиплексор управляющим входом подключен к соответствующему выходу блока контроля и управления и в зависимости от сигнала на этом входе передает на выход информацию или своего блока, или от соседнего мультиплексора.

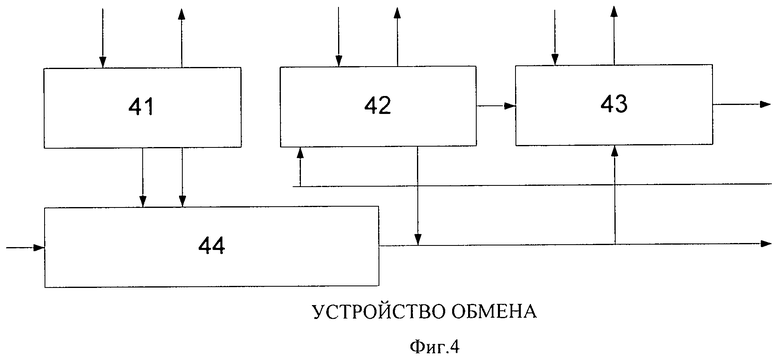

На фиг.4 изображена структурная схема устройства обмена, где цифрой 41 обозначен регистр адреса подсистемы, цифрой 42 - регистр данных, цифрой 43 обозначен регистр адреса абонента, а цифрой 44 - делитель частоты.

Параллельные входы регистров адреса подсистемы и абонента являются входами устройства. Выходы регистра адреса подсистемы подключены к входам делителя частоты, выход которого является синхронизирующим выходом устройства и подключен к синхронизирующим входам последовательно соединенных регистра данных и регистра адреса абонента, образующих сдвиговый регистр. При этом выход регистра адреса абонента является последовательным выходом устройства и системы, а вход регистра данных является последовательным входом устройства и системы. Это включение позволяет передать в одной посылке данные для внешней подсистемы и адрес абонента в ней, для которого эти данные предназначены. Передачей синхроимпульсов во внешнюю подсистему не только синхронизируется прием данных абонентом, но и сдвиг информации из его регистра, а также запись их в регистр данных УО. Такая организация обмена позволяет заметно сократить время передачи данных, но требует предварительного согласования порядка передачи данных, когда от абонента после приема очередного слова требуется запись следующего слова. Порядок может быть установлен посредством определения адресов абонента. Введение делителя частоты, управляемого кодом адреса подсистемы позволяет задать для каждой подсистемы частоту следования синхронизирующих импульсов, соответствующую быстродействию ее сдвигового регистра.

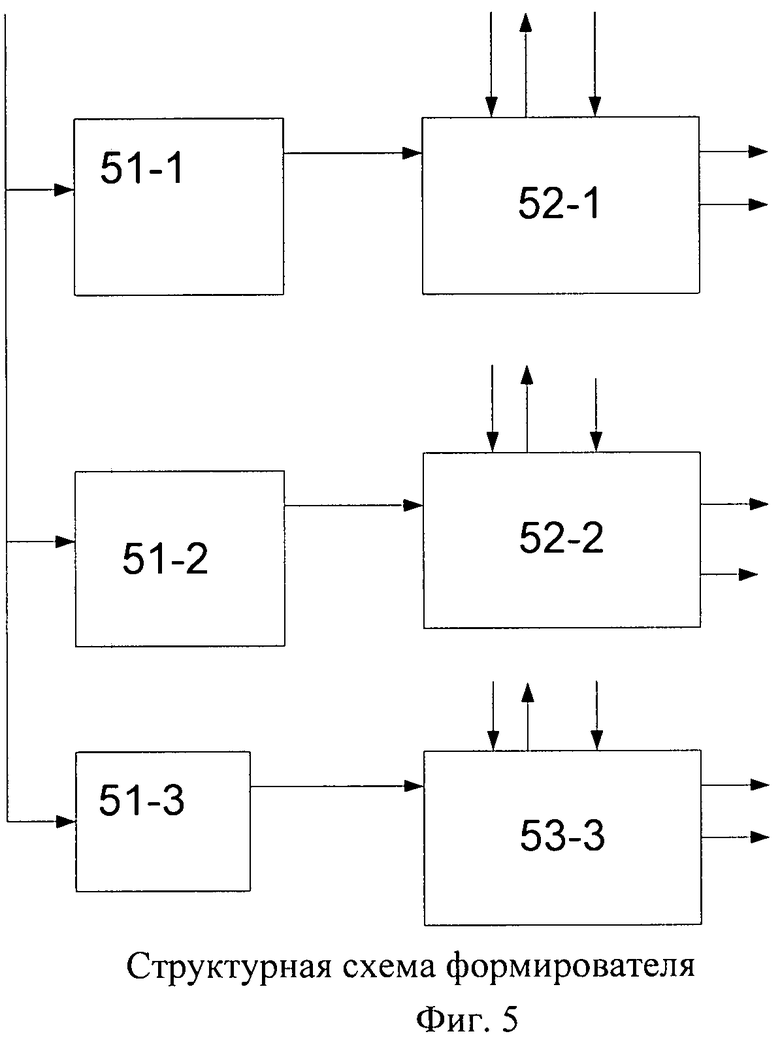

На фиг.5 изображена структурная схема формирователя синхроимпульсов, где цифрами 51-1, 51-2 и 51-3 обозначены первый, второй и третий задающие генераторы, цифрами 52-1, 52-2 и 52-3 обозначены первый, второй и третий блоки формирования (БФ).

Управляющие входы генераторов объединены между собой и являются одноименным входом формирователя, выходы генераторов подключены к входам одноименных БФ, фазирующий выход каждого из которых подключен к фазирующим входам двух других БФ, а синхронизирующие выходы БФ являются выходами формирователя синхроимпульсов.

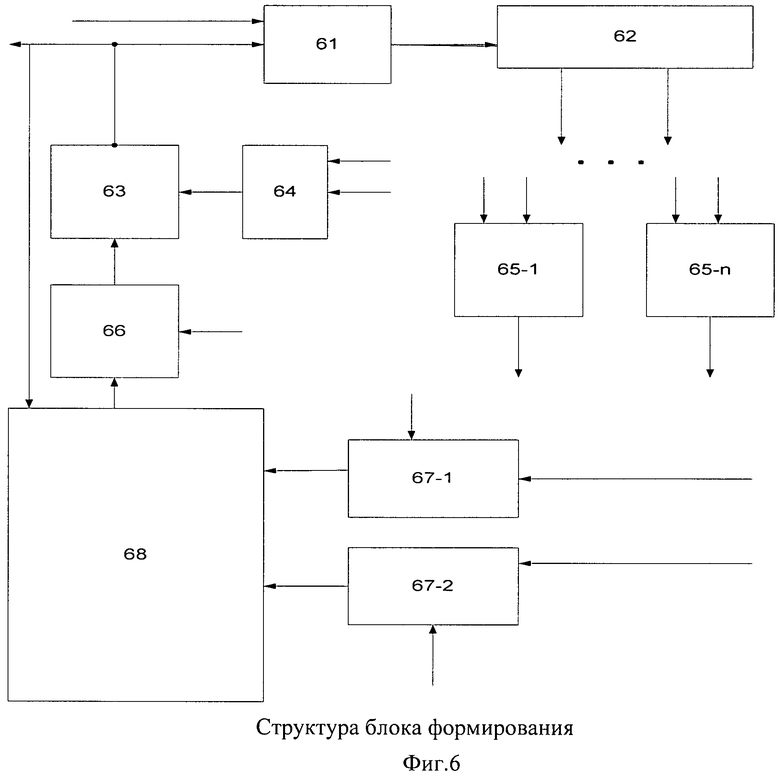

На фиг.6 изображен состав блока формирования, где цифрой 61 обозначен элемент И, на первый вход, являющийся входом БФ, подключен выход задающего генератора. Выход элемента И подключен к входу сдвигового регистра 62, выходы которого подключены к входам дешифратора 64, выход которого подключен к запускающему входу триггера «останова» (ТО), выход которого является фазирующим выходом БФ и подключен ко второму входу элемента И, и первому входу мажоритарного элемента 68, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу ТО. Кроме того, выходы сдвигового регистра 62 подключены к синхронизирующим входам триггера пуска 66, триггеров привязки 67-1 и 67-2, подключенных выходами ко второму и третьему входу мажоритарного элемента 68. Триггеры пуска 66 и привязки (67-1, 67-2) стробированы сигналом задающего генератора, для чего он заведен на их входы. Выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам n триггеров формирователей от 65-1 до 65-n, выходы которых являются выходами БФ и формирователя в целом. Такое построение системы синхронизации обеспечивает резервирование задающего генератора и фазирование выходных синхроимпульсов разных каналов с точностью до периода высокой частоты, которая может быть достаточно высокой (16-24 МГц), что вполне достаточно для синхронной и синфазной работы модулей разных каналов, так как реальное быстродействие современных цифровых элементов составляет около нескольких десятков наносекунд с разбросом около 10 процентов. Таким образом, несинфазность модулей разных каналов находится в пределах нестабильности быстродействия элементной базы, т.е. не приводит к снижению быстродействия вычислителя в целом, но обеспечивает нейтрализацию отказов задающего генератора.

Фазировка формирователей синхроимпульсов обеспечивается следующим образом.

В блоке формирования в регистре 62 происходит сдвиг импульсов задающего генератора, поступающих на регистр через элемент И. При определенном состоянии триггеров регистра, определяющего конец цикла формирования, срабатывает дешифратор 64, который включает триггер останова 63, сигнал которого запрещает поступление через элемент И 61 импульсов задающего генератора, в результате чего приостанавливается триггерами-формирователями 65-1 - 65-n формирование синхроимпульсов нового цикла.

На запускающие входы триггеров-формирователей подключены нечетные разряды сдвигового регистра, а на сбрасывающие - четные. Сигнал с триггера останова поступает как фазирующий сигнал на первый вход своего мажоритарного элемента 68 и в два других канала формирователя через триггеры привязки 67-1 и 67-2 на второй и третий входы их мажоритарных элементов. После окончания цикла в любом из двух других каналов срабатывают мажоритарные элементы всех каналов и везде включается триггер пуска 66, сбрасывающий триггер останова, который снимает запрет прохождения частоты на сдвиговый регистр, и начинается новый цикл формирования синхроимпульсов синфазно во всех каналах с точностью до периода высокой частоты, из-за стробировки запуска триггера пуска и триггеров привязки 67-1 и 67-2 сигналом задающего генератора.

В результате опережающий канал «притормаживается» и ждет второй, после чего начинают синфазно работать все формирователи. Со временем опережающие каналы могут меняться своим местом на временной шкале, и происходит сближение фаз.

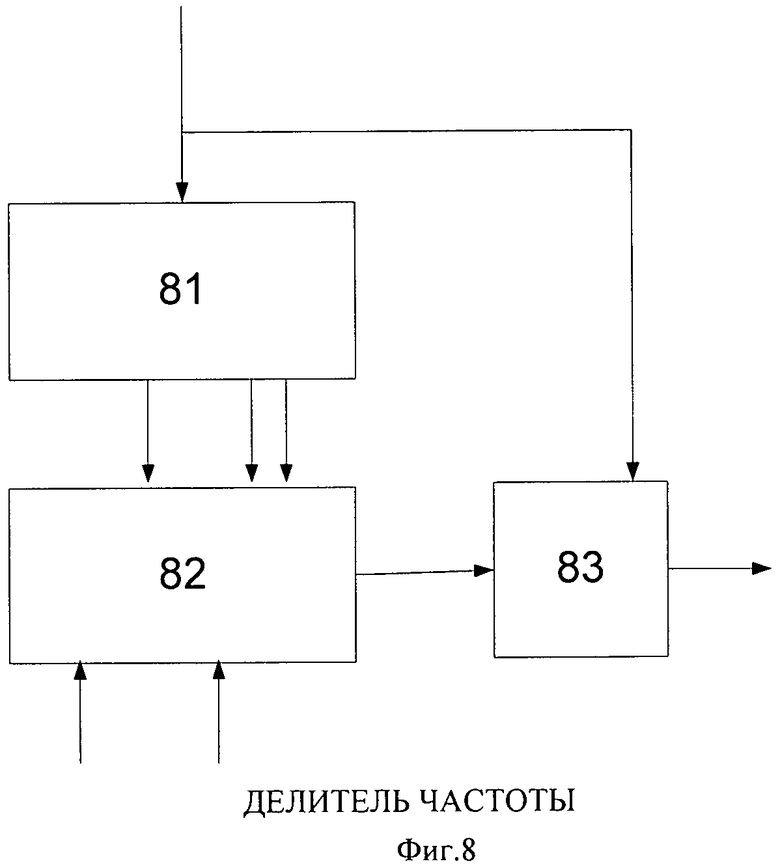

На фигуре 7 приведена схема задающего генератора. Его основу составляют n последовательно включенных инверторов от 71-1 до 71-n, выходы которых подключены к мультиплексору 72, вход управляющий вход которого является одноименным входом генератора, а выход подключен к входу первого инвертора 71-1 и буфера 73, выход которого является выходом генератора. Количество инверторов, включая мультиплексор, подобрано таким образом, чтобы возникла положительная обратная связь и возникла генерация с частотой определяемой временем прохождения сигнала по кольцу. Это время определяется количеством инверторов в кольце и их быстродействием. Меняя количество инверторов в кольце можно менять частоту, для чего используется мультиплексор, управляемый внешним кодом. Перестройка частоты (снижение в частности) используется в системе при переключении на резервный модуль из-за увеличения времени прохождения информации через мультиплексоры (21-1, 21-n), образующие коммутаторы 4-1 и 4-2. Так как понижение частоты производится только при возникновении отказа и переключении на резервный модуль, все основное время система работает с номинальным быстродействием.

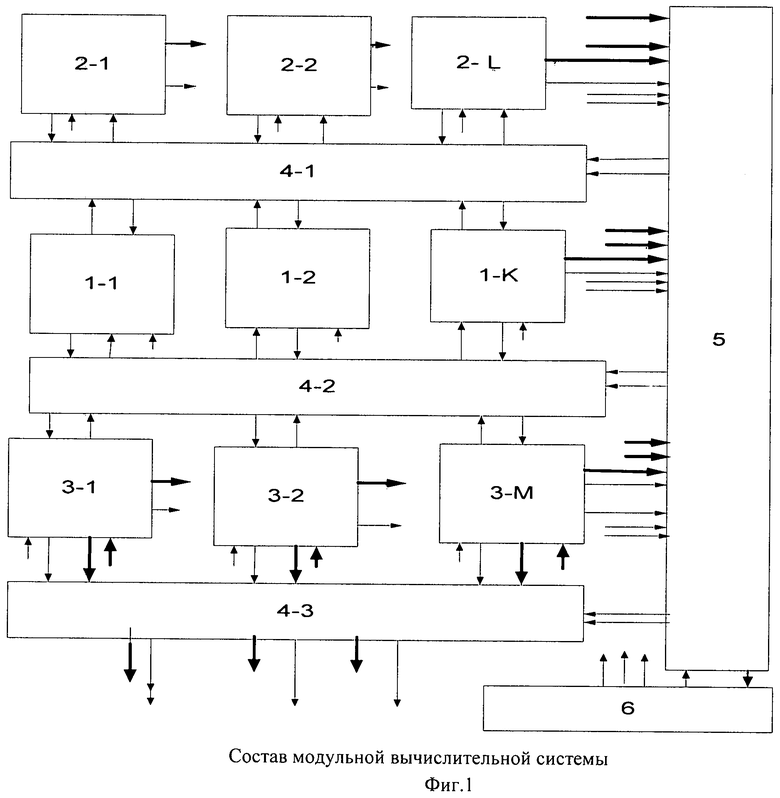

На фигуре 8 приведена структурная схема делителя частоты, который содержит счетчик 81, вход которого является входом делителя, на который поступают синхроимпульсы от ФСИ, а выходы счетчика подключены к дешифратору 82, управляемому кодом регистра адреса системы, сигнал с выхода дешифратора через триггер привязки 83, стробируемый входным синхроимпульсом, поступает на выход и является синхронизирующим сигналом для собственного сдвигового регистра, образованного регистрами данных 42 и адреса абонента 43, а также для внешней подсистемы.

Вычислительная система работает следующим образом.

После включения системы коммутаторы настроены таким образом, что ведется прямая передача данных между процессорами и соответствующими ему модулями ЗУ и УО, которые условно можно назвать модулями одного канала. При этом передача ведется на максимально допустимой номинальной частоте, так как информация на выход каждого мультиплексора поступает от модулей своего канала с минимальной задержкой на элементах коммутатора.

При возникновении отказа в одном из модулей какого-либо канала сигнал с его встроенных схем контроля поступает в блок контроля и правления или формируется в блоке по встроенной логике на основе сравнения информации модулей соседних каналов. По внутренней логике вырабатываются и записываются в регистры управления 23-1 и 23-2 сигналы управления, переключающие мультиплексоры на передачу данных от соседнего i-1-го канала. Так как при этом появляется дополнительная задержка, связанная с предварительным прохождением информации через мультиплексор соседнего канала в регистр 23-2 записывается код управления частотой задающих генераторов ФСИ. Код зависит от количества последовательно включенных коммутаторов и задает частоту, соответствующую настроенной конфигурации модулей.

Такая реализация системы позволяет сохранить работоспособность при возникновении отказов в общем блоке формирования синхроимпульсов, сохраняя их синхронность и синфазность. Дополнение внутренних схем контроля сравнением информации разных каналов повышает полноту контроля.

Таким образом предлагаемая система сохраняя все достоинства известных решений, устраняет их недостатки.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2444053C1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| КОМПЛЕКС ОТЛАДКИ | 2010 |

|

RU2448363C1 |

Изобретение относится к вычислительной технике и может использоваться при создании систем управления объектами ракетно-космической техники. Техническим результатом является повышение надежности и повышение быстродействия системы в основном режиме работы. Система содержит (К) модулей процессоров (ПР), (L) модулей запоминающих устройств (ЗУ), (М) модулей обмена (МО), блок контроля и управления (БКУ) и формирователь синхроимпульсов (ФСИ), а также три группы коммутаторов, предназначенные для связи модулей процессоров, модулей запоминающих устройств и модулей обмена. 7 з.п. ф-лы, 8 ил.

1. Вычислительная система, содержащая К модулей процессоров, L модулей запоминающих устройств и М модулей обмена, отличающаяся тем, что в ее состав введены первая и вторая группа коммутаторов, формирователь синхроимпульсов и блок контроля и управления, входы которого подключены к контрольным сигнальным и информационным выходам модулей, а выходы подключены к управляющим входам формирователя синхроимпульсов и управляющим входам всех групп коммутаторов, причем первые выходы и входы процессоров каждого канала подключены к входам и выходам первой группы входов и выходов первой группы коммутаторов, входы и выходы второй группы выходов которой подключены к входам и выходам запоминающих устройств соответствующего канала, а вторые выходы и входы процессора подключены к входам и выходам первой группы входов и выходов второй группы коммутаторов, у которой выходы и входы второй группы выходов и входов подключены к входам и выходам устройств обмена своего канала, при этом последовательный и синхронизирующий выходы и последовательные входы устройств обмена подключены к одноименным входам и выходам третьей группы коммутаторов, выходы и входы второй группы выходов и входов которого являются одноименными выходами и входами системы, а дополнительный выход и синхронизирующий вход третьей группы коммутаторов подключены к одноименному входу и выходу формирователя синхроимпульсов, остальные синхронизирующие выходы которого подключены к одноименным входам модулей обмена.

2. Система по п.1, отличающаяся тем, что блок контроля и управления содержит регистр состояния, входы которого являются входами блока, а выходы подключены к группе схем И, ИЛИ, НЕ, выходы которых подключены к входам регистров управления, выходы которых являются выходами блока.

3. Система по п.1, отличающаяся тем, что каждая группа коммутаторов содержит несколько (К) двухвходовых мультиплексоров, первые входы которых являются входами группы, а выходы являются выходами группы, а выходы последующих по номеру мультиплексоров подключены к вторым входам предыдущих, при этом вход первого и выход последнего являются входом и выходом наращивания.

4. Система по п.1, отличающаяся тем, что устройство обмена содержит регистры адреса, данных и адреса абонента, первые входы и выходы которых являются входами устройства, при этом выход регистра адреса подсистемы подключен к входу делителя частоты, выход которого является синхронизирующим выходом устройства и подключен к одноименным входам регистров данных и адреса абонента, соединенных последовательно в сдвиговый регистр, у которого выход регистра адреса абонента является последовательным выходом устройства, а последовательный вход регистра данных является одноименным входом устройства.

5. Система по п.1, отличающаяся тем, что формирователь синхроимпульсов содержит три блока формирования и три задающих генератора, управляющие входы которых являются входом формирователя, а выходы каждого из них подключены к входу своего блока формирования, у каждого из которых фазирующий выход подключен к фазирующим входам двух других блоков, выходы которых являются выходами формирователя.

6. Система по п.5, отличающаяся тем, что блок формирования содержит элемент И, первый вход которого является входом блока, подключенным к задающему генератору, а выход элемента подключен к сдвиговому регистру, выходы которого подключены к входам дешифратора, выход которого подключен к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен к второму входу элемента И и первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова, а синхронизирующий вход триггера пуска объединен с первым входом элемента И и синхронизирующими входами первого и второго триггеров привязки, входы которых являются фазирующими входами блока, а выходы подключены к второму и третьему входам мажоритарного элемента, при этом выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются выходами блока.

7. Система по п.5, отличающаяся тем, что задающий генератор содержит несколько последовательно включенных инверторов, подключенных выходами к мультиплексору, вход которого является управляющим входом генератора, а выход подключен к входу первого инвертора и усилителя, выход которого является выходом генератора.

8. Система по п.4, отличающаяся тем, что делитель частоты содержит счетчик, вход которого объединен с синхронизирующим входом формирователя и является входом делителя, а выход подключен к входу дешифратора, управляющие входы которого являются входами делителя, а выход подключен к входу формирователя, выход которого является выходом делителя.

| Хвощ С.Т | |||

| и др | |||

| Микропроцессоры и микроэвм в системах автоматического управления: Справочник | |||

| - Л.: Машиностроение, 1987, с.610-611, рис.19.5 | |||

| Резервированное вычислительное устройство | 1983 |

|

SU1200292A1 |

| Трехканальная резервированная вычислительная система | 1983 |

|

SU1156273A1 |

| US 20030172248 А1, 11.09.2003. | |||

Авторы

Даты

2013-02-10—Публикация

2011-06-23—Подача