(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1995 |

|

RU2096801C1 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство аналого-цифровогопРЕОбРАзОВАНия | 1979 |

|

SU839044A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Устройство для измерения времени переключения радиостанций | 1982 |

|

SU1029420A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

Л

Изобретение относится к импульсной технике, в частности к устройствам преобразования формы информации, и может использоваться в вычислительной технике и скоростных системах обработки информации.

Известен аналого-цифровой преобразователь (АЦП), содержащий в каждом из трех каналов параллельный АЦП, а также регистр и счетчик 1. Три старших разряда цифрового эквивалента преобразуемого сигнала формируются параллельно с помощью АЦП, а младщие разряды - путем счета импульсов во время линейного разряда конденсатора дополнительных устройств выборки, содержащихся в каждом канале.

Недостатками такого АЦП являются низкая точность и невысокое быстродействие.

Цель изобретения - повыщение точности и быстродействия АЦП.

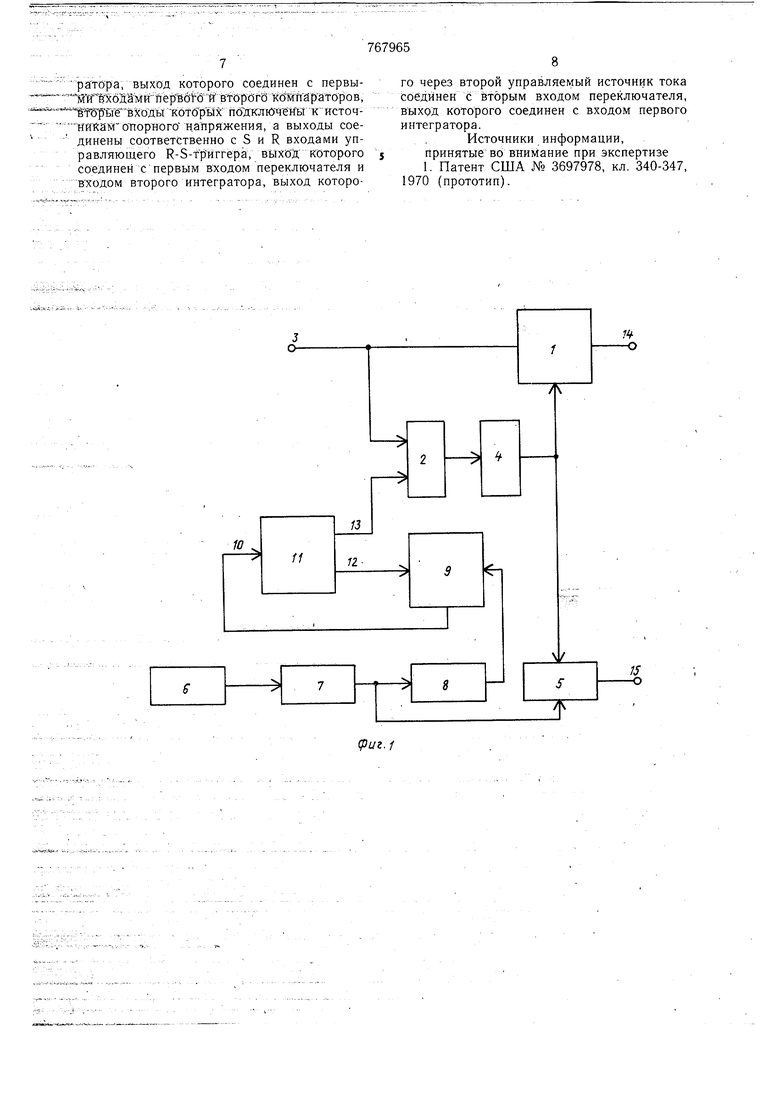

Это достигается тем, что в аналого-цифровой преобразователь, содержащий параллельный, аналого-цифровой преобразователь, регистр и счетчик, дополнительно введены управляемый по частоте генератор сигнала развертки, блок компараторов, делитель частоты, формирователь строб-и.мпульсов, импульсно-фазовый детектор и генератор эталонной частоты, причем первые входы блока компараторов и параллельного аналогоцифрового преобразователя объединены и соединены с входной щи ной, выход блока компараторов через формирователь строб- импульсов подключен соответственно к второму входу параллельного аналого-цифрового преобразователя и первому входу регистра, выход генератора эталонной частоты соединен с входом счетчика, выход которого подключен к второму входу регистра и.

10 через делитель частоты к первому входу импульсно-фазового детектора, второй вход и выход которого соединены соответственно с первым выходом и входом управляемого по частоте генератора сигнала развертки, второй выход которого соединен с вторым входом блока компараторов, выходы параллельного аналого-цифрового преобразователя и регистра соединены с выходной шиной. При этом управляемый по частоте генератор сигнала развертки содержит первый и второй

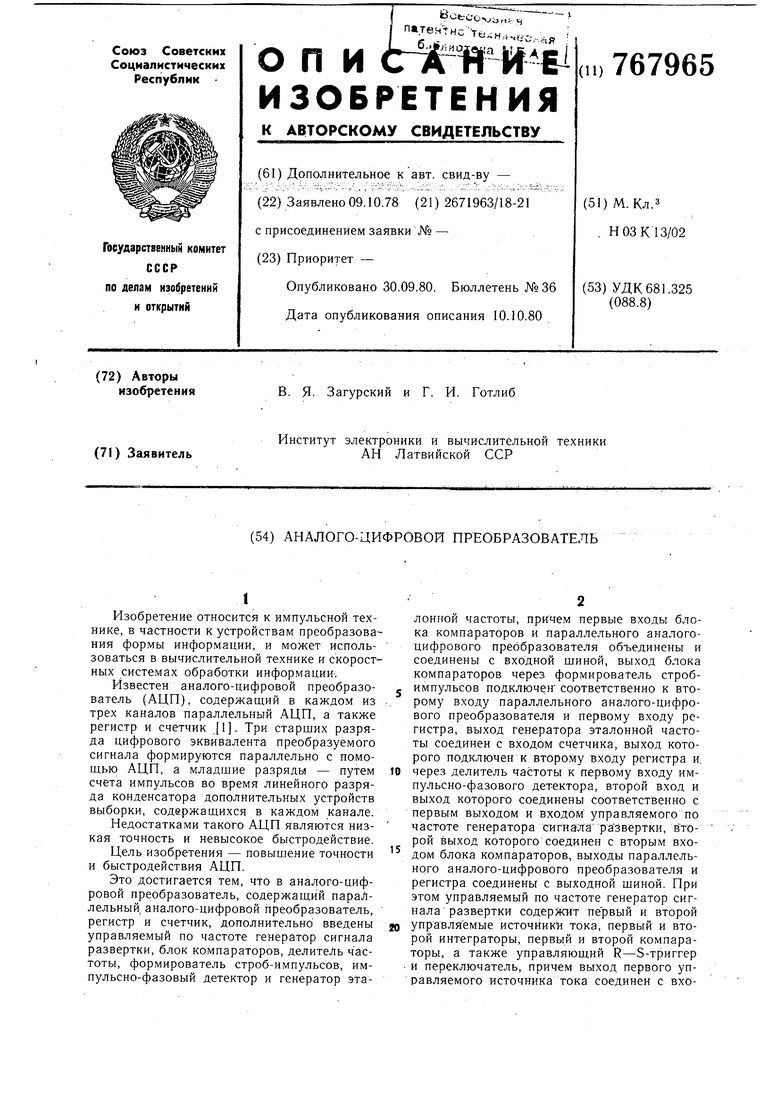

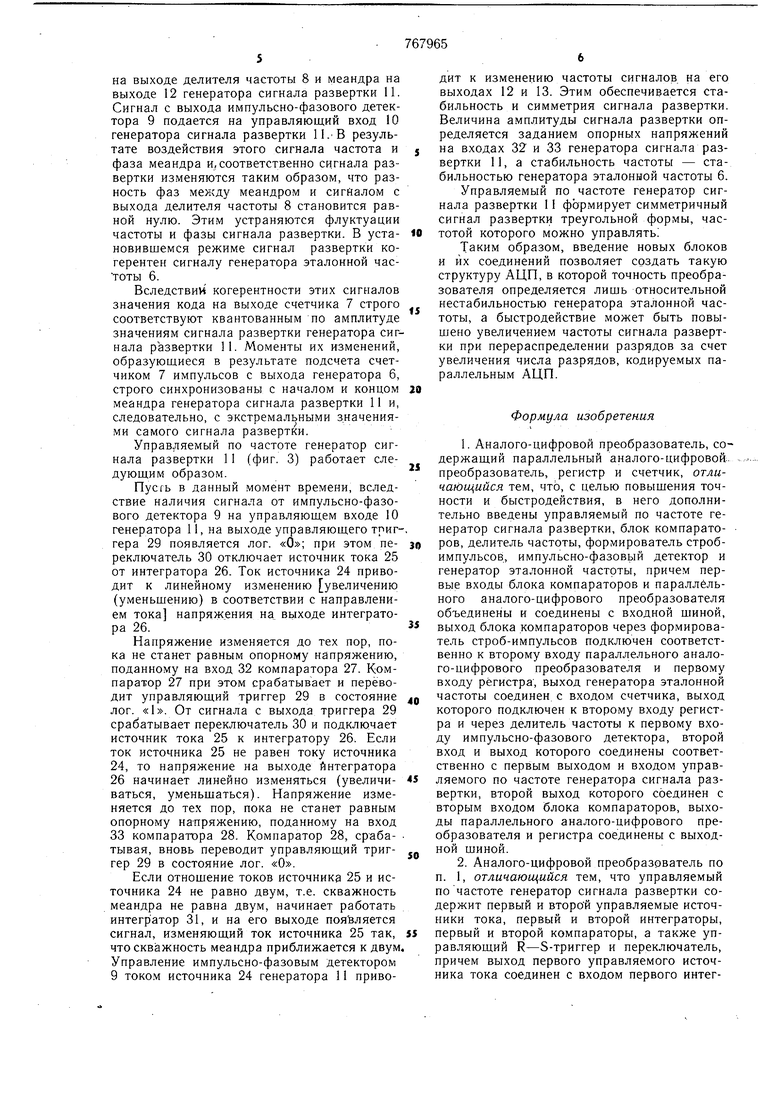

20 управляемые источники тока, первый и второй интеграторы, первый и второй компараторы, а также управляющий R-S-триггер и переключатель, причем выход первого управляемого источника тока соединен с входом первого интегратора, выход которого соединен с первыми входами первого и второ го компараторов, вторые входы которых подключены к источникам опорного напряжения а выходы соединены соответственно с S и R входами управляющего R-S-триггера, выход которого соединен с первым входом переключателя и входом второго интегратора, выход которого через второй управляемый источник тока соединен с вторым входом переключателя, выход которого соединен с входом первого интегратора. На фиг. 1 представлена блок-схема k-pSsрядного (k п + гп, где п 1, 2, 3,..,п, ш 1 2,3,...,т) аналого-цифрового преобразователя; на фиг. 2 изображены временные диаграммы работы преобразователя; на фиг. 3 представлена блок-схема управляемого по частоте генератора сигнала развёртки. Преобразователь (фиг. 1) содержит празрядный (, 2, 3,...,п) параллельный аналого-цифровой преобразователь 1, вход которого соединен с первым входом блока компараторов 2 и входом 3 устройства. Выход блока 2 через формирователь строб-импульсов 4 соединен с вторым входом преобразователя 1 и первым входом ш-разрядного (т 1,2,3,...,т) регистра 5. Выход генератора эталонной частоты 6 соединен с входом т-разрядного (т 1,2,3,...,ш) счетчика 7, выход которого подключен к второму входу регистра 5 и входу делителя час.-тоты 8. Выход делителя частоты 8 соединен с первым входом импульсно-фазового детектора 9, выход которого соединен с управляющим входом 10 управляемого по частоте генератора сигнала развертки 11. Выход 12 генератора сигнала развертки 11 соединен с входом импульсно-фазового детектора 9, а выход 13 - с вторым входом блока 2. ВыХод 14 преобразователя 1 и выход 15 регистра 5 образуют выходы устройства для старших и младщих.разрядов цифрбВбГо эквивалента преобразуемого сигнала соответственВременные диаграммы (фиг. 2) получены при условии, что п m 3, преобразователь 1 и счетчик 7 работают в коде Грея; делитель частоты 8 - двухразрядный, а генератор 11 вырабатывает сигнал развертки треугольной формы. На фиг. 2 приняты еледующие обозначения; 16 - квантующая характеристика преобразователя 1 (заштрихованы состояния лог. «1); 17 - квантующая характеристика блока 2 в момент времени 18 (с учетом работы схемы 4); 19-23 - моменты совпадения сигнала на входе 3 с порогами срабатывания блока 2. Для обеспечения такой,строгой синхронизации управляемый по частоте генератор Сигнала развертки, представленный на фиг. 3, содержит первый 24 и второй 25 управляе мые источники тока, причем выход источника тока 24 соединен с входом первого интегратора 26, выход которого соединен с первыми входами первого 27 и второго 28 компараторов. Выходы компараторов 27 и 28 соединены соответственно с S и R входами управляющего R-S-триггера 29, выход которого соединен с первым входом переключателя 30 и второго интегратора 31. Выход второго интегратора 31 через второй управ- . ляемый источник тока 25 подключен к второму входу переключателя 30, выход которого соединен с входом первого интегратора 26. К вторым входам 32 и 33 соответственно первого 27 и второго 28 компараторов пбдтслючены источники опорного напряжения. Выход первого интегратора 26 является выходом 12 сигнала развертки, выход управляющего R-S-триггера 29 - выходом 13 меандра, а вход первого источника тока 24 - управляющим входом 10 всего управляемого по частоте генератора сигнала развертки 11. Как уже указывалось, генератор 11 вырабатывает сигнал треугольной формы. Преобразователь работает следующим образом. Преобразуемый сигнал с входа 3 поступает на входы блока 2 и преобразователя 1. Поскольку блок 2 сканирует весь диапазон преобразования, то в момент времени 19 23 (фиг. 2) произойдет совпадение преобразуемого сигнала с порогом срабатывания одного из компараторов блОка 2. Моменты совпадения 19-23 определяются как ходом реализации преобразуемого сигнала, так и сигнала развертки. В момент совпадения на выходе формирователя 4 происходит смена логических уровней (лог «О на лог «1. или наоборот). Фронт этого импульса стробирует как преобразователь 1, так и регистр 5, записывая в нем текущее значение кода на выходе счетчика 7. При этом на выходе 14 фиксируется п старших разрядов, а на. выходе 15 - m младших разрядов, составляЮщихk-разрядный (k n + m) кодовый эквивалент преобразуемого сигнала. Фиксация Кодов старших и младших разрядов происходит одновременно по сигналу формирователя строб-импульсов 4. При этом шкала младших разрядов в процессе работы преобразователя реализуется следующим образом. Импульсы эталонной частоты с выхода генератора 6 подсчитываются счетчиком 7. Старший разряд с выхода счетчика 7 подается на вход делителя частоты 8. Импульсы деленной (в рассматриваемом случае - в 4 раза) частоты с выхода делителя 8 при помощи импульсно-фазового детектора 9 сравниваются с сигналом Меандра на выходе 12 генератора сигнала развертки 11. При уходе частоты генератора сигнала развертки 11, что соответствует изменению параметров на его выходах 12 и 13, на выходе импульсно-фазового детектора 9 вырабатывается сигнал, пропорциональный раз ности фаз эталонного сигнала генератора 6

на выходе делителя частоты 8 и меандра на выходе 12 генератора сигнала развертки 11. Сигнал с выхода импульсно-фазового детектора 9 подается на управляющий вход 10 генератора сигнала развертки 11.В результате воздействия этого сигнала частота и фаза меандра несоответственно сигнала развертки изменяются таким образом, что разность фаз между меандром и сигналом с выхода делителя частоты 8 становится равной нулю. Этим устраняются флуктуации частоты и фазы сигнала развертки. В установившемся режиме сигнал развертки когерентен сигналу генератора эталонной частоты 6.

Вследствии когерентности этих сигналов значения кода на выходе счетчика 7 строго соответствуют квантованным по амплитуде значениям сигнала развертки генератора сигнала развертки 11. Моменты их изменений, образующиеся в результате подсчета счетчиком 7 импульсов с выхода генератора 6, строго синхронизованы с началом и концом меандра генератора сигнала развертки И и, следовательно, с экстремальными значениями самого сигнала развертки.

Управляемый по частоте генератор сигнала развертки 11 (фиг. 3) работает следующим образом.

Пусть в данный момент времени, вследствие наличия сигнала от импульсно-фазового детектора 9 на управляющем входе 10 генератора 11, на выходе управляющего триггера 29 появляется лог. при этом переключатель 30 отключает источник тока 25 от интегратора 26. Ток источника 24 приводит к линейному изменению увеличению (уменьшению) в соответствии с направлением тока напряжения на выходе интегратора 26.

Напряжение изменяется до тех пор, пока не станет равным опорному напряжению, поданному на вход 32 компаратора 27. Компаратор 27 при этом срабатывает и переводит управляющий триггер 29 в состояние лог. «1. От сигнала с выхода триггера 29 срабатывает переключатель 30 и подключает источник тока 25 к интегратору 26. Если ток источника 25 не равен току источника 24, то напряжение на выходе интегратора 26 начинает линейно изменяться (увеличиваться, уменьшаться). Напряжение изменяется до тех пор, пока не станет равным опорному напряжению, поданному на вход 33 компаратора 28. Компаратор 28, срабатывая, вновь переводит управляющий триггер 29 в состояние лог. «О.

Если отношение токов источника 25 и источника 24 не равно двум, т.е. скважность меандра не равна двум, начинает работать интегратор 31, и на его выходе появляется сигнал, изменяющий ток источника 25 так, что скважность меандра приближается к двум Управление импульсно-фазовым детектором 9 током источника 24 генератора 11 приводит к изменению частоты сигналов на его выходах 12 и 13. Этим обеспечивается стабильность и симметрия сигнала развертки. Величина амплитуды сигнала развертки определяется заданием опорных напряжений на входах 32 и 33 генератора сигнала развертки 11, а стабильность частоты - стабильностью генератора эталонной частоты 6.

Управляемый по частоте генератор сигнала развертки 11 формирует симметричный сигнал развертки треугольной формы, частотой которого можно управлять

Таким образом, введение новых блоков и их соединений позволяет создать такую структуру АЦП, в которой точность преобразователя определяется лишь относительной нестабильностью генератора эталонной частоты, а быстродействие может быть повышено увеличением частоты сигнала развертки при перераспределении разрядов за счет увеличения числа разрядов, кодируемых параллельным АЦП.

Формула изобретения

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3697978, кл. 340-347, 1970 (прототип).

%

/3 12 8

г

z

13 1

гг Z3 18

20 Z1

сриг.г

Авторы

Даты

1980-09-30—Публикация

1978-10-09—Подача