(54) УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ЦИФРОВЫХ КАНАЛОВ

1

Изобретение относится к области электросвязи, устройствам коммутации и может быть использовано для коммутации цифровых каналов.

Известно устройство для коммутации цифровых каналов, содержащее блок управления, многотактный генератор, адресный распределитель, блок временной коммутации, блок пространственной коммутации, блок входящих запоминающих устройств, блок исходящих запоминающих устройств, при этом выход многотактного генератора соединен с тактирующим входом адресного распределителя, блока временной коммутации, блока пространственной коммутации, блока входящих запоминающих устройств и блока исходящих запоминающих устройств, выходы блока временной коммутации соединены с соответствующими информационными входами блока пространственной коммутации, выход которого соединен с информационными входами блока исходящих запоминающих устройств, а выход блока управления соединен с входом адресного распределителя, первый выход которого подключен к управляющему входу блока пространственНОЙ коммутации, а второй - к управляющему входу блока временной коммутации 1.

Однако пропускная способность такого устройства невелика.

Цель изобретения - повышение пропускной способности устройства.

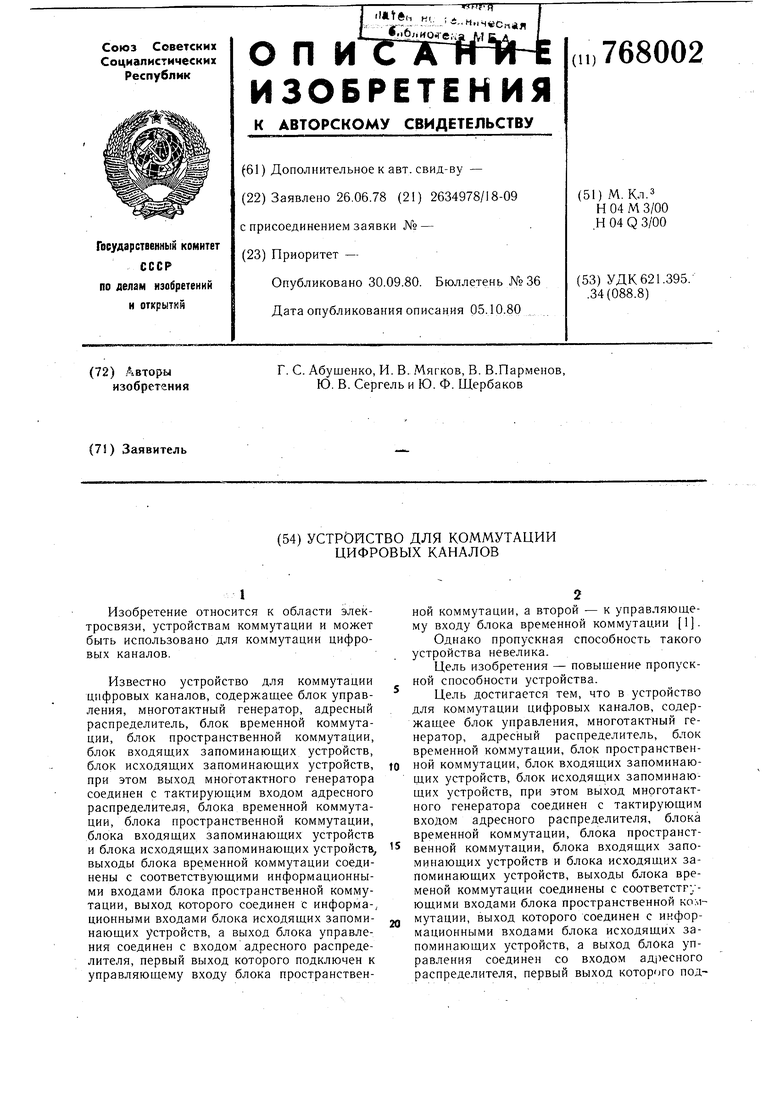

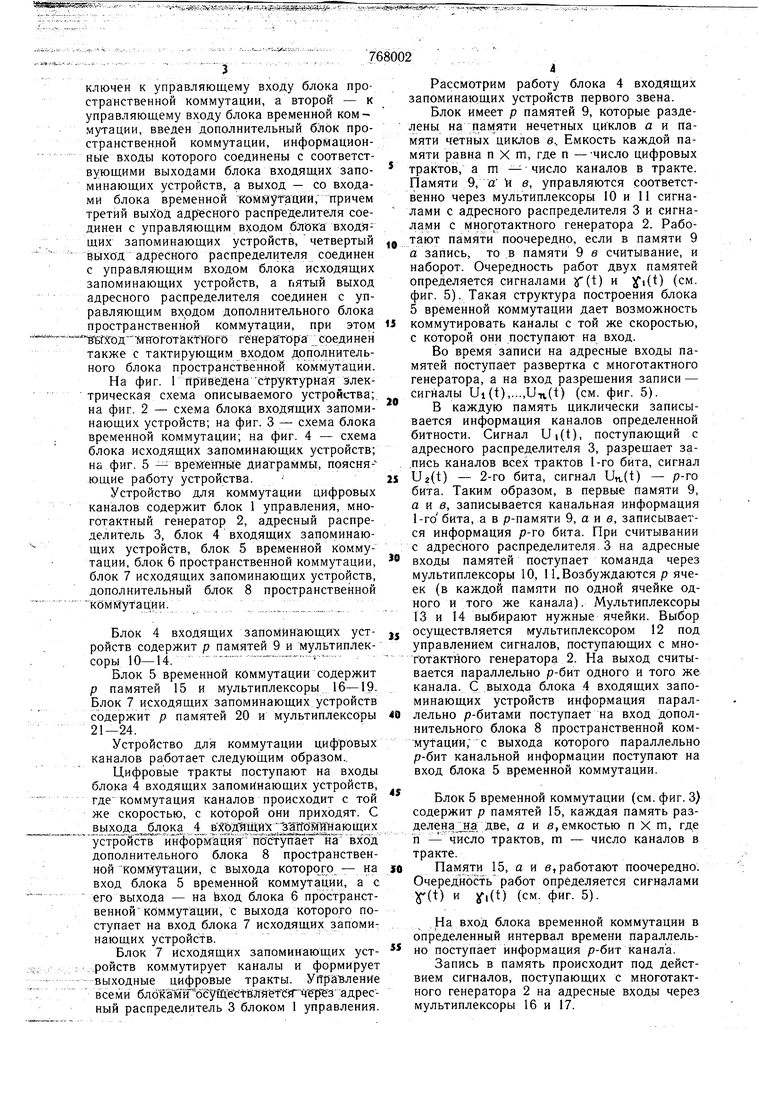

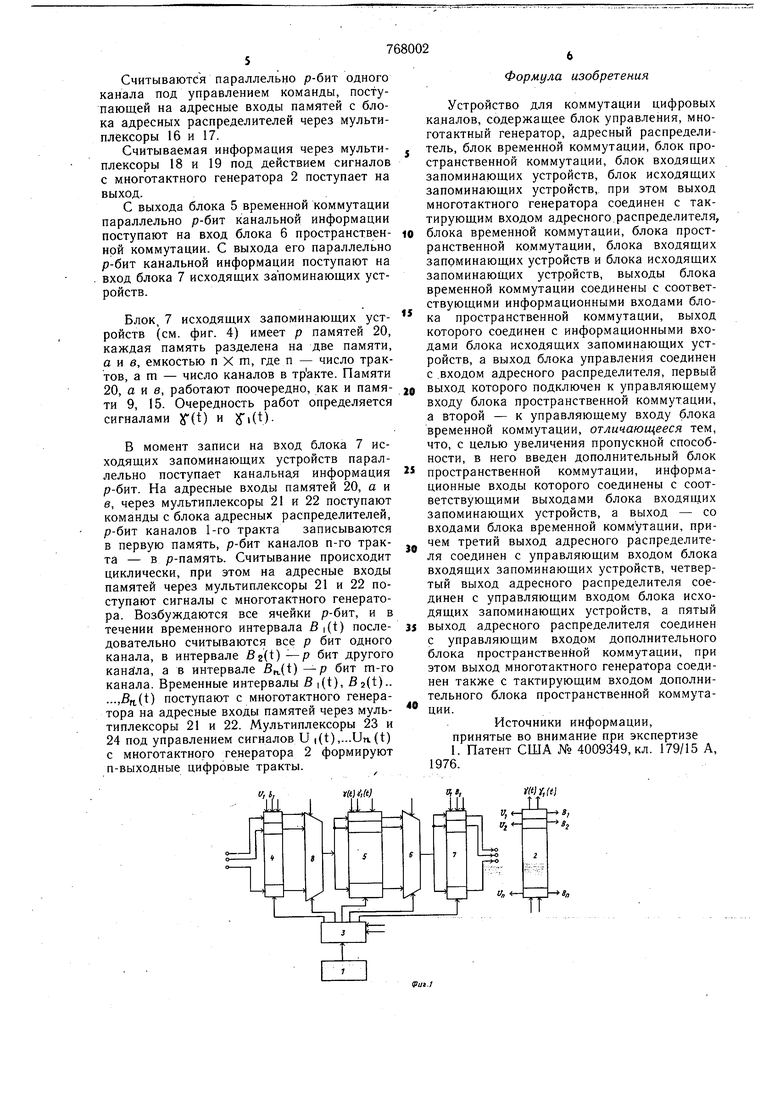

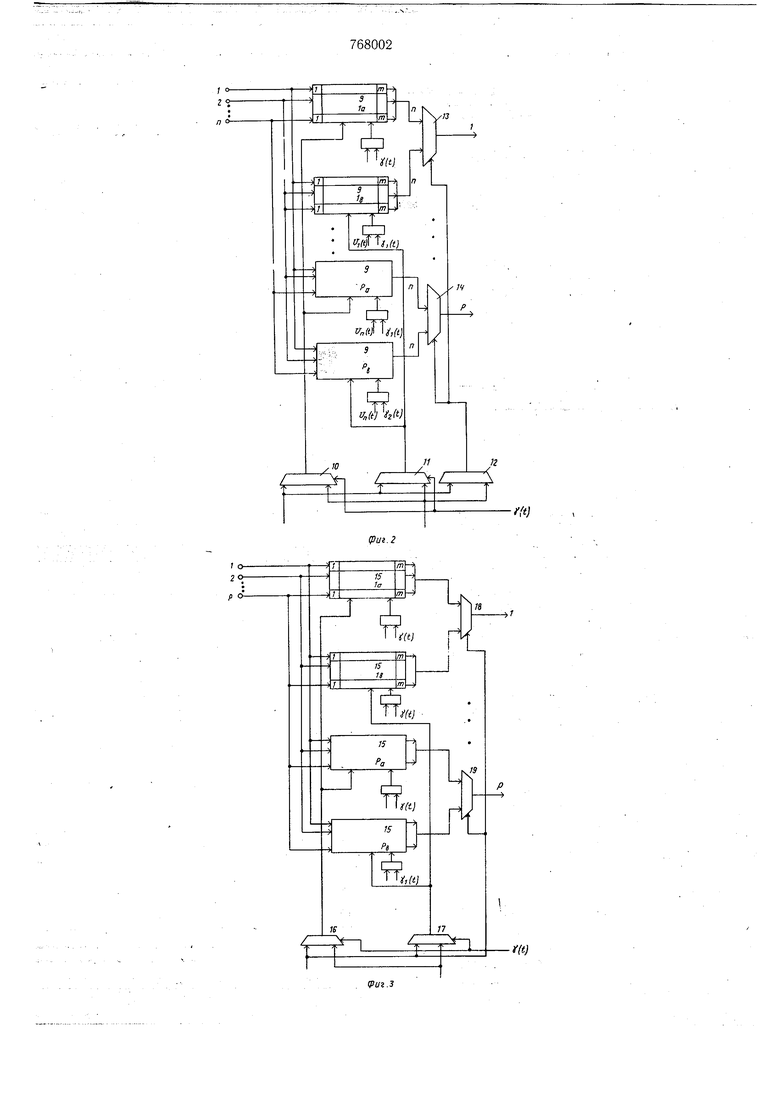

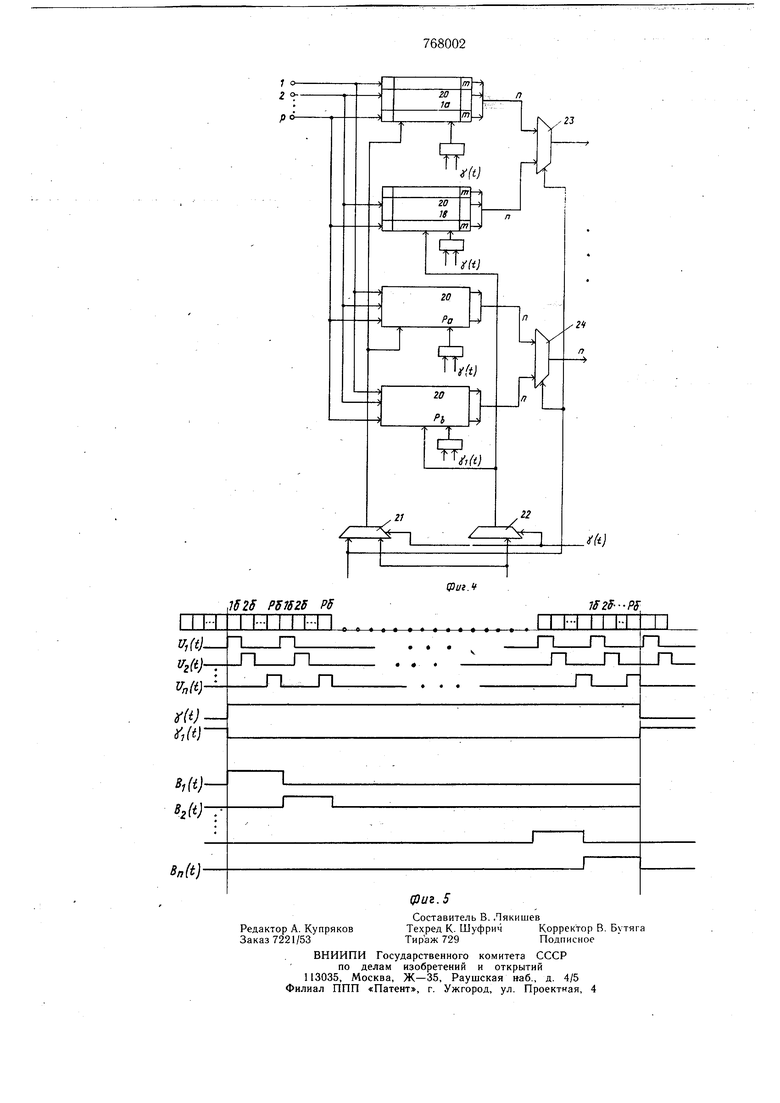

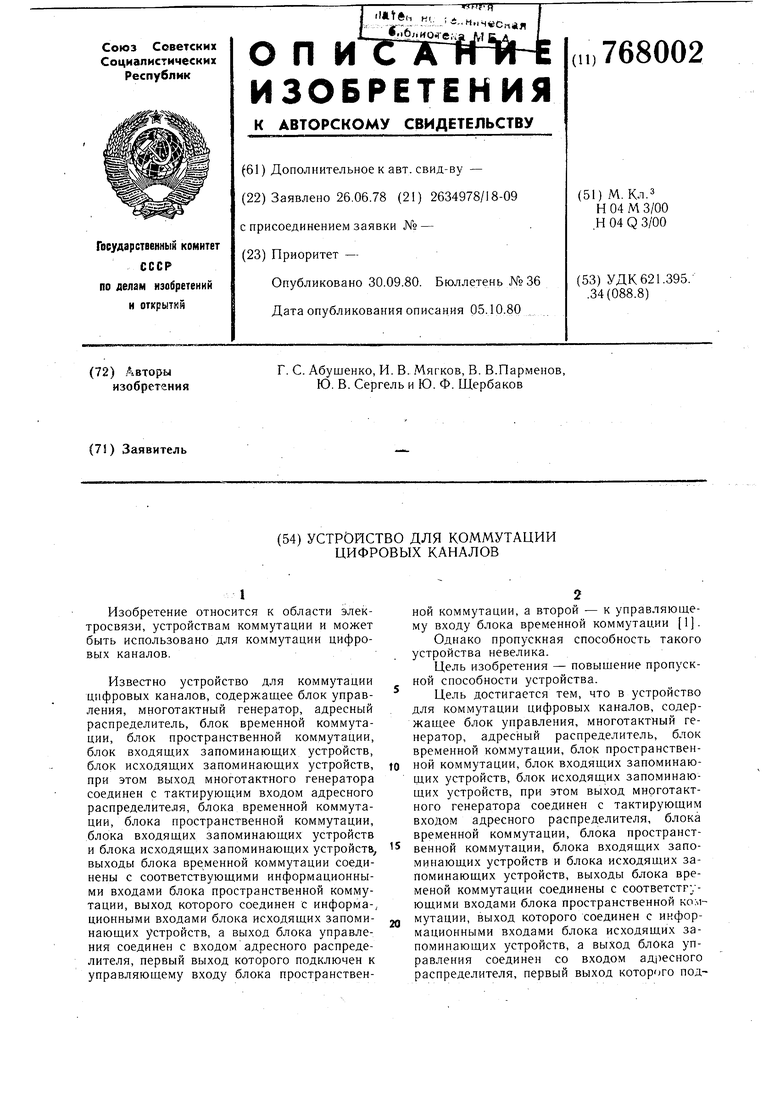

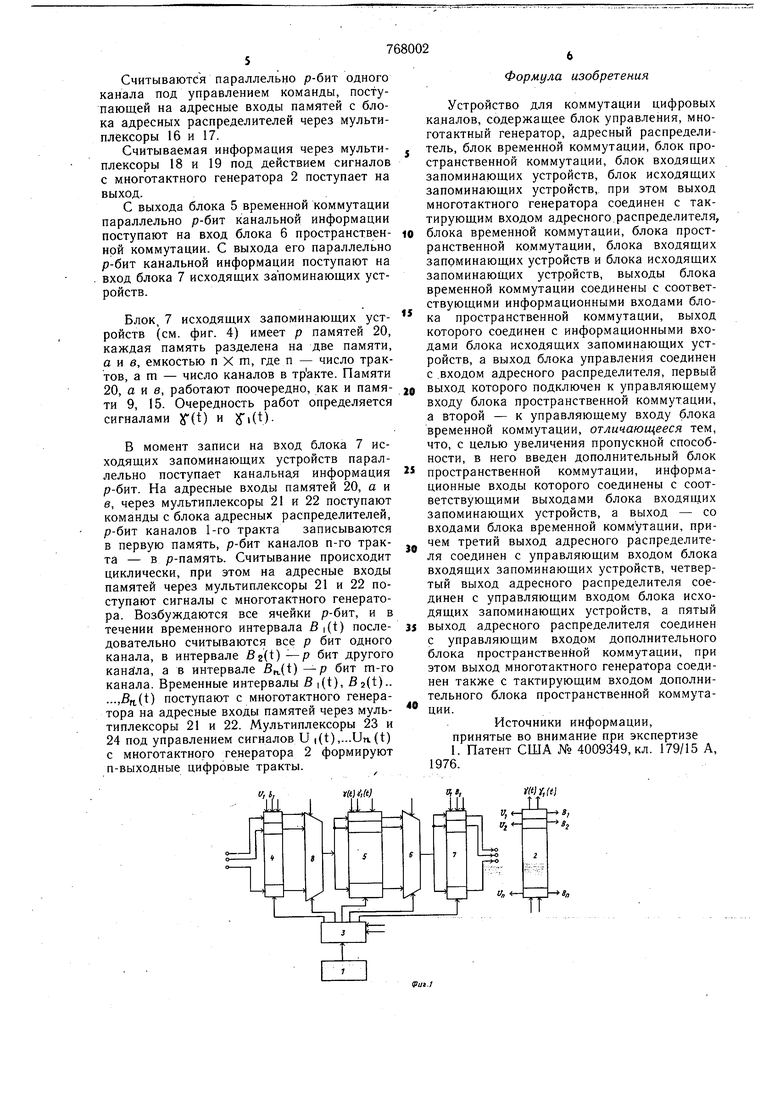

Цель достигается тем, что в устройство для коммутации цифровых каналов, содержащее блок управления, многотактный генератор, адресный распределитель, блок временной коммутации, блок пространственной коммутации, блок входящих запоминающих устройств, блок исходящих запоминающих устройств, при этом выход многотактного генератора соединен с тактирующим входом адресного распределителя, блока временной коммутации, блока пространственной коммутации, блока входящих запоминающих устройств и блока исходящих запоминающих устройств, выходы блока временой коммутации соединены с соответстгующими входами блока пространственной коммутации, выход которого соединен с информационными входами блока исходящих запоминающих устройств, а выход блока управления соединен со входом ад|)есного распределителя, первый выход которого подключей к управляющему входу блока пространственной коммутации, а второй - к управляющему входу блока временной коммутации, введен дополнительный блок пространственной коммутации, информационные входы которого соединены с соответствующими выходами блока входящих запоминающих устройств, а выход - со входами блока временной КОМйугаЦйй; причем третий выход адртесного распределителя соединен с управляющим входом блока входя- щих запоминающих устройств, четвертый выход адресного распределителя соединен с управляющим входом блока исходящих запоминающих устройств, а пятый выход адресного распределителя соединен с управляющим входом дополнительного блока пространственной коммутации, при этом ЖГГод МН15ГотактнОГО генергтора соединен также с тактирующим входом дополнительного блока пространственной коммутации. На фиг. 1 приведенастгруктурная электрическая схема описываемого устройства;, на фиг. 2 - схема блока входящих запоминающих устройств; на фиг. 3 - схема блока временной коммутации; на фиг. 4 - схема блока исходящих запоминающих устройств; на фиг. 5 - Bpeitfemibie Диаграммы, поясняющие работу устройства. Устройство для коммутации цифровых каналов содержит блок 1 управления, многотактный генератор 2, адресный распределитель 3, блок 4 входящих запоминающих устройств, блок 5 временной коммутации, блок 6 пространственной коммутации, блок 7 исходящих запоминающих устройств, дополнительный блок 8 пространственной коммутации. Блок 4 входящих запоминающих устройств содержит р памятей 9 и мультиплексоры 10-14. Блок 5 временной коммутации содержит р памятей 15 и мультиплексоры . Блок 7 исходящих запоминающих устройств содержит р памятей 20 и мультиплексоры 21-24. Устройство для коммутации цифровых каналов работает следующим образом.. Цифровые тракты поступают на входы блока 4 входящих запоминающих устройств, где коммутация каналов происходит с той же скоростью, с которой они приходят. С выхода блока 4 вХодйи1.йх; ;||;ШОТИаЮЦхих устройств инфо)Мацйя дополнительного блока 8 прос1ранственной комйутации, с выхода которого- на вход блока 5 временной коммутации, а с его выхода - на Ьход блока 6 пространственной коммутации, с выхода которого поступает на вход блока 7 исходящих запоминающих устройств. Блок 7 исходящих запоминающих устройств коммутирует каналы и формирует выходные цифровые тракты. Управление всеми блокаЖ бс7Ще(;тВЛйёТс:Гч рНЗ-адресный распределитель 3 блоком 1 управления. Рассмотрим работу блока 4 входящих запоминающих устройств первого звена. Блок имеет р памятей 9, которые разделены на памяти нечетных циклов а и памяти четных циклов в.. Емкость каждой памяти равна п X гп, где п --число цифровых трактов, а гп - число каналов в тракте. Памяти 9, а и в, управляются соответственно через мультиплексоры 10 и И сигналами с адресного распределителя 3 и сигналами с многртактного генератора 2. Работают памяти поочередно, если в памяти 9 а запись, то в памяти 9 в считывание, и наборот. Очередность работ двух памятей определяется сигналами f(i) и (i) (см. фиг. 5). Такая структура построения блока 5 временной коммутации дает возможность коммутировать каналы с той же скоростью, с которой они поступают на вход. Во время записи на адресные входы памятей поступает развертка с многотактного генератора, а на вход разрещения записи - сигналы Ui(t),...,Uu(t) (см. фиг. 5). В каждую память циклически записывается информация каналов определенной битности. Сигнал U|(t), поступающий с адресного распределителя 3, разрещает за.пись каналов всех трактов 1-го бита, сигнал U2(t) - 2-го бита, сигнал Utt(t) - р-го бита. Таким образом, в первые памяти 9, айв, записывается канальная информация 1-го бита, а в р-памяти 9, а и в, записывается информация р-го бита. При считывании с адресного распределителя.3 на адресные входы памятей поступает команда через мультиплексоры 10, 11. Возбуждаются р ячеек (в каждой памяти по одной ячейке одного и того же канала). Мультиплексоры 13 и 14 выбирают нужные ячейки. Выбор осуществляется мультиплексором 12 под управлением сигналов, поступающих с многотактного генератора 2. На выход считывается параллельно р-бит одного и того же канала. С выхода блока 4 входящих запоминающих устройств информация параллельно р-битами поступает на вход дополнительного блока 8 пространственной коммутаций;с выхода которого параллельно р-бит канальной информации поступают на вход блока 5 временной коммутации. Блок 5 временной коммутации (см. фиг. 3) содержит р памятей 15, каждая память разделена на, две, а и в, емкостью п X гп, где h - число трактов, m - число каналов в тракте. Памяти 15, а и в, работают поочередно. Очередность работ определяется сигналами (t) и j,(t) (см. фиг. 5). , На вход блока временной коммутации в определенный интервал времени параллельно поступает информация р-бит канала. Запись в память происходит под действием сигналов, поступающих с многотактного генератора 2 на адресные входы через мультиплексоры 16 и 17.

Считываются параллельно р-бит одного канала под управлением команды, поступающей на адресные входы памятей с блока адресных распределителей через мультиплексоры 16 и 17.

Считываемая информация через мультиплексоры 18 и 19 под действием сигналов с многотактного генератора 2 поступает на выход.

С выхода блока 5 временной коммутации параллельно р-бит канальной информации поступают на вход блока 6 пространственной коммутации. С выхода его параллельно р-бит канальной информации поступают на вход блока 7 исходящих запоминающих устройств.

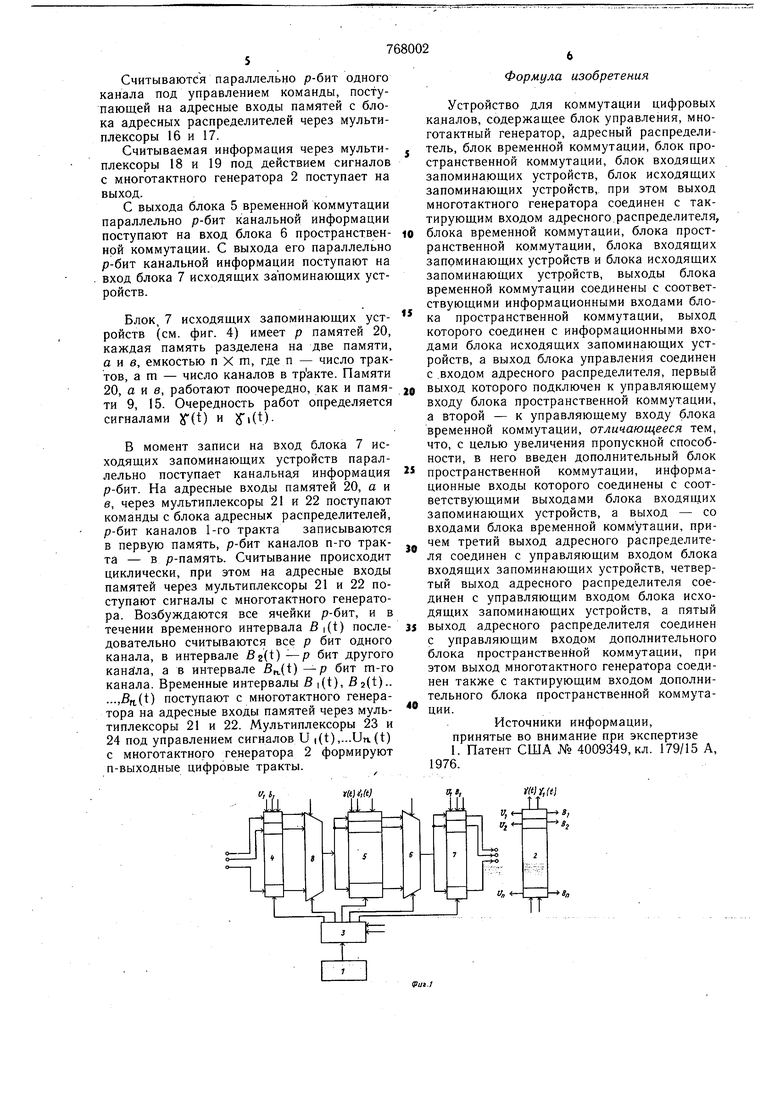

Блок 7 исходящих запоминающих устройств (см. фиг. 4) имеет р памятей 20, каждая память разделена на две памяти, айв, емкостью п X т, где п - число трактов, am - число каналов в тракте. Памяти 20, а и 8, работают поочередно, как и памяти 9, 15. Очередность работ определяется сигналами Jf(t) и yi(t).

В момент записи на вход блока 7 исходящих запоминающих устройств параллельно поступает канальная информация р-бит. На адресные входы памятей 20, а и S, через мультиплексоры 21 к 22 поступают команды с блока адресных распределителей, р-бит каналов 1-го тракта записываются в первую память, р-бит каналов п-го тракта - в р-память. Считывание происходит циклически, при этом на адресные входы памятей через мультиплексоры 21 и 22 поступают сигналы с многотактного генератора. Возбуждаются все ячейки р-бит, и в течении временного интервала S i(t) последовательно считываются все р бит одного канала, в интервале Bz(i) -р бит другого канала, а в интервале B,{t)-р бит т-го канала. Временные интервалы B(i), By{i).. ...,Bfi(i) поступают с многотактного генератора на адресные входы памятей через мультиплексоры 21 и 22. Мультиплексоры 23 и 24 под управлением сигналов U ((t),...Un.(t) с многотактного генератора 2 формируют п-выходные цифровые тракты.

Формула изобретения

Устройство для коммутации цифровых каналов, содержащее блок управления, многотактный генератор, адресный распределитель, блок временной коммутации, блок пространственной коммутации, блок входящих запоминающих устройств, блок исходящих запоминающих устройств, при этом выход многотактного генератора соединен с тактирующим входом адресного.распределителя, блока временной коммутации, блока прост0ранственной коммутации, блока входящих запоминающих устройств и блока исходящих запоминающих устройств, выходы блока временной коммутации соединены с соответствующими информационными входами блока пространственной коммутации, выход которого соединен с информационными входами блока исходящих запоминающих устройств, а выход блока управления соединен с .входом адресного распределителя, первый выход которого подключен к управляющему

0 входу блока пространственной коммутации, а второй - к управляющему входу блока временной коммутации, отличающееся тем, что, с целью увеличения пропускной способности, в него введен дополнительный блок

S пространственной коммутации, информационные входы которого соединены с соответствующими выходами блока входящих запоминающих устройств, а выход - со входами блока временной коммутации, причем третий выход адресного распределите0ля соединен с управляющим входом блока входящих запоминающих устройств, четвертый выход адресного распределителя соединен с управляющим входом блока исходящих запоминающих устройств, а пятый выход адресного распределителя соединен

5 с управляющим входом дополнительного блока пространственной коммутации, при этом выход многотактного генератора соединен также с тактирующим входом дополнительного блока пространственной коммута0ции.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 4009349, кл. 179/15 А, 1976.

тт

/ °

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коммутации цифровых сигналов | 1975 |

|

SU658789A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство временной коммутации асинхронных импульсных каналов | 1975 |

|

SU568194A2 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для коммутации телеграфных каналов | 1979 |

|

SU866774A1 |

| Пространственно-временное поле для коммутации цифровых сигналов с временным уплотнением | 1974 |

|

SU511738A1 |

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

t о

ро

2J

1S2S PS75ZS PS

15ZS---P5

IfdJ -

Si(t)-

Bzi)

Авторы

Даты

1980-09-30—Публикация

1978-06-26—Подача