Г

rCl.TN

-

Jr

rrrvj

.ц±1

г J

Л

,С.

iU

.TN

j

- м- : - t--

Jr-Jab

п

04 0

X Ю О

о

Изобретение относится к электросвязи и может использоваться в устройствах коммутации цифровых сигналов.

Цель изобретения - расширение диапазона скоростей цифровых сигналов.

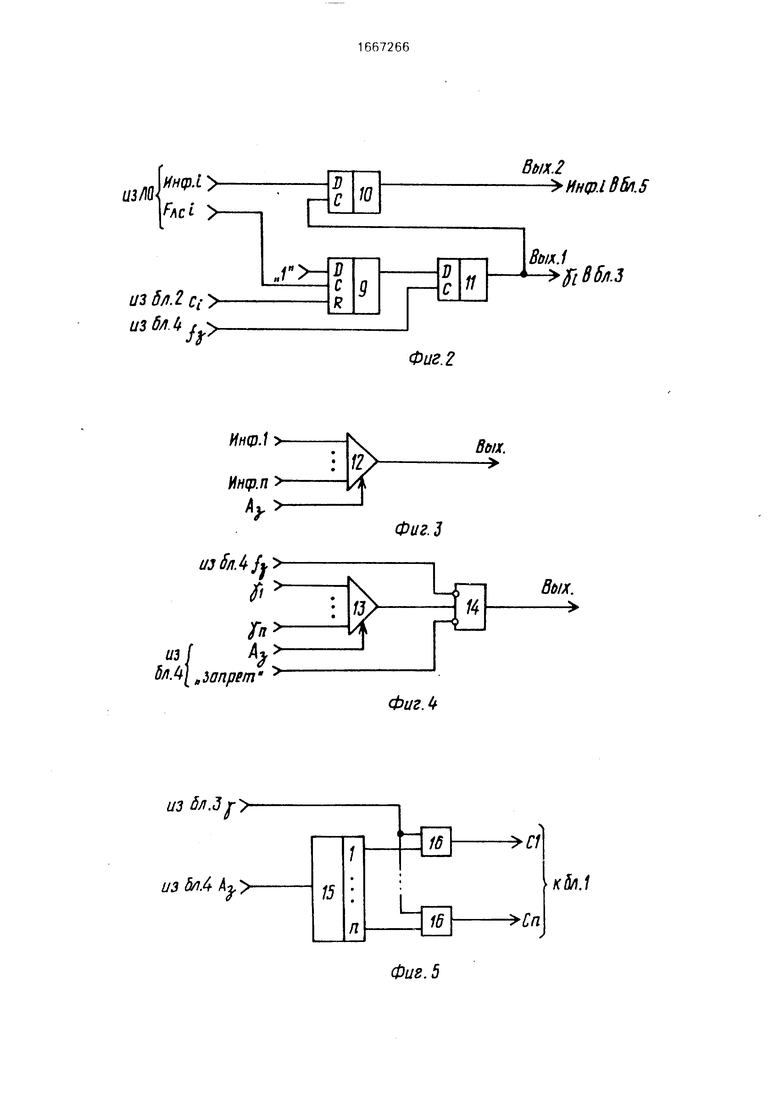

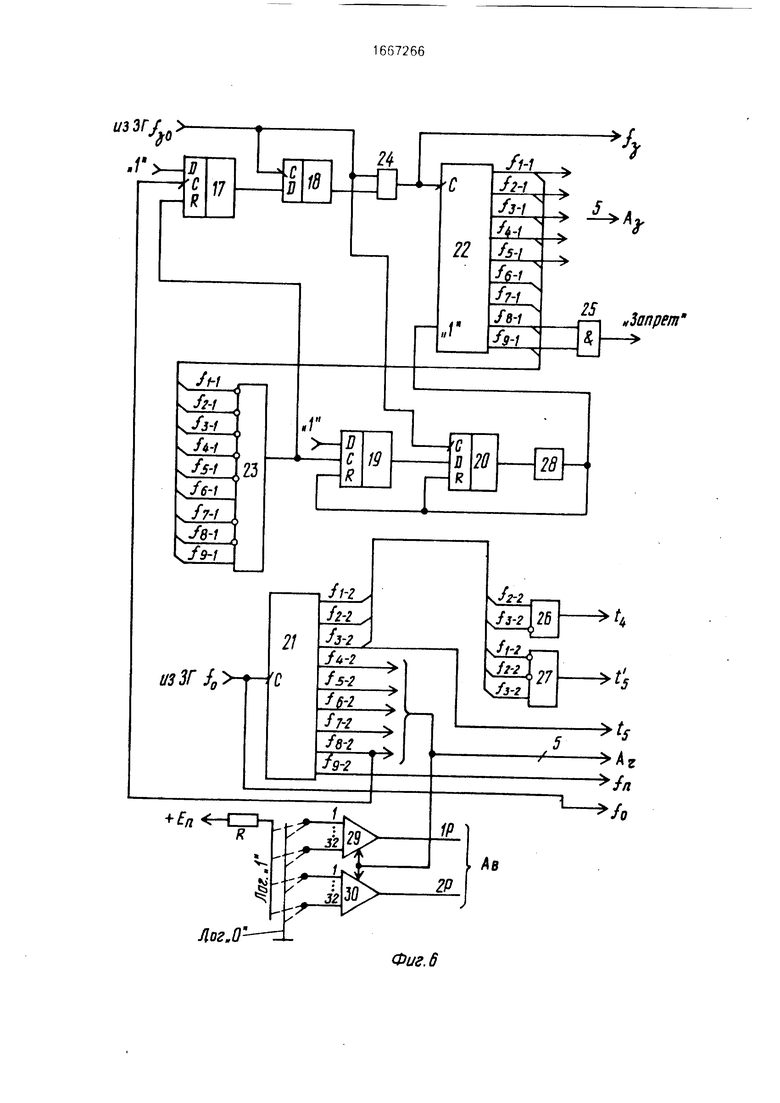

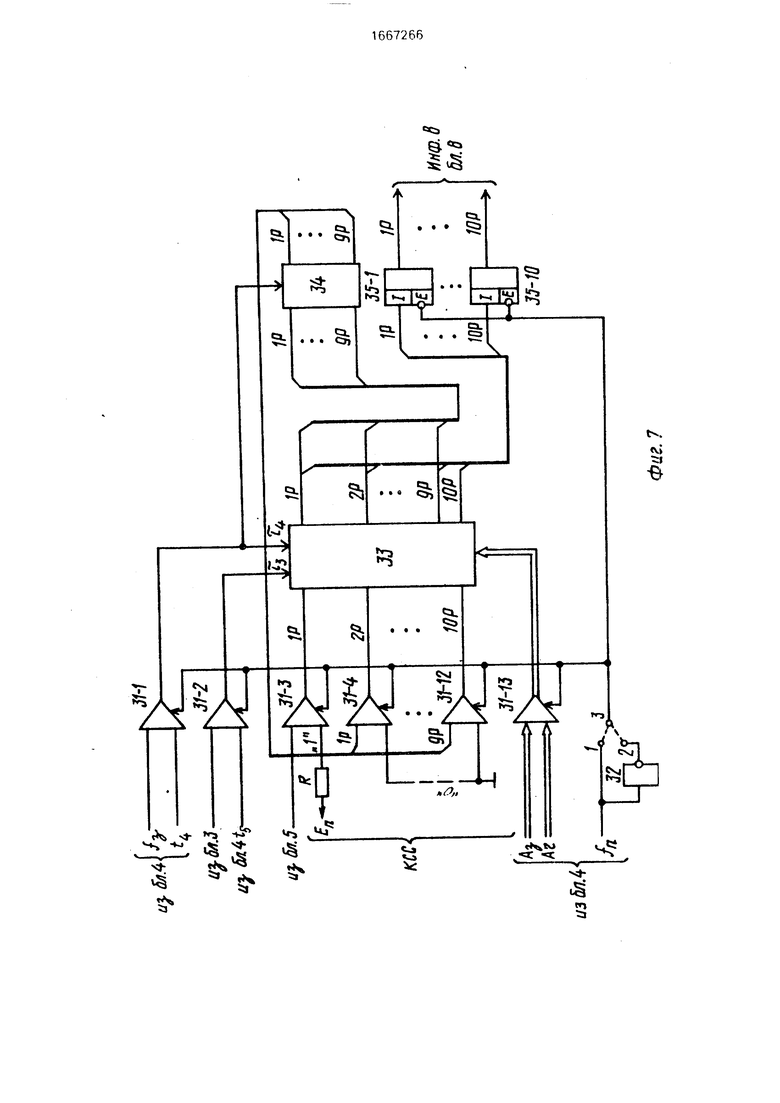

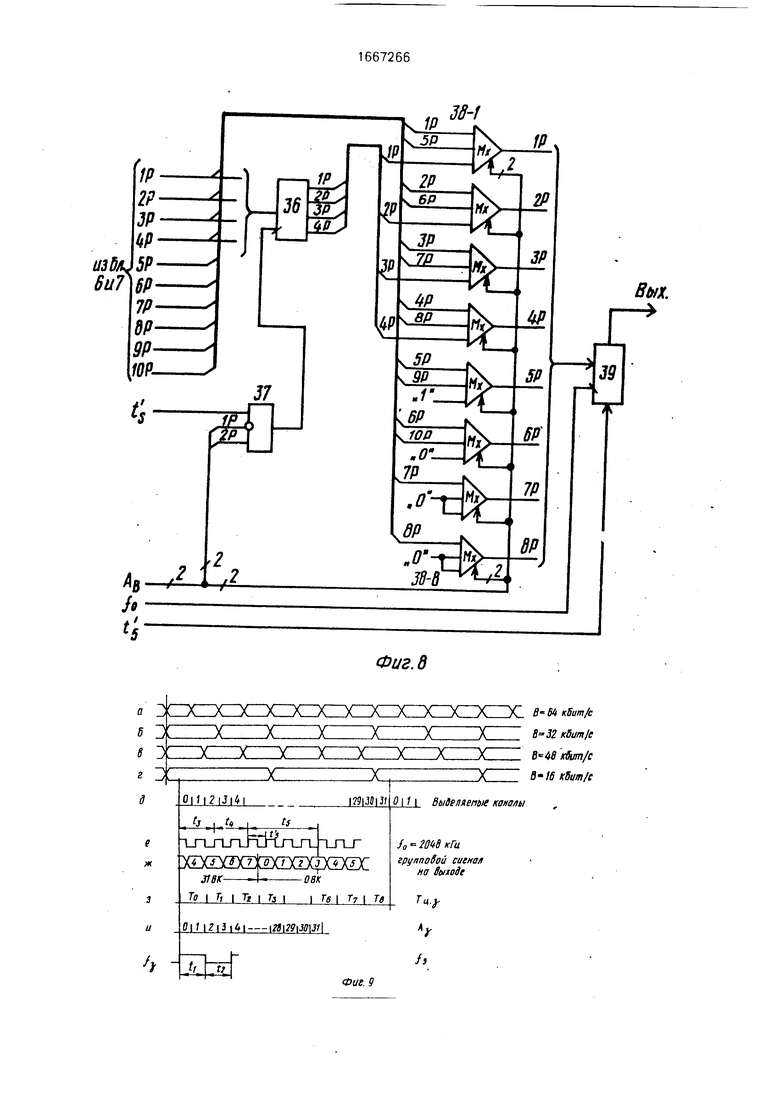

На фиг. 1 приведена структурная электрическая схема устройства сопряжения раз- носкоростных асинхронных цифровых сигналов; на фиг. 2-8 - примеры выполнения соответственно блока привязки, второго и первого мультиплексоров, дешифратора, блока синхронизации, преобразователя сигналов и преобразователя кода; на фиг. 9-10 - временные диаграммы, поясняющие принцип функционирования устройства.

Устройство сопряжения разноскорост- ных асинхронных цифровых сигналов содержит блоки 1 привязки, дешифратор 2, первый мультиплексор 3 и блок 4 синхронизации, а также второй мультиплексор 5. первый и второй преобразователи 6 и 7 сигналов и преобразователь 8 кода.

Блок привязки (фиг. 2) включает три D- триггера 9-11. Второй и первый мультиплексоры (фиг. 3 и 4) включают мультиплексоры 12 и 13 и элемент И 14, Дешифратор (фиг. 5) включает дешифратор 15 и элементы И 16.

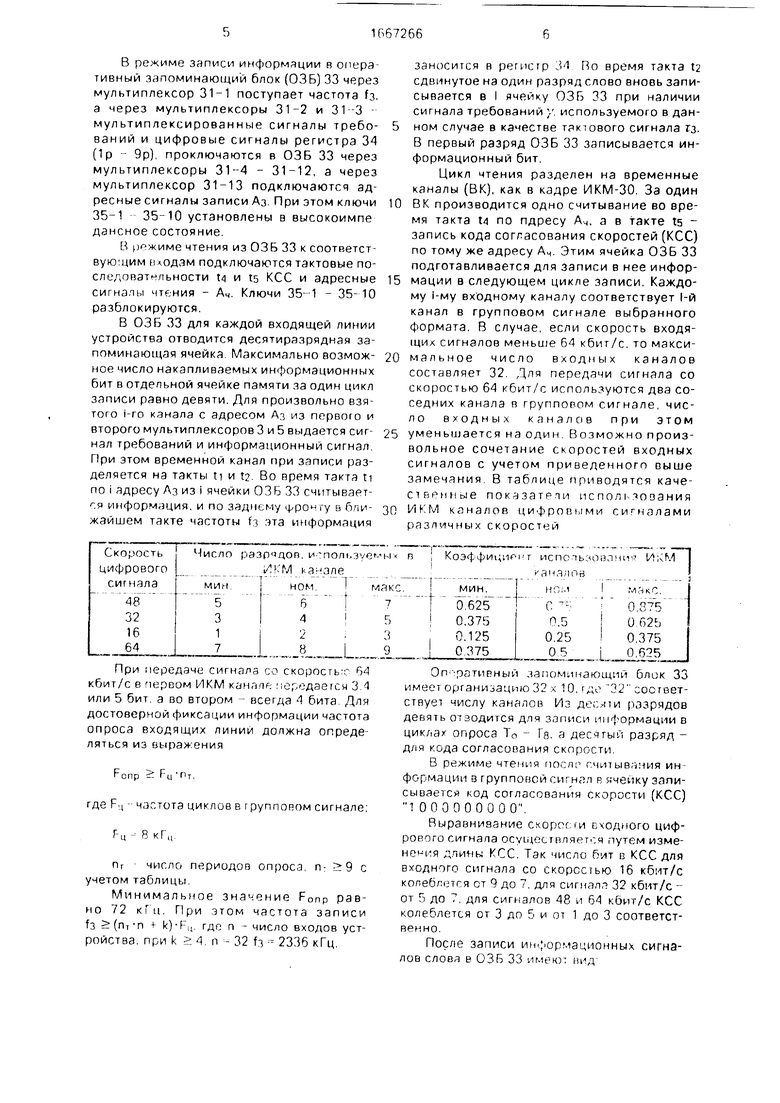

Блок синхронизации (фиг. 6) включает четыре D-триггера 17-20, два счетчика 21 и 22, пять элементов И 23-27, дифференцирующую цепь 28 и мультиплексоры 29 и 30.

Преобразователь сигналов (фиг. 7) включает мультиплексоры 31, элемент ИЛИ 32, оперативный запоминающий блок 33, регистр 34 и ключи 35.

Преобразователь кода (фиг. 8) включает первый регистр 36, элемент И 37, мультиплексоры 38 и второй регистр 39.

Устройство сопряжения разноскорост- ных цифровых сигналов работает следующим образом.

Цифровые сигналы по линиям связи по ступают из линейного оборудования (ЛО) на блоки 1 привязки. Каждой входящей линии соответствует свой блок 1 привязки. Между ЛО и блоком привязки осуществляется со- направленный стык. Фиксация информации в блоке 1 привязки (фиг. 2) производится на частоте передаваемого цифрового сигнала, привязанного к частоте f3 в центре принимаемых посылок с помощью D-триггера 10. Привязка тактового сигнала Fnci к частоте Тз - осуществляется с помощью D-триггеров 9 и 10. Выходной сигнал D-триггерэ 11 является сигналом требований yi - 1.

Информационные сигналы из блоков 1 привязки поступают на второй мультиплексор 5, а сигнал1 требований у - на первый мультиплексор 3. Второй мультиплексор 12 (фиг. 3) управляется адресными сигналами Аз, формируемыми в блоке 4 синхронизации. и осуществляет побитое временное уплотнение поступающих цифровых сигналов.

Сигналы требований объединяются (фиг. 4) мультиплексором 13. Объединенные

0 сигналы стробируются частотой fa в элементе И 14. Сигнал Запрет, вырабатываемый блоком 4 синхронизации, блокирует сигналы требований у на время согласования цикла записи с циклом чтения, и его дли5 тельность может достигать нескольких периодов частоты fa.

Для обеспечения однократного приема информационных сигналов из входных линий дешифратор 2 по сигналам Аз выраба0 тывает сигналы Ci . Сп, подаваемые в соответствующие блоки 1 привязки для их обнуления. Дешифратор 2 (фиг. 5) включает дешифратор 15, к выходам которого подключены элементы И 16. На другие входы

5 элементов И 16 поступает мультиплексированный сигнал требований. В первом и втором преобразователях 6 и 7 сигналов осуществляется преобразование мультиплексированных информационных сигна0 лов и сигналов требований в параллельную форму. Эти сигналы в преобразователе 8 кода преобразуются далее в принятый для данной системы формит (кадр).

5В случае сопряжения низкоскоростных

сигналов со скоростью до 64 кбит/с включительно в формит, соответствующий формигу серийно выпускаемой аппаратуры ИКМ-30, схема преобразователя (6 или 7) сигналов

0 может быть выполнена в соответствии с фиг. 7. На мультиплексор 31-1 поступают часто- та тз и тактовая последовательность t4 из блока А синхронизации а на мультиплексоры 31-3 и 31-2 - мультиплексированные

5 информационный сигнал и сигнал требований. На мультиплексор 31-13 поступают адресные сигналы записи и чтения Аз и Ач также из блока 4 синхронизации. На управляющие входы всех мультиплексоров

0 31 и вход элемента НЕ 32 поступает тактовая последовательность переключений fn. Код согласования скоростей (КСС) вырабатывается непосредственно в преобразователях сигналов Преобразователи 6 и 7

5 сигналов работают в противофазе, для чего в одном блоке устанавливается перемычка 1-3. а во втором - 2-3. Частота переключений fn для упомянутого выше случая составляет 4 кГц, скважность импульсов - 2.

В режиме записи информации в оперативный запоминающий блок (ОЗБ) 33 через мультиплексор 31-1 поступает частота Ь, а через мультиплексоры 31-2 и 31--3 - мультиплексированные сигналы требо- ваний и цифровые сигналы регистра 34 (1р - 9р), проключаются в ОЗБ 33 через мультиплексоры 31-4 - 31-12, а через мультиплексор 31-13 подключаются ад- ресные сигналы записи Аз При этом ключи 35-1 35-10 установлены в высокоимпе дансное состояние.

В режиме чтения из ОЗБ 33 к соответствующим (йодам подключаются тактовые последовательности t4 и is KCC и адресные сигналы чтения - Ач. Ключи 35-1 - 35-10 разблокируются.

В ОЗБ 33 для каждой входящей линии устройства отводится десятиразрядная запоминающая ячейка Максимальновозмож- мое число накапливаемых информационных бит в отдельной ячейке памяти за один цикл записи равно девяти. Для произвольно взятого 1-го канала с адресом АЗ из первого и второго мультиплексоров 3 и 5 выдается сиг- нал требований и информационный сигнал При этом временной канал при записи разделяется на такты ti и t2 Во время такга ti по i адресу АЗ из I ячейки ОЗБ 33 считывается информация, и по заднему фронту в бпи- жайшем такте частоты f3 эта информация

заносится в регистр J4 По время такта t2 сдвинутое на один разряд слово вновь записывается в I ячейку ОЗБ 33 при наличии сигнала требований у используемого в данном случае в качестве тактового сигнала гз. В первый разряд ОЗБ 33 записывается информационный бит.

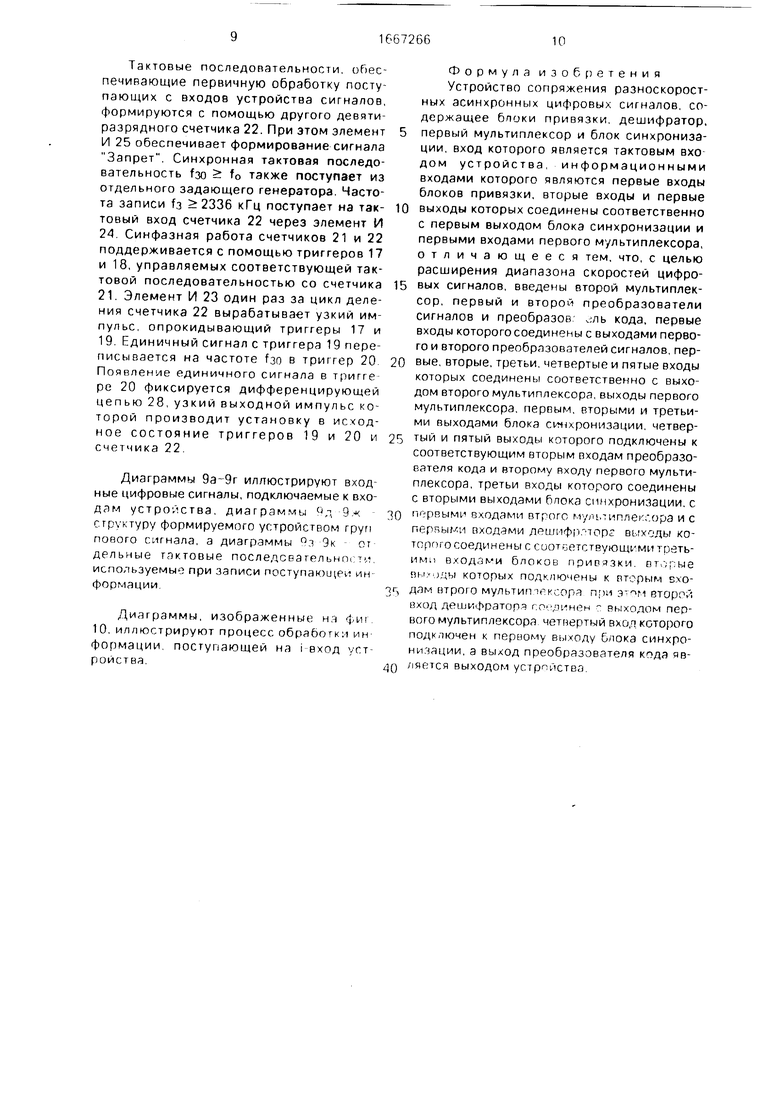

Цикл чтения разделен на временные каналы (ВК), как в кадре ИКМ-30. За один ВК производится одно считывание во время такта 14 по пдресу Ач. а в такте ts - запись кода согласования скоростей(КСС) по тому же адресу Ач Этим ячейка ОЗБ 33 подготавливается для записи в нее информации в следующем цикле записи. Каждому i-му входному каналу соответствует 1-й канал в групповом сигнале выбранного формата. В случае, если скорость входящих сигналов меньше 64 кбит/с, то максимальное число входных каналов составляет 32 Для передачи сигнала со скоростью 64 кбит/с используются два соседних канала в групповом сигнале, число входных каналов при этом уменьшается на один Возможно произвольное сочетание скоростей входных сигналов с учетом приведенного выше замечания В таблице приводятся качественные покззатрти истолкования И КМ кдналов цифровыми сигналами различных скоростей

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Устройство для передачи и приема цифровой информации | 1986 |

|

SU1322344A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для передачи и приема цифровой информации | 1987 |

|

SU1481832A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

Изобретение относится к электросвязи и может использоваться в устройствах коммутации цифровых сигналов. Цель изобретения - расширение диапазона скоростей цифровых сигналов. Для достижения указанной цели в устройство введены второй мультиплексор 5, первый и второй преобразователи 6 и 7 сигналов и преобразователь 8 кода. Приводятся примеры выполнения всех узлов устройства для случая сопряжения цифровых сигналов со скоростями до 64 кбит/с включительно в групповой сигнал, соответствующий сигналу серийно выпускаемой аппаратуры. 10 ил.

При передаче сигнала со скоросты 64 кбит/с в первом ИКМ канапе черздаегся 3 4 или 5 бит а во втором - всегда 4 бита Для достоверной фиксации информации частота опроса входящих линии должна опреде ляться из выражения

опр

Fu -пт,

где F.t частота циклов в групповом сигнале; Рц- В кГц

пг число периодов опроса п- 9 с учетом таблицы

Минимальное значение F0np равно 72 кГц. При этом частота записи f3 (пт П + k)-Fu где п - число входов устройства, при к 4 п - 32 fi - 2336 кГц.

Коэффицир 1 г испс ть.-юол LHV чналов

ИхМ

п

Оп рзтивный запоминающий блок 33 имееторгануьацию 32 10, г до 32 соответствует числу каналов Из десяти разрядов девять отводится для записи информации в циклах опроса Т0 - Га. а десятый разряд - для кода согласования скорости

В режиме чтения поел.1 считывания информации в групповой сигнал в ячеику записывается код согласования скорости (КСС) 1000000000

Выравнивание скорое ги входного цифрового сигнала осуществляется путем изме- дпи«ы КСС. Так число бит в КСС для входного сигнала со скоростью 16 кбит/с колеблется от 9 до 7, для сигнала 32 кбит/с - от 5 до 7, для сигналов 48 и 64 кбит/с КСС колеблется от 3 до 5 и от 1 до 3 соответственно.

После записи информационных сигналов слова в ОЗБ 33 имеют вид

Значение кодов скорости Ав записывается в блок 4 синхронизации по месту установки устройства на станции с помощью мультиплексоров 29 иЗО(фиг. 6). К примеру, если к 1-му входу подключается сигнал со скоростью 48 кбит/с, то это соответствует коду 00, если же на 1-м входе действует сигнал со скоростью 64 кбит/с, то это соответствует коду 01 в 1-м канале и 10 в (I + 1)-м канале.

Согласование форматов сигналов при считывании производится путем исключения 9 и 10-го разрядов, так как максимальное число бит информации для сигналов со скоростью до 48 кбит/с равно 7 и они занимают положение с 2 по 7-й разряд, а 8-й разряд может быть занят Ч КСС.

Считывание слов из преобразователей 6 и 7 сигналов по l-му адресу Ач происходит во время такта /. а во время такта ts в 1-ю ячейку записывается КСС

В преобразователе 8 кода слово в регистр 39 записывается по переднему фронту такта ts1, совпадающему с задним фронтом такта ts и с передним фронтом частоты f0. Запись в регистр 36 происходит по переднему фронту последовательности ts, проходящей через элемент И 37.

первого (Ui)

второго (U)

девятого (Ug)

При обработке сигнала со скоростью 64 кбит/с по коду 01 часть слов с 1 по 4-й разряд записывается в регистр 36, а другая часть с 5 по 10-й разряд сразу записывается

в регистр 39 преобразователя 8 кода (фиг. 8) через соответствующие мультиплексоры 38 Далее 5-й разряд слова продвигается нэ 1 и разряд выделенного канала(ВК) в групповом тракте и т.д., 10-й разряд слова - на 6-й

разряд ВК, а на 7 и 8-й разряды ВК проклю- чаются нули. В (I + 1)-м ВК по коду 10 проключается слово с регистра 36, причем 1-й разряд слова проключает 1-й разряд ВК и т.д.. на 5-й разряд В К проключается 1, а на

разряды б, 7 и 8 - нули Таким образом соблюдается правильный порядок выдачи информации. Так при скорости входногосигнала 48 кбит/с промежуточное слово может иметь один из представленных ниже видов

Блок 6 синхронизации (фиг. 6) формиру ет набор необходимых импульсных последовательностей, управляющих процессами обработки поступающей информации По скольку скорость группового сигнала на выходе устройства должна состаЕ1лять 2048 кбис/с, то на вход девятиразрядного счетчика 21 поступает тактовая частота 2048 кГц от отдельного задающего генератора (не показанного на фиг 6) С помощью элементов И 26 и 27 формируются тактовые последовательности и t5

Тактовые последовательности обеспечивающие первичную обработку поступающих с входов устройства сигналов, формируются с помощью другого девятиразрядного счетчика 22. При этом элемент И 25 обеспечивает формирование сигнала Запрет Синхронная тактовая последовательность fao 5: f0 также поступает из отдельного задающего генератора Частота записи 1з 2336 кГц поступает на тактовый вход счетчика 22 через элемент И 24 Синфазная работа счетчиков 21 и 22 поддерживается с помощью триггеров 17 и 18, управляемых соответствующей тактовой последовательностью со счетчика 21 Элемент И 23 один раз за цикл деления счетчика 22 вырабатывает узкий импульс опрокидывающий триггеры 17 и 19 Единичный сигнал с триггера 19 переписывается на частоте fao в триггер 20 Появление единичного сигнала в тригге ре 20 фиксируется дифференцирующей цепью 28 узкий выходной импульс которой производит установку в исходное состояние триггеров 19 и 20 и счетчика 22

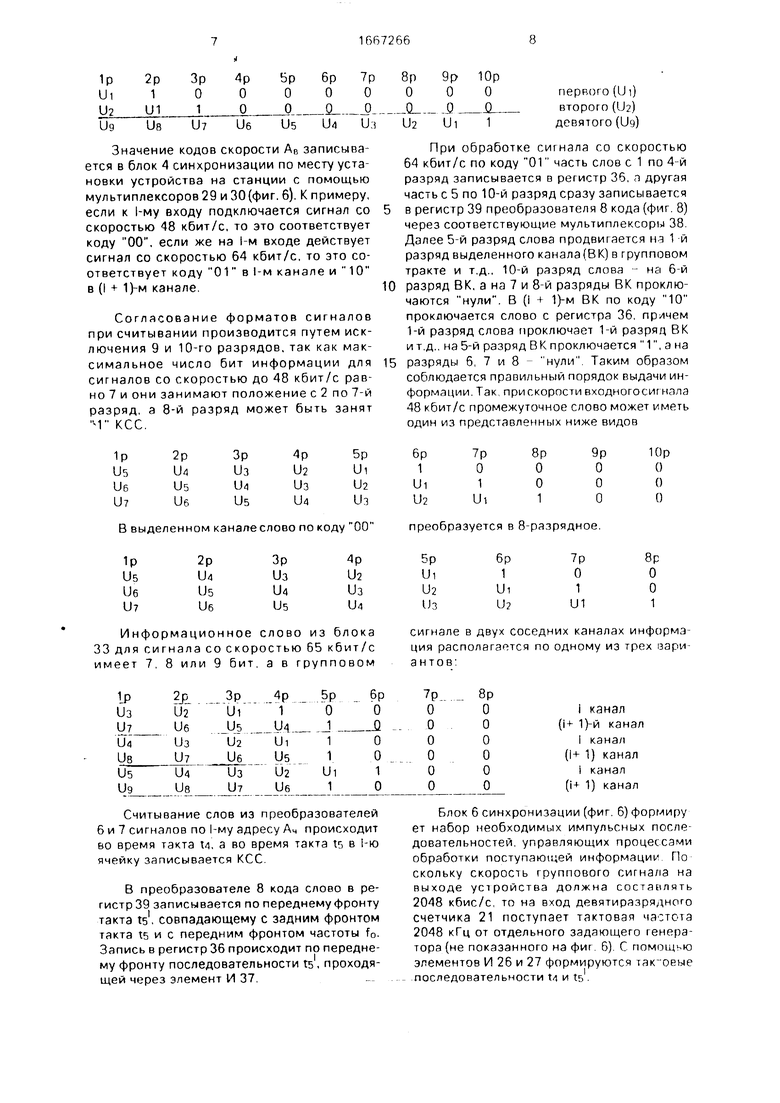

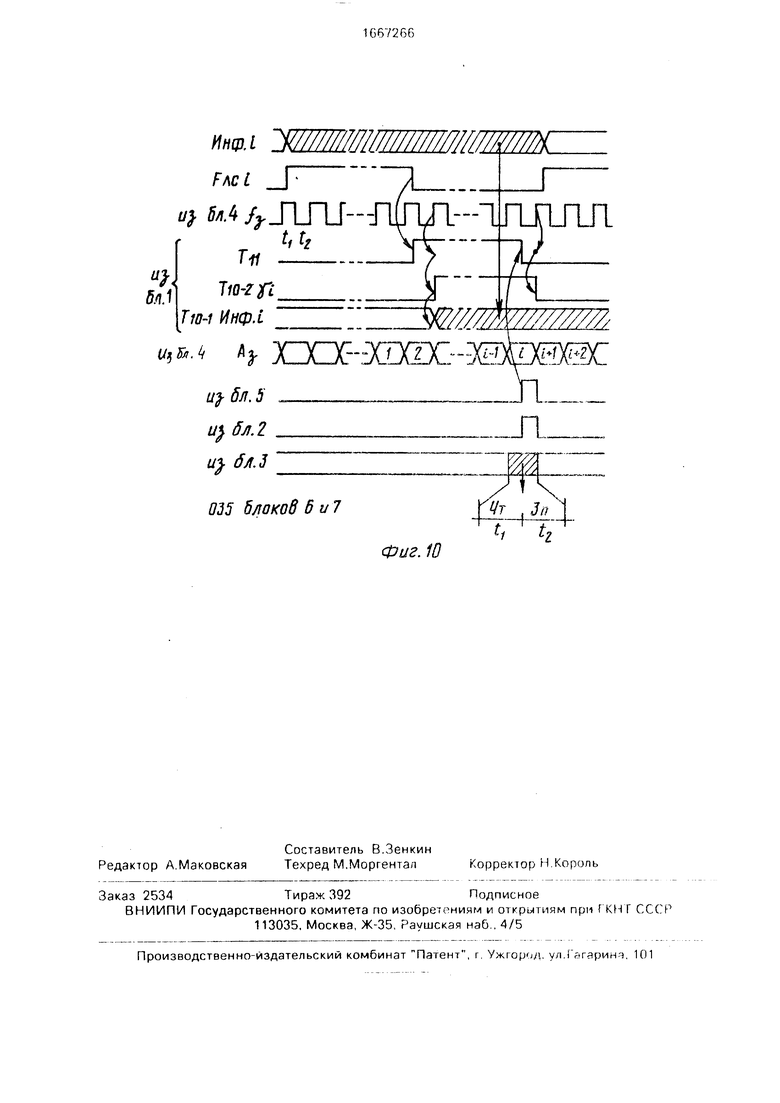

Диаграммы иллюстрируют вход ные цифровые сигналы, подключаемые к вхо- дам устройства диаграммы д 9 формируемого устройством труп нового сигнала, а диаграммы °т 9к от дельные тактовые последовательниц используемые при записи поступающей ин формации

Диаграммы, изображенные нч фи 10 иллюстрируют процесс обработка ин Формации поступающей на i вход VCT роиства

Формула изобретения Устройство сопряжения разноскорост- ных асинхронных цифровых сигналов содержащее блоки привязки дешифратор, 5 первый мультиплексор и блок синхронизации, вход которого является тактовым вхо дом устройства информационными входами которого являются первые входы блоков привязки, вторые входы и первые

0 выходы которых соединены соответственно с первым выходом блока синхронизации и первыми входами первого мультиплексора, отличающееся тем, что, с целью расширения диапазона скоростей цифро5 вых сигналов, введены второй мультиплексор, первый и второй преобразователи сигналов и преобразов гль кода, первые входы которого соединены с выходами первого и второго преобразователей сигналов пер0 вые вторые, третьи четвертые и пятые входы которых соединены соответственно с выходом второго мультиплексора выходы первого мультиплексора первым вторыми и третьими выходами блока синхронизации четвер5 тый и пятый выходы которого подключены к соответствующим вторым входам преобразователя кода и второму входу первого мультиплексора, третьи входы которого соединены с вторыми выходами блока синхронизации с

Q первыми входами втрогс м/ль иплек. ора и с перчыми входами дршифр торс выходы ко- тгрп, о соединены с соотБртствующл Ми третьим. вводами блоков привязки от ,; ые пи- )гды которых подключены к вторым БХОг, дам втрого мультип при второй вход дешифратора гр ДИНРН выходом первого мультиплексора четвертый вход которого подключен к первому выходу б/юка синхронизации, а выход преобразователя яв0 ляется выходом устройства

из/lQ

Инф.1 FAd

из б/г.2 cf

избЛ.Ь j ;

Инф.1

И//97./7

ь

из б/i.l „запрет

из бл.Зру

из 5л4 k-ь

Btnx.2

Инф.1Вбл.5

Фиг.2

12

V

Вых. -

Фиг.З

Фиг.Ь

кШ

Фиг. 5

Фиг. 6

scs

.00

г д

е ж

То | Г, | Tj i ft i i rg | г7 | те

g|/m3i4| Я П ЩЗЛ

h -«

tt

Фиг. 8

В 54 к5ит/с кбит/с кбит/С В 16 кбит/с

0 11 Выйекяетче каналы

Ja 20ЬВ кГи

групповой сигнал на выходе

Гц.у

h

Фиг. 9

нищ УШШШ1ШШШШ/ШШ

FACL р

ч} А / ЛГит t,t,

Тц ...

liu-zfi

Т10-1 Инф. I

и

t

Tff/////w/////

гтх--з(1ш:--шс№Ј

6л. 5.

Ј/; Af.2-Л,

иу

035 блоков б и 7

и

t

Tff/////w//////m

фиг. Ю

| Чуркин В.П | |||

| Асинхронные цифровые системы коммутации | |||

| М.: Радио и связь, 1985, с | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

Авторы

Даты

1991-07-30—Публикация

1988-06-08—Подача