мент И 23, мультиплексор-селектор 24 и генератор 26 импульсов. Сжатие выходной информации осуществляется сигнатурным анализатором, в состав которого входят сумматор 12 по моду1

Изобретение относится к импульсной технике и может быть использовано для автоматизированного контроля функционирования и диагностики цифровых блоков.

Целью изобретения является расширение функциональных йозможностей путем обеспечения возможности подачи по выбранным контактам объекта контроля взаимоинверсных (парафаз- ных) сигналовi формирования фиксированной временной диаграммы и подачи константных сигналов по заданным контактам.

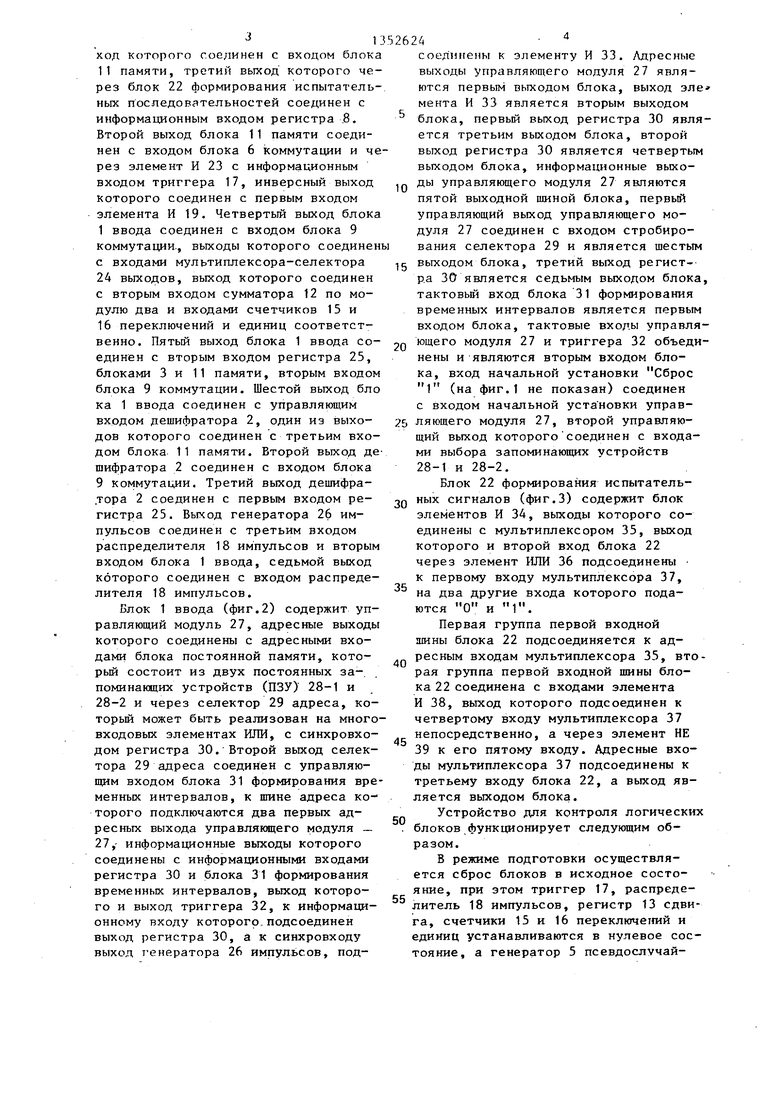

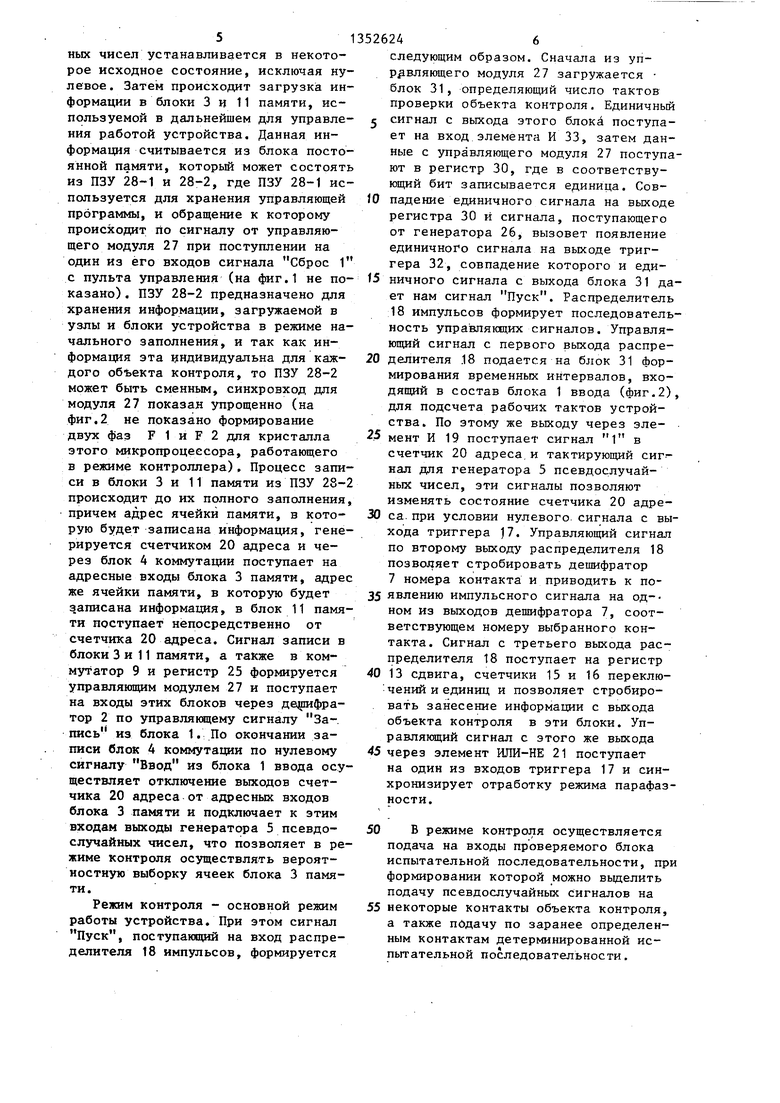

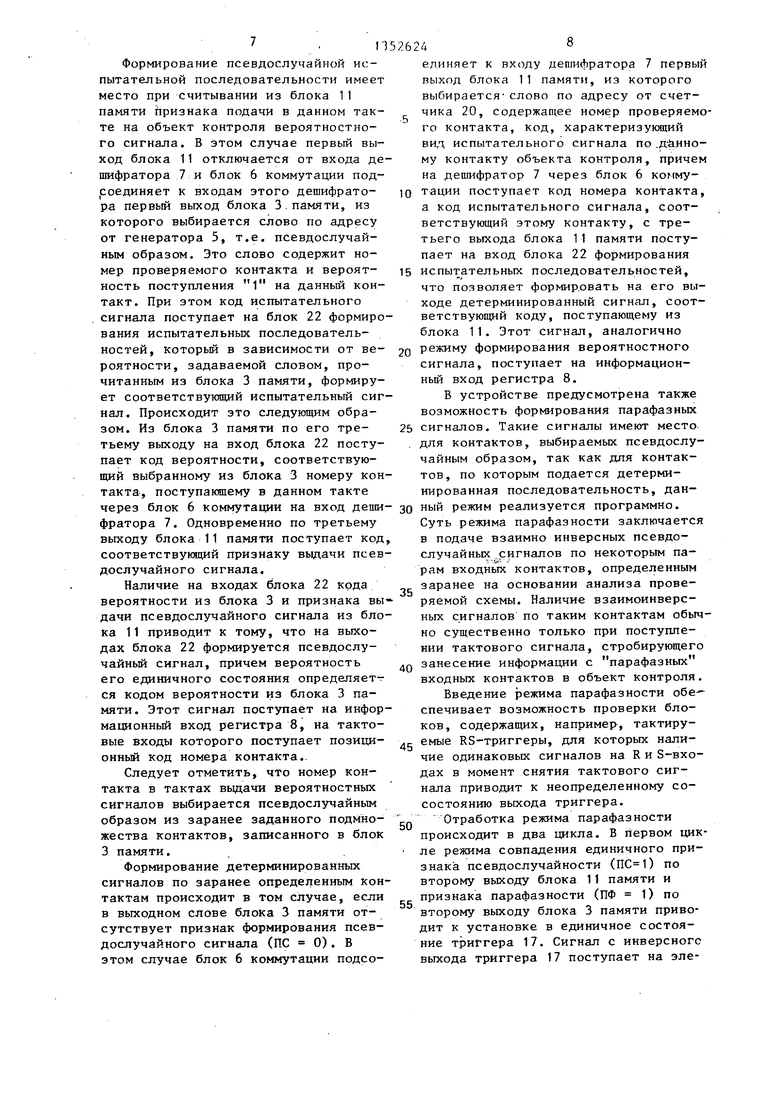

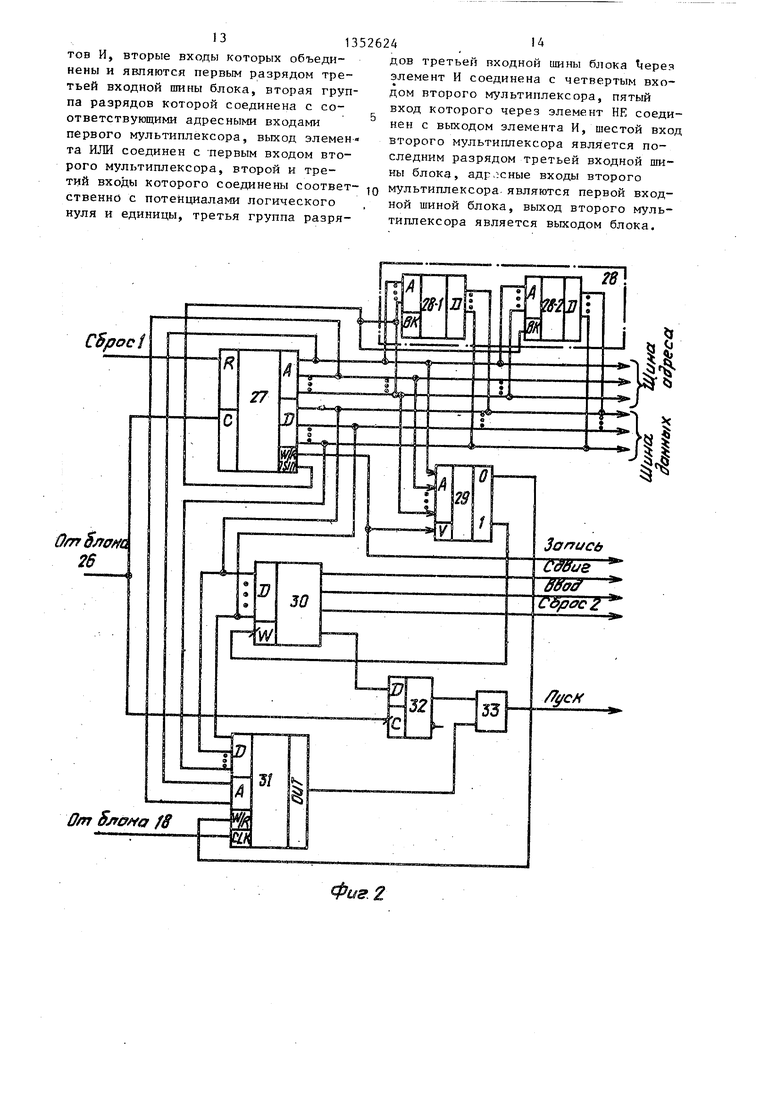

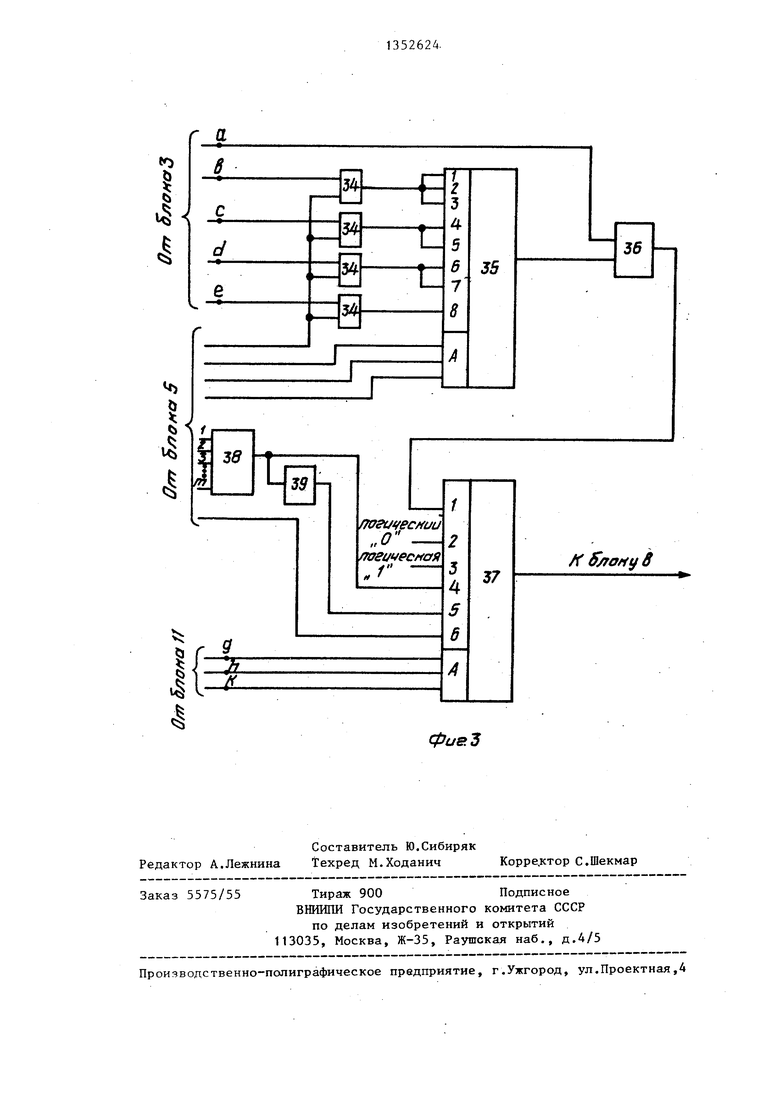

На фиг.1 представлена функциональная схема устройства для контроля логических блоков;, на фиг.2 - структурная схема блока фиг.З - структурная блока формирования испытательных сигналов.

Устройство для контроля логических блоков содержит (фиг.1) блок 1 ввода, дешифратор 2, первый блок 3 памятиj первый блок 4 коммутации, генератор 5 псевдослучайных чисел, второй блок 6 коммутации, дешифратор 7, первый регистр 8, третий блок 9 коммутации, объект 10 контроля,второй блок 11 памяти, сумматор 12 по модулю два, регистр 13 сдвига, блок 14 индикации, счетчик 15 переключений, счетчик 16 единиц, триггер U, распределитель 18 импульсов, элемент И 19, счетчик 20 адреса, элемен ИЛИ-НЕ 21, блок 22 формирования испытательных последовательностей, элемент И 23, мультиплексор-селектор 24 выходов, второй регистр 25, генератор 26 импульсов, причем первый выход блока 1 ввода через дешифратор 2 соединен с третьим входом блока 3 памяти, к первому входу которого через блок 4 коммутации подсоединен выход генератора 5 псевдослзгчайных чисел, выход которого соединен с вхолю два и регистр сдвига 13. Состояние регистра 13, счетчиков 15 и 1-6 отображается блоком 14 индикации для анализа оператором результатов контроля. 2 з.п. ф-лы, 3 ил.

дом блока 22 формирования испытательных последовательностей. Первьй выход блока 3 памяти через блок 6 ком- мутации соединен с информационным входом дешифратора 7, выходы которого соединены с тактовьтми входами регистра 8, выходы которого через коммутатор 9 соединены с входами объекта 10 контроля. Второй выход блока 3 памяти соединен с входом элемента И 23, а третий выход - с вторым входом блока 22 формирования испытательных последовательностей-. Первый выход

5 блока 11 памяти соединен с входом блока 6 коммутации. Выход сумматора 12 по модулю два через регистр 13 сдвига соединен со своим входом и входом блока 14 индикации. Выходы

0 счетчиков 15 и 16 переключений и единиц соответственно соединены с двумя другими входами блока 14 индикации. Второй выход блока 1 ввода соединен с первь1ми входами регистра 13

5 сдвига, счетчиков 15 и 16 переключений и единиц соответственно, входом генератора 5 псевдослучайных чисел, установочным входом триггера 17, выход которого соединен с входом бло0 ка 4 коммутации. Второй выход блока 1 ввода соединен с первым входом распределителя 18 импульсов, первый выход которого соединен с входами блока 1 ввода и элемента И 19, выход которого соединен с входом счетчика 20 адреса и входом генератора 5. Второй вькод распределителя 18 импульсов соединен с управляющим входом дешифратора 7, а третий его выход - с входаQ ми регистра 13 сдвига и счетчиков 15 и 16 переключений и единиц соответственно, а также через элемент ИЛИ-НЕ 21 с синхровходами триггера 17. Третий выход блока 1 ввода соединен с

. управляющим входом блока 4 коммутации и входом счетчика 20 адреса, вы5

ход которого соединен с входом блока 11 памяти, третий выход которого через блок 22 форьшровання испытательных последовательностей соединен с информационным входом регистра .8. Второй выход блока 11 памяти соединен с входом блока 6 коммутации и через элемент И 23 с информационным входом триггера 17, инверсный выход которого соединен с первым входом элемента И 19. Четвертый выход блока 1 ввода соединен с входом блока 9 коммутации., выходы которого соединен с входами мультиплексора-селектора 24 выходов, выход которого соединен с вторым входом сумматора 12 по модулю два и входами счетчиков 15 и 16 переключений и единиц соответственно. Пятый выход блока 1 ввода соединен с вторым входом регистра 25, блоками 3 и 11 памяти, вторым входом блока 9 коммутации. Шестой выход бло ка 1 ввода соединен с управляющим входом дешифратора 2, один из выходов которого соединен с третьим входом блока 11 памяти. Второй выход дешифратора 2 соединен с входом блока 9 коммутации. Третий выход дешифратора 2 соединен с первым входом регистра 25. Выход генератора 26 импульсов соединен с третьим входом распределителя 18 импульсов и вторым входом блока 1 ввода, седьмой выход которого соединен с входом распределителя 18 импульсов.

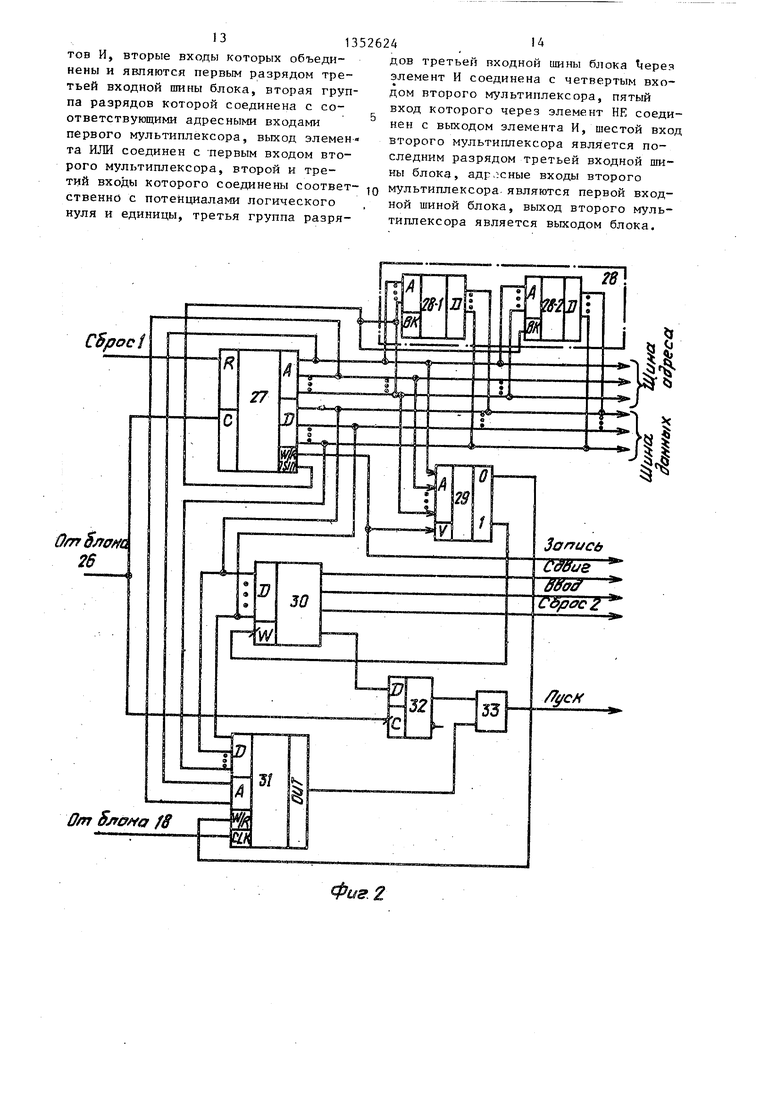

Блок 1 ввода (фиг.2) содержит управляющий модуль 27, адресные выходы которого соединены с адресными входами блока постоянной памяти, кото- рьй состоит из двух постоянных за-, поминающих устройств (ПЗУ) 28-1 и 28-2 и через селектор 29 адреса, ко- торьй может быть реализован на много входовых элементах ИЛИ, с синхровхо- дом регистра 30. Второй выход селектора 29 адреса соединен с управляю- входом блока 31 формирования временных интервалов, к шине адреса ко- торого подключаются два первых адресных выхода управляющего модуля - 27,- информационные выходы которого соединены с информационными входами регистра 30 и блока 31 формирования

В режиме подготовки осуществляется сброс блоков в исходное состояние, при этом триггер 17, распредевременных интервалов, выход КОТОРО- , щл- «vjn ,, , , и выход триггера 32, к информаци- литель 18 импульсов, регистр 13 сдвионному входу которого, подсоединен выход регистра 30, а к синхровходу выход 1 енератора 26 импульсов, под0

соединены к элементу И 33. Адресные выходы управляющего модуля 27 являются первым выходом блока, выход эле мента И 33 является вторым выходом блока, первый выход регистра 30 является третьим выходом блока, второй выход регистра 30 является четвертым выходом блока, информационные выходы управляющего модуля 27 являются пятой выходной щиной блока, первый управляющий выход управляющего модуля 27 соединен с входом стробиро- вания селектора 29 и является шестым

5 выходом блока, третий выход регистра 30 является седьмым выходом блока, тактовый вход блока 31 формирования временных интервалов является первым входом блока, тактовые входы управляQ ющего модуля 27 и триггера 32 объединены и являются вторым входом блока, вход начальной установки Сброс 1 (на фиг.1 не показан) соединен с входом начальной уста новки управ5 ляющего модуля 27, второй управляющий выход которого соединен с входами выбора запоминающих устройств 28-1 и 28-2.

Блок 22 формирования испытательных сигналов (фиг.З) содержит блок элементов И 34, выходы которого соединены с мультиплексором 35, выход которого и второй вход блока 22 через элемент ИЛИ 36 подсоединены к первому входу мультиплексора 37, на два другие входа которого пода- ются О и 1.

Первая группа первой входной шины блока 22 подсоединяется к адресным входам мультиплексора 35, вторая группа первой входной шины блока 22 соединена с входами элемента И 38, выход которого подсоединен к четвертому входу мультиплексора 37 непосредственно, а через элемент НЕ 39 к его пятому входу. Адресные входы мультиплексора 37 подсоединены к третьему входу блока 22, а выход является выходом блока.

Устройство для контроля логических блоков функционирует следующим образом.

В режиме подготовки осуществляется сброс блоков в исходное состояние, при этом триггер 17, распреде0

5

0

5

0

, щл- «vjn ,, , , , счетчики 15 и 16 переключений и единиц устанавливаются в нулевое состояние, а генератор 5 псевдослучайных чисел устанавливается в некоторое исходное состояние, исключая нулевое. Затем происходит загрузка информации в блоки 3 и 11 памяти, используемой в дальнейшем для управления работой устройства. Данная информация считывается из блока постоянной памяти, который может состоять из ПЗУ 28-1 и 28-2, где ПЗУ 28-1 используется для хранения управляющей программы, и обращение к которому происходит по сигналу от управляющего модуля 27 при поступлении на один из его входов сигнала Сброс 1 с пульта управления (на фиг.1 не показано) . ПЗУ 28-2 предназначено для хранения информации, загружаемой в узлы и блоки устройства в режиме начального заполнения, и так как информация эта индивидуальна для каждого об-ьекта контроля, то ПЗУ 28-2 может быть сменным, синхровход для модуля 27 показан упрощенно (на фиг.2 не показано формирование двух фаз F 1 и F 2 для кристалла этого микропроцессора, работающего в режиме контроллера), Процесс записи в блоки 3 и 11 памяти из ПЗУ 28-2 происходит до их полного заполнения, причем адрес ячейки памяти, в которую будет записана информахщя, генерируется счетчиком 20 адреса и через блок 4 коммутации поступает на адресные входы блока 3 памяти, адрес же ячейки памяти, в которую будет записана информация, в блок 11 памяти поступает непосредственно от счетчика 20 адреса. Сигнал записи в блоки 3 и 11 памяти, а также в коммутатор 9 и регистр 25 формируется управляющим модулем 27 и поступает на входы этих блоков через де5шфра- тор 2 по управляющему сигналу Запись из блока 1. По окончании записи блок 4 коммутации по нулевому сигналу Ввод из блока 1 ввода осуществляет отключение выходов счетчика 20 адреса от адресных входов блока 3 памяти и подключает к этим входам выходы генератора 5 псевдослучайных чисел, что позволяет в режиме контроля осуществлять вероятностную выборку ячеек блока 3 памяти.

Режим контроля - основной режим работы устройства. При этом сигнал Пуск, поступающий на вход распределителя 18 импульсов, формируется

следующим образом. Сначала из уп- рдвляющего модуля 27 загружается блок 31, определяющий число тактов проверки объекта контроля. Единичный

сигнал с выхода этого блока поступает на вход элемента И 33, затем данные с управляющего модуля 27 поступают в регистр 30, где в соответствующий бит записывается единица. Совпадение единичного сигнала на выходе регистра 30 и сигнала, поступающего от генератора 26, вызовет появление единичного сигнала на выходе триггера 32, совпадение которого и единичного сигнала с выхода блока 31 дает нам сигнал Пуск. Распределитель 18 импульсов формирует последовательность управляющих сигналов. Управляющий сигнал с первого выхода распределителя .18 подается на блок 31 формирования временных интервалов, входящий в состав блока 1 ввода (фиг.2), для подсчета рабочих тактов устройства. По этому же выходу через элемент И 19 поступает сигнал 1 в

счетчик 20 адреса, и тактирующий сигнал для генератора 5 псевдослучайных чисел, эти сигналы позволяют изменять состояние счетчика 20 адреса.при условии нулевого сигнала с выхода триггера J7. Управляюпщй сигнал по второму выходу распределителя 18 позволяет стробировать дешифратор 7 номера контакта и приводить к появлению импульсного сигнала на од-- ном из выходов дешифратора 7, соответствующем номеру выбранного контакта. Сигнал с третьего выхода распределителя 18 поступает на регистр

13 сдвига, счетчики 15 и 16 переключений и единиц и позволяет стробировать занесение информации с выхода объекта контроля в эти блоки. Управляющий сигнал с этого же выхода

через элемент ИЛИ-НЕ 21 поступает на один из входов триггера 17 и синхронизирует отработку режима парафаз- ности.

В режиме контроля осуществляется подача на входы проверяемого блока испытательной последовательности, при формировании которой можно выделить подачу псевдослучайных Сигналов на

некоторые контакты объекта контроля, а также пОдачу по заранее определенным контактам детерминированной испытательной последовательности.

. f 526248

Формирование псевдослучайной ис-единяет к входу дешифратора 7 первый пытательной последовательности имеетвыход блока 11 памяти, из которого место при считывании из блока 1 1выбирается- слово по адресу от счет- памяти признака подачи в данном так-чика 20, содержащее номер проверяемо- те на объект контроля вероятностно- го контакта, код, характеризующий го сигнала. В этом случае первый вы-вид испытательного сигнала по .д-анно- ход блока 11 отключается от входа де-му контакту объекта контроля, причем шифратора 7 и блок 6 коммутации под-на дешифратор 7 через блок 6 комму- роединяет к входам этого дешифрато- ютации поступает код номера контакта, ра первый выход блока 3. памяти, иза код испытательного сигнала, соот- которого выбирается слово по адресуветствующий этому контакту, с трест генератора 5, т.е. псевдослучай-тьего выхода блока 11 памяти посту- ным образом. Это слово содержит но-пает на вход блока 22 формирования мер проверяемого контакта и вероят- igиспытательных последовательностей, ность поступления 1 на данный кон-что позволяет формировать на его вы- такт. При этом код испытательногоходе детерминированный сигнал, соот- сигнала поступает на блок 22 формиро-ветствующий коду, поступающему из вания испытательных последователь-блока 11. Этот сигнал, аналогично костей, который в зависимости от ве- 20Режиму формирования вероятностного роятности, задаваемой словом, про-сигнала, поступает на информацион- читанным из блока 3 памяти, формиру-ный вход регистра 8. ет соответствующий испытательный сиг- В устройстве предусмотрена также нал. Происходит это следующим обра-возможность формирования парафазных зом. Из блока 3 памяти по его тре- 25сигналов. Такие сигналы имеют место тьему выходу на вход блока 22 посту- .для контактов, выбираемых псевдослу- пает код вероятности, соответствую-чайным образом, так как для контак- щий выбранному из блока 3 номеру кон-тов, по которым подается детерми- такта, поступающему в данном тактенированная последовательность, дан- через блок 6 коммутации на вход деши- режим реализуется программно, фратора 7. Одновременно по третьемуСуть режима парафазности заключается выходу блока 11 памяти поступает код,в подаче взаимно инверсных псевдосоответствующий признаку выдачи псев-случайных.ригналов по некоторым па- дослучайного сигнала.рам входных контактов, определенным Наличие на входах блока 22 кодазаранее на основании анализа прозе- вероятности из блока 3 и признака вы-ряемой схемы. Наличие взаимоинверс- дачи псевдослучайного сигнала из бло-ных сигналов по таким контактам обыч- ка 11 приводит к тому, что на выхо-но существенно только при поступле- дах блока 22 формируется псевдослу-нии тактового сигнала, стробирующего чайньй сигнал, причем вероятность занесение информации с парафазных его единичного состояния определяет-входных контактов в объект контроля. ся кодом вероятности из блока 3 па- Введение режима парафазности обе- мяти. Этот сигнал поступает на инфор-спечивает возможность проверки бло- мационный вход регистра 8, на такто-ков, содержащих, например, тактиру- вые входы которого поступает позици- ,емые RS-триггеры, для которых нали- онньй код номера контакта..чие одинаковых сигналов на RиS-BXOСледует отметить, что номер кон-дах в момент снятия тактового сиг- такта в тактах вьщачи вероятностныхнала приводит к неопределенному со- сигналов выбирается псевдослучайнымсостоянию выхода триггера.

образом из заранее заданного подмно- .. Отработка режима парафазности

ьи

жества контактов, записанного в блокпроисходит в два цикла. В первом цик3 памяти.. ле режима совпадения единичного приФормирование детерминированныхзнака псевдослучайности () по

сигналов по заранее определенным кон-второму выходу блока 11 памяти и

тактам происходит в том случае, еслипризнака парафазности (ПФ 1) по

в выходном слове блока 3 памяти от-второму выходу блока 3 памяти привосутствует признак формирования псев-дит к установке в единичное состоядослучайного сигнала (ПС 0) . Вние триггера 17. Сигнал с инверсного

этом случае блок 6 коммутации подсо-выхода триггера 17 поступает на элемент И 19, запрещая тем самым для второго цикла отработки парафазно- сти стробирование счетчика 20 адреса и генератора 5 псевдослучайных чисел. Во втором цикле сигнал с прямого выхода триггера 17 поступает на блок 4 коммутации, формируя единичное значение старшего бита кода адреса в блоке 3 памяти.

Таким образом, по сформированному адресу во втором цикле из блока 3 выбирается слово из старшей по-- ловины ячеек данного блока, т.е. если в первом цикле бьшо обращение к ячейке г из младшей половины блока 3 (нулевое состояние старшего разряда адреса), то во вторбм цикле отработки парафазнести происходит обращение к ячейке блока 3 с адресам (г + ), где емкость (количество ячеек) блока 3 памяти.

Мультиплексор-селектор 24 выходов выбирает из множества выходов объекта контроля выходной контакт, инфор- магщонная последовательность с которого поступает, например, на сигнатурный анализатор и в последствии сравнивается с эталонным значением.Управление указанным мультиплексором осуществляется перед началом режима контроля записью в регистр 25 управляющего кода с шины данных (блок 1 ввода) по сигналу дешифратора 2. Аналогично прототипу, входяш 1й в состав устройства счетчик переключений позволяет обнаруживать одиночные логические неисправности константного типа. Счетчик 16 единиц обеспечивает возможность определения вероятностных характеристик выходной последовательности, сжатие выходной информации осуществляется сигнатурным анализатором, в состав которого входит сумматор 12 по модулю два и регистр 13 сдвига. Состояния регистра 13, счетчиков 15 и 16 переключений и единиц отображаются блоком 14 инди- Kaiijin для анализа оператором результатов контроля.

Формула изобретения

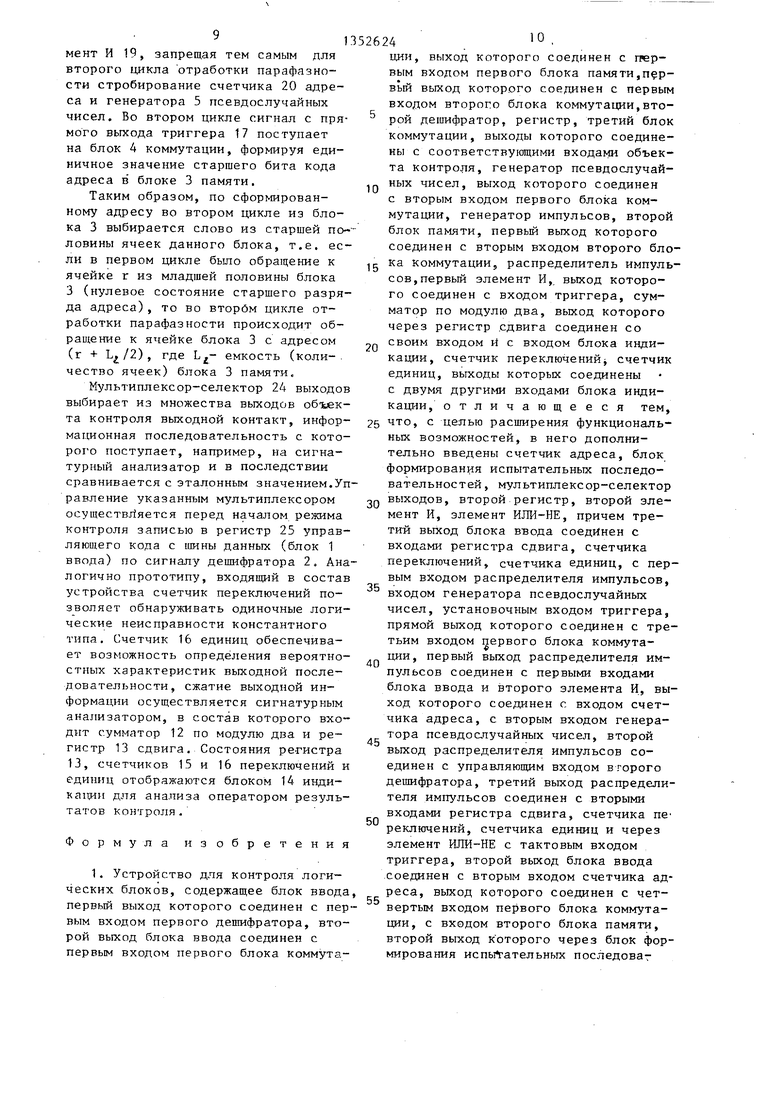

1. Устройство для контроля логических блоков, содержащее блок ввода, первый выход которого соединен с первым входом первого дешифратора, второй выход блока ввода соединен с первым входом первого блока коммута1352624 ° .

или, выход которого соединен с ггер- вым входом первого блока памяти, вьй выход которого соединен с первым входом второго блока коммутации,вто- рой дешифратор, регистр, третий блок коммутации, выходы которого соединены с соответствующими входами объекта контроля, генератор псевдослучай10

с вторым входом первого блока коммутации, генератор импульсов, второй блок памяти, первьй выход которого соединен с вторым входом второго ка коммутации, распределитель импульсов, первый элемент И, выход которого соединен с входом триггера, сумматор по модулю два, выход которого через регистр сдвига соединен со

У„ своим входом rt с входом блока индикации, счетчик переключенийj счетчик единиц, выходы которых соединены с двумя другими входами блока индикации, отличающееся тем,

25 что, с целью расширения функциональных возможностей, в него дополнительно введены счетчик адреса, блок формирования испытательных последовательностей , мультиплексор-селектор

2Q выходов, второй регистр, второй элемент И, элемент ИЛИ-НЕ, причем третий выход блока ввода соединен с входами регистра сдвига, счетчика переключений, счетчика единиц, с первым входом распределителя импульсов, входом генератора псевдослучайных чисел, установочным входом триггера, прямой выход которого соединен с третьим входом первого блока коммутации, первый выход распределителя импульсов соединен с первыми входами блока ввода и второго элемента И, выход которого соединен с входом счетчика адреса, с вторым входом генератора псевдослучайных чисел, второй выход распределителя импульсов соединен с управляющим входом вгорого дешифратора, третий выход распределителя импульсов соединен с вторыми входами регистра сдвига, счетчика пе реключений, счетчика единиц и через элемент ИЛИ-НЕ с тактовым входом триггера, второй выход блока ввода соединен с вторым входом счетчика адреса, выход которого соединен с четвертым входом первого блока коммутации, с входом второго блока памяти, второй выход к оторого через блок формирования испьЛгательных последоваг

35

40

45

50

55

с вторым входом первого блока коммутации, генератор импульсов, второй блок памяти, первьй выход которого соединен с вторым входом второго блока коммутации, распределитель импульсов, первый элемент И, выход которого соединен с входом триггера, сумматор по модулю два, выход которого через регистр сдвига соединен со

своим входом rt с входом блока индикации, счетчик переключенийj счетчик единиц, выходы которых соединены с двумя другими входами блока индикации, отличающееся тем,

что, с целью расширения функциональных возможностей, в него дополнительно введены счетчик адреса, блок формирования испытательных последовательностей , мультиплексор-селектор

выходов, второй регистр, второй элемент И, элемент ИЛИ-НЕ, причем третий выход блока ввода соединен с входами регистра сдвига, счетчика переключений, счетчика единиц, с первым входом распределителя импульсов, входом генератора псевдослучайных чисел, установочным входом триггера, прямой выход которого соединен с третьим входом первого блока коммутации, первый выход распределителя импульсов соединен с первыми входами блока ввода и второго элемента И, выход которого соединен с входом счетчика адреса, с вторым входом генератора псевдослучайных чисел, второй выход распределителя импульсов соединен с управляющим входом вгорого дешифратора, третий выход распределителя импульсов соединен с вторыми входами регистра сдвига, счетчика пе реключений, счетчика единиц и через элемент ИЛИ-НЕ с тактовым входом триггера, второй выход блока ввода соединен с вторым входом счетчика адреса, выход которого соединен с четвертым входом первого блока коммутации, с входом второго блока памяти, второй выход к оторого через блок формирования испьЛгательных последоваг

тельностей соединен с информационным входом первого регистра, третий выход второго блока памяти соединен с третьим входом второго блока коммутации и с первым входом первого элемента И, инверсный выход триггера соединен с вторым входом второго элемента И, четвертый выход блока ввода соединен с входом третьего блока коммутации, выходы которого соединены с входами мультиплексора-селектора выходов, выход которого соединен с вторым входом сумматора по модулю два и третьими входами счетчика пе- р-еключений и счетчика единиц, пятьш выход блока ввода соединен с входом второго регистра, с вторым входом второго блока памяти, с входом третьего блока коммутации, вторым .входом первого блока памяти, второй выход которого соединен с входом первого элемента И, третий выход первого блока памяти соединен с вторым входом блока формирования испытательных последовательностей,/шестой выход блока ввода соединен с управляющим входом первого дешифратора, первый вьгход которого соединен с третьим входом второго блока памяти, второй выход первого дешифратора соединен с третьим входом третьего блока Коммутации, третий выход первого дешифратора соединен с вторым входом второго регистра, четвертьй выход первого дешифратора соединен с третьим входом первого блока памяти, седьмой выход блока ввода соединен с вторым входом распределителя импульсов, выход генератора импульсов соединен с третьим входом распределителя импульсов и вторым входом блока ввода, первый выход которого соединен с третьим входом счетчика адреса, выход второго регистра соедй- нен с адресными входами мультиплексора-селектора выходов, выходы второго дешифратора через первый регистр соединены с информационными входами третьего коммутатора.

2, Устройство по п.1, .о т л и ч а ю щ е е с я тем, что блок ввода co-i держит управляющий модуль, блок постоянной памяти, селектор адреса, регистр, блок формирования временных интервалов, триггер, элемент И,причем адресные выходы управляющего модуля соединены с адресными входами блока постоянной памяти, с адресны0

5

0

мн входами селектора адреса, с адресными входами блока формирования временных интервалов, выход которого соединен с первым входом эл емента И, второй вход которого соединен с прямым выходом триггера, синхровход KO-S- торого объединен с синхровходом управляющего модуля и является вторым входом блока, адресные выходы управляющего модуля являются первой выходной шиной блока, информационные выходы управляющего модуля соединены с информационными выходами блока постоянной памяти, информационными входами регистра, информационными входами блока формирования временных интервалов и являются пятой выходной шиной блока, первый управляющий выход управляющего модуля соединен с входом стробирования селектора адреса и является шестым вьгходом блока, второй управляющий выход управляющего модуля соединен с входом вы- 5 бора блока постоянной памяти, пер- вьм выход селектора адреса соединен с первым управляющим входом блока формирования временных интервалов, второй управляющий вход которого является первым входом блока, второй выход селектора адреса соединен с синхровходом регистра, первый выход которого является четвертым выходом блока, второй выход регистра является BTopbiM выходом блока, третий выход регистра является третьим выходом блока, четвертьй выход регистра соединен с информационным входом триггера, выход элемента И является седьмым выходом блока, вход начальной установки управляющего модуля является входом начальной установки блока.

3. Устройство по п.1, о т л и - 5 чающееся тем, что блок формирования испытательных сигналов содержит блок элементов И, первый и второй мультиплексоры, элемент ИЛИ, элемент И, элемент НЕ, причем выхо- 0 ды блока элементов И соединены с соответствующими информационными входами первого мультиплексора, выход которого соединен с первым входом элемента ИЛИ, второй вход которого 5 является первым разрядом второй

входной шины блока, остальные разря-: ды Которой соединены с соответствующими первыми входами блока элемен0

5

0

тов и, вторые входы которых объединены и являются первым разрядом третьей входной шины блока, вторая группа разрядов которой соединена с соответствующими адресными входами первого мультиплексора, выход элемен та ИЖ соединен с первым входом второго мультиплексора, второй и третий входы которого соединены соответ- Q мультиплексора являются первой вход- ственно с потенциалами логического , ной шиной блока, выход второго муль- нуля и единицы, третья группа разря- типлексора является выходом блока.

дов третьей входной шины блока ерез элемент И соединена с четвертым входом второго мультиплексора, пятый вход которого через элемент НЕ соединен с выходом элемента И, шестой вход второго мультиплексора является последним разрядом третьей входной шины блока, адр -сные входы второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Генератор псевдослучайных испытательных последовательностей | 1984 |

|

SU1226621A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

Изобретение относится к импульсной технике и может быть использовано для автоматизированного контроля функционирования и диагностики цифровых блоков. Цель изобретения - расширение функциональных возможностей- достигается путем подачи по выбранным контактам объекта контроля па- рафазных сигналов, Лормиррвания фиксированной временной диаграммы и подачи константных сигналов по заданным контактам. Устройство содержит блок 1 ввода, дешифратор 2, блоки 3 и 11 памяти, блоки 4, 6 и 9 коммутации, генератор 5 псевдослучайных чисел, дешифратор 7, регистры 8 и 25, объект 10 контроля, сумматор 12 по модулю 2, регистр 13 сдвига, блок 14 индикации, счетчик 15 переключений, счетчик 16 единиц, триггер 17, распределитель 18 импульс.ов, элемент И 19, счетчик 20 адреса, элемент ИЖ-НЕ 21, блок 22 формирования испытательных последовательностей,элеi (Л :лэ сд VO О5 ND it

CSpoci

Om ffffffO. 26

От /8

Физ. 2

Составитель Ю.Сибиряк Редактор А.Лежнина Техред М.Ходанич Корре.ктор С.Шекмар

5575/55

Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

фиеЗ

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1985-12-30—Подача