Изобретение относится к электросвязи и может быть использовано в устройствах передачи и коммутации цифровых систем связи.

Известно устройство объединения цифровых сигналов передачи данных в групповой цифровой поток с целью передачи их на коммутационное поле и на станцию для ско- ростей передачи асинхронных до 1,2 кбит/с и синхронных до 48 кбит/с сигналов с использованием канала передачи 64 кбит/с.

Недостатком этого устройства является ограниченный диапазон сопрягаемых цифровых сигналов с групповым трактом, а именно, устройство объединяет асинхронные сигналы, имеющие скорости передачи до 1,2 кбит/с, а синхронные - до 48 кбит/с.

Известны также устройства для скоростей передачи асинхронных сигналов до 9,6 кбит/с и синхронных сигналов до 48 кбит/с также с использованием канала передачи 64

кбит/с.

Наряду с указанными скоростями передачи цифровых сигналов используются модемы для скорости передачи от 48 кбит/с до 164 кбит/с, модемы для передачи 144

кбит/с для формата 2В + D, где В 64 кбит/с, D 16 кбит/с, 80 кбит/с - для формата В + D и др.

Известны также устройства со скоростью передачи 64/128/192/256 кбит/с. Кроме того, существует задача сопряжения групповых трактов с убпервичными трактами, в частности сопряжения первичной ЦСП тактами ИКМ-30 с субпервичными трактами 480 кбит/с и другими.

Построение каналов и станций коммутации на базе одинаковых (цифровых) методов позволяет осуществить так называемую интеграцию систем коммутации и передачи, исключающую необходимость разуплотнения цифровых каналов на станциях коммутации и применения различных коммутационных полей для различных скоростей передачи. Поэтому различные цифровые сигналы объединяются в единый групповой цифровой поток, решаемый предлагаемым устройством. При интеграции систем коммутации и передачи станции коммутации и каналы пб сути дела представляют собой временные цифровые системы. Взаимодействие этих систем требует соглаел

С

Я

СЛ

со

00 Оч

сования их во времени, т.е. синхронизации, причем синхронное уплотнение является частным случаем асинхронного.

Типы мультиплексоров для скоростей передачи до 48 кбит/с, где описаны функ- ции мультиплексоров с частотным уплотнением (МЧУ), с временным уплотнением (МВУ), со статическим временным уплотнением (МСВУ). МЧУ применяется для аналоговых линий МВУ и МСВУ для синхронных каналов связи.

Наиболее близким по технической сущности к предлагаемому является устройство сопряжения разноскоростных асинхронных цифровых сигналов, содержащее входные регистры, блок синхронизации, мультиплексор информационных сигналов, мультиплексор сигналов требований и дешифратор. Вторые выходы входных регистров подключены к первым входам мульти- плексора сигналов требований, тактовым входом устройства является блок синхронизации, первый выход которого подключен к третьему входу мультиплексора сигналов требований.

Недостатком этого устройства является то, что устройство сопрягается с групповым цифровым потоком линии связи со скоростями передачи до 64 кбит/с включительно. В настоящее время существуют линии связи со скоростями передачи до 256 кбит/с, групповые тракты - со скоростью передачи 480 кбит/с и др. Кроме того, с развитием цифровых систем передачи скорости передачи имеют тенденцию к росту.

Цель изобретения - расширение диапазона скоростей цифровых сигналов.

Поставленная цель достигается тем, что в устройство сопряжения асинхронных разноскоростных цифровых сигналов, содер- жащее входные регистры, блок синхронизации, мультиплексор информационных сигналов, мультиплексор сигналов требований и дешифратор, входы которого соединены с первыми входами входных ре- гистров, вторые входы котбрых являются информационными входами устройства, первые выходы входных регистров соединены с первыми входами мультиплексора информационных сигналов, вторые выходы входных регистров подключены к первым входам мультиплексора сигналов требований, тактовым входом устройства является блок синхронизации, первый выход которого подключен к третьему входу мультиплек- сора сигналов требований, введены блок памяти линий, первый и второй блоки памяти бит, первый и второй блоки памяти канала, первый и второй блоки согласования скорости, первые входы которых соединены

с первым выходом мультиплексора информационных сигналов, вторые входы первого и второго блоков согласования скорости объединены с первыми входами дешифратора, первого и второго блоков памяти бит и подключены к выходу мультиплексора сигналов требований, третьи входы первого и второго блоков согласования скорости соединены с выходами соответствующих первого и второго блоков памяти канала, четвертые входы первого и второго блоков согласования скорости объединены с вторым входом дешифратора, четвертым входом мультиплексора сигналов требований и третьим входом мультиплексора информационных сигналов, первыми входами первого и второго блоков памяти канала, вторыми входами первого и второго блоков памяти бит и подключены к выходу блока памяти линий, выходы первого и второго блоков памяти биг соединены с вторыми входами соответствующих первого и второго блоков памяти канала, второй выход блока синхронизации соединен с входом блока памяти линий, третий выход блока синхронизации подключен к третьим входам первых блока памяти бит и блока памяти канала и пятым входом первого блока согласования скорости, четвертый выход блока синхрониза - ции соединен с третьими входами вторых блока памяти бит и блока памяти канала, пятым входом второго блока согласования скорости, пятый и шестой выходы блока синхронизации подключены соответственно к шестым входам первого и второго блоков согласования скорости, выходы которых объединены и являются выходом устройства,

Сущность изобретения состоит в расширении диапазона скоростей цифровых сигналов.

При помощи предлагаемого устройства совместно с известными цифровыми коммутационными системами проектируются ЦСК для коммутации разноскоростных асинхронных цифровых сигналов без потери бит, а также для объединения и передачи между станциями в едином групповом цифровом потоке разноскоростных асинхронных цифровых потоков. Комплекс этих устройств позволяет осуществлять цифровую передачу и коммутацию в любой конфигурации сети как в чисто цифровой, так и в смешанной без потери бит.

Введение в устройство блока памяти линий и его связей позволяет равномерно распределять время опроса входных линий и тем самым при повышении скорости входных линий временная диаграмма опроса остается прежней Введение двух блоков

памяти бит и их связей позволяет подсчитывать число принятых информационных бит. Введение двух блоков памяти каналов и их связей позволяет задействовать подряд необходимое число каналов в групповом цифровом потоке. Введение двух блоков согласования скорости и их связей позволяет для входных линий связи согласовывать скорости с каналами индивидуально при помощи вставок, принимать и выдавать информационные потоки в последовательном коде, что снижает объем оборудования устройства,

Пру использовании устройства достигается расширение диапазона скоростей цифровых сигналов.

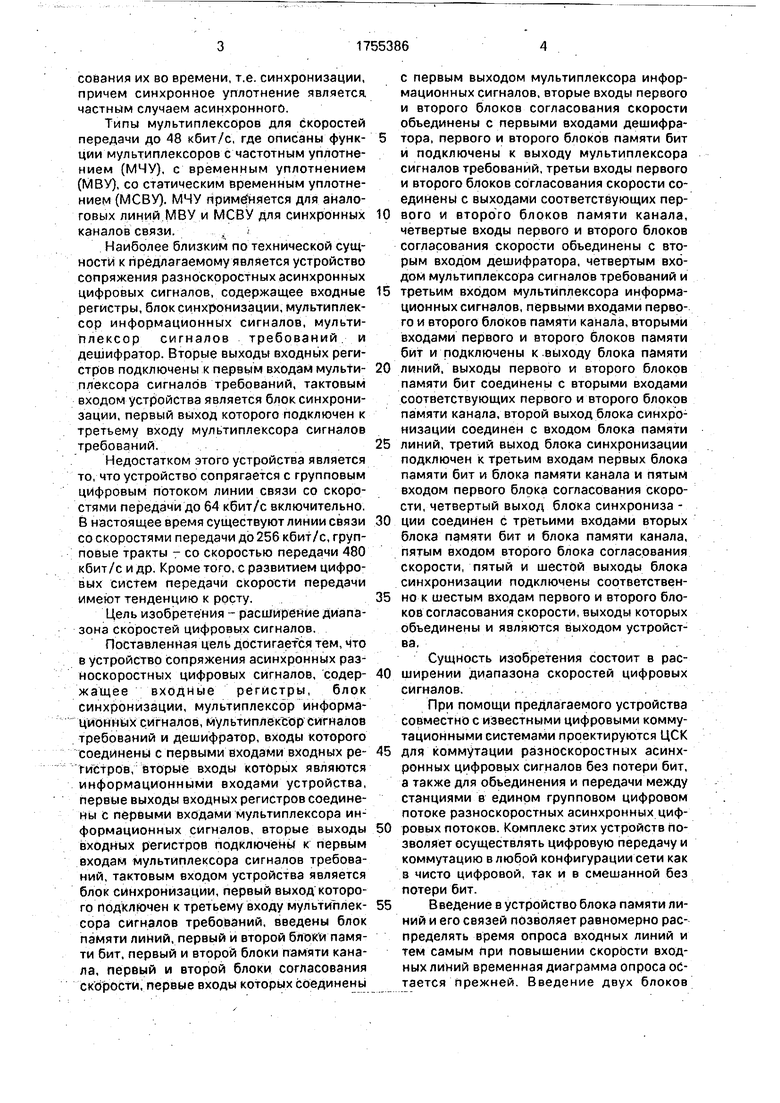

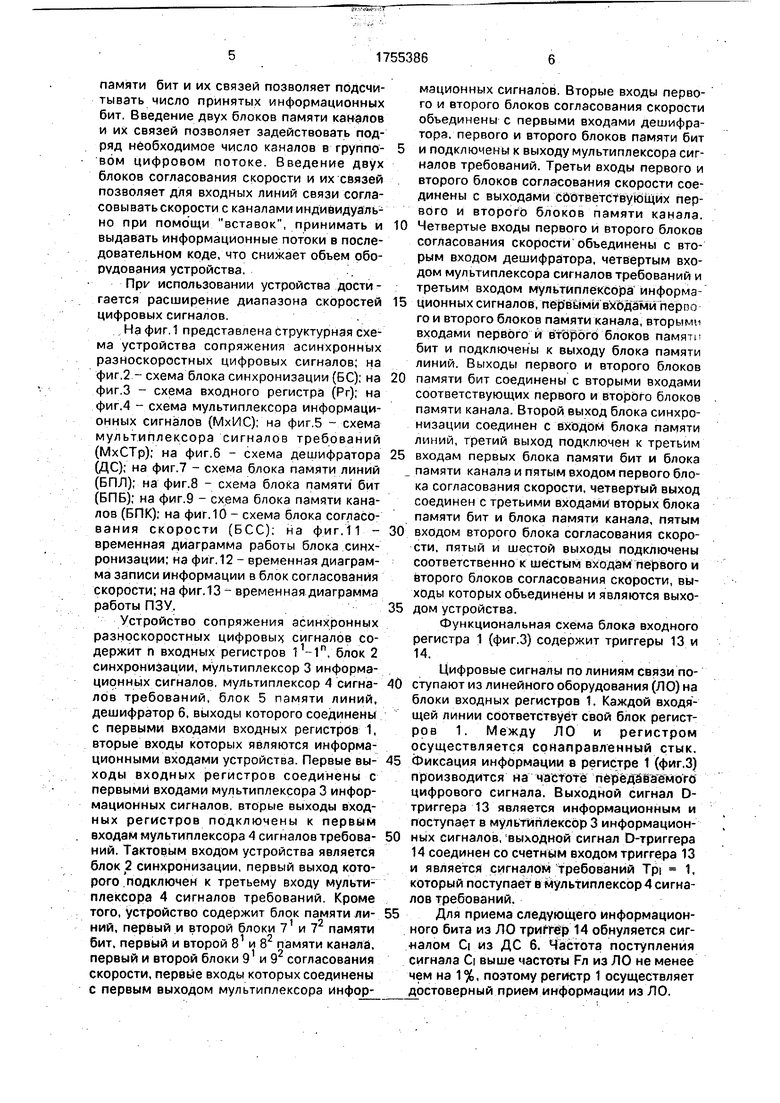

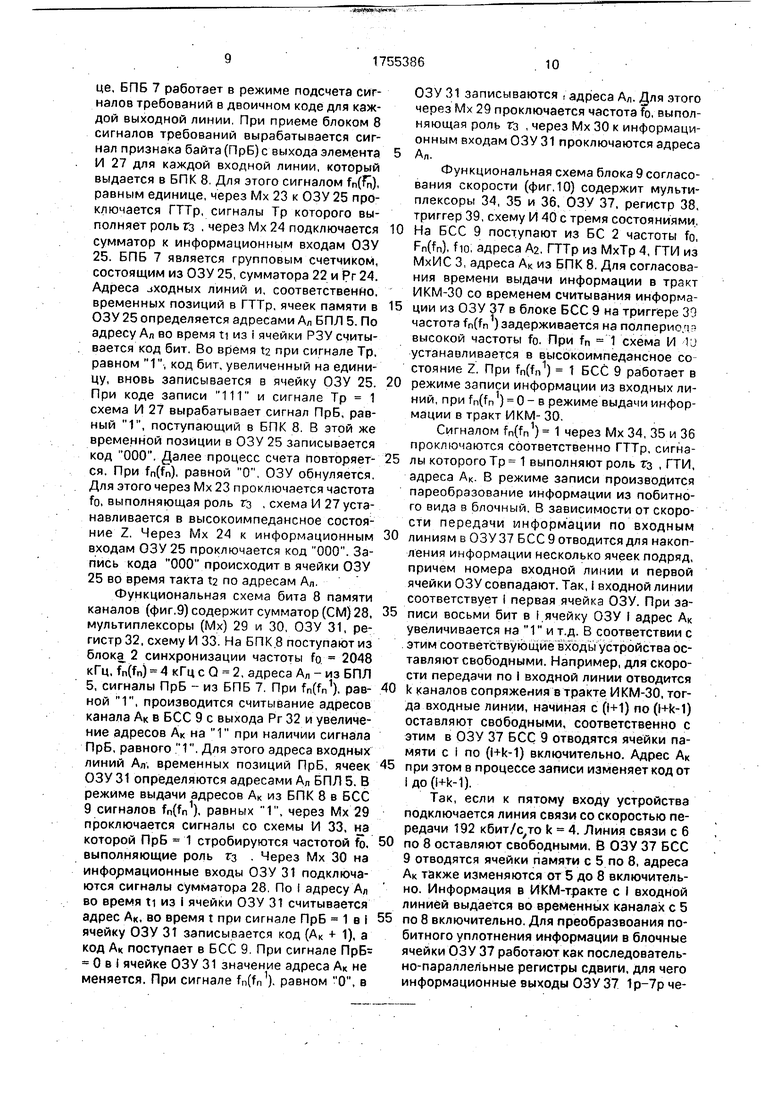

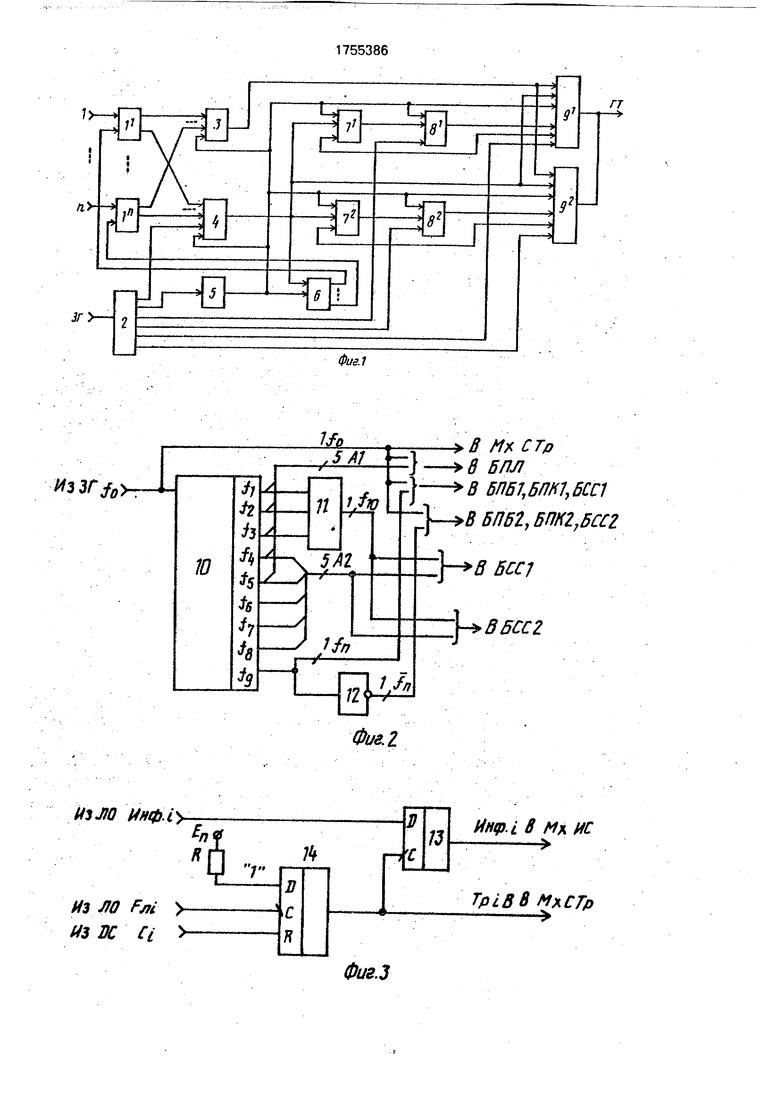

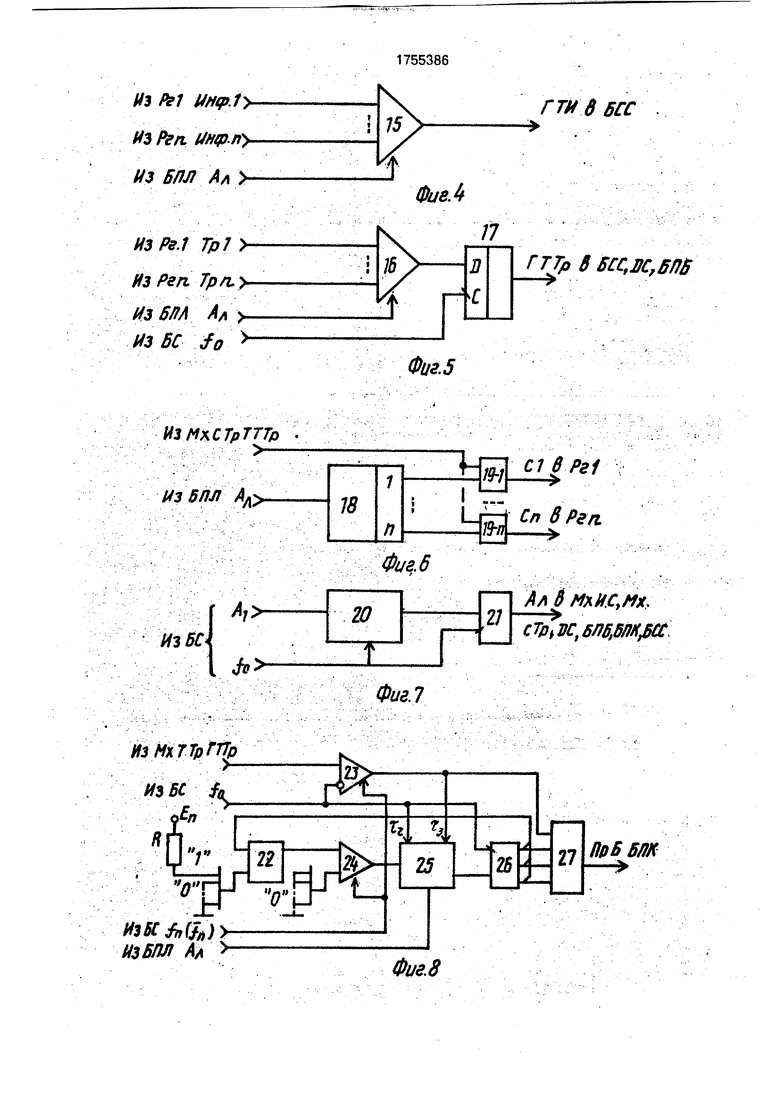

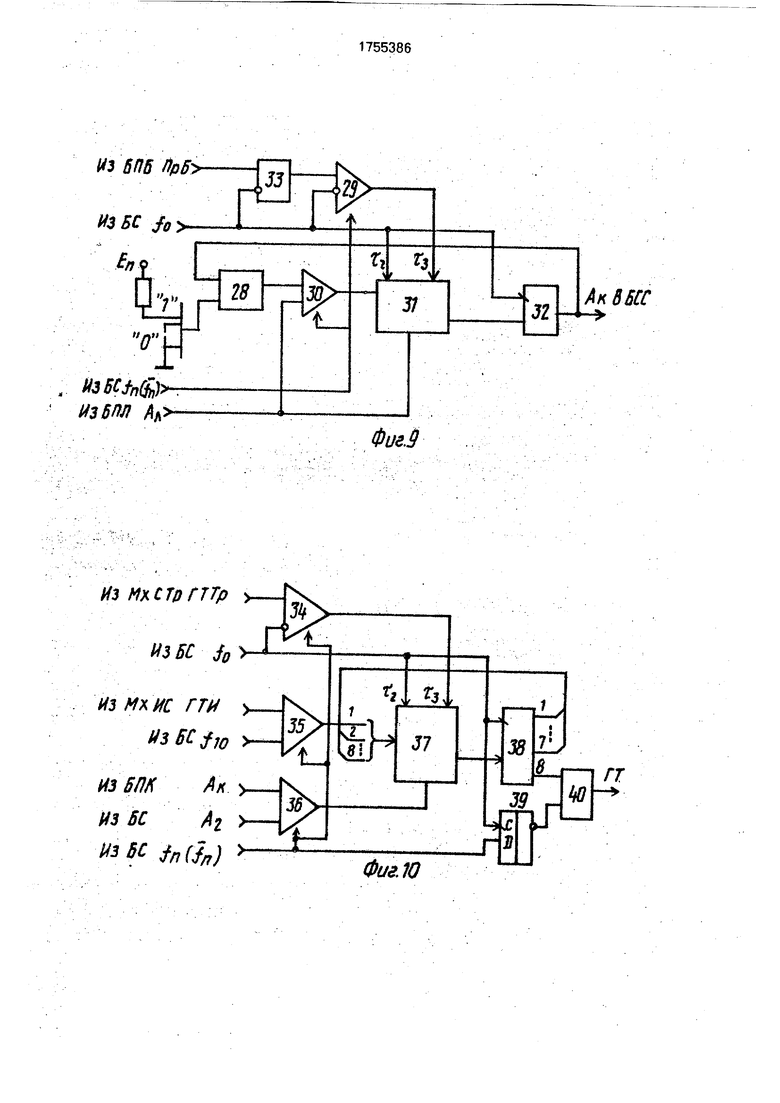

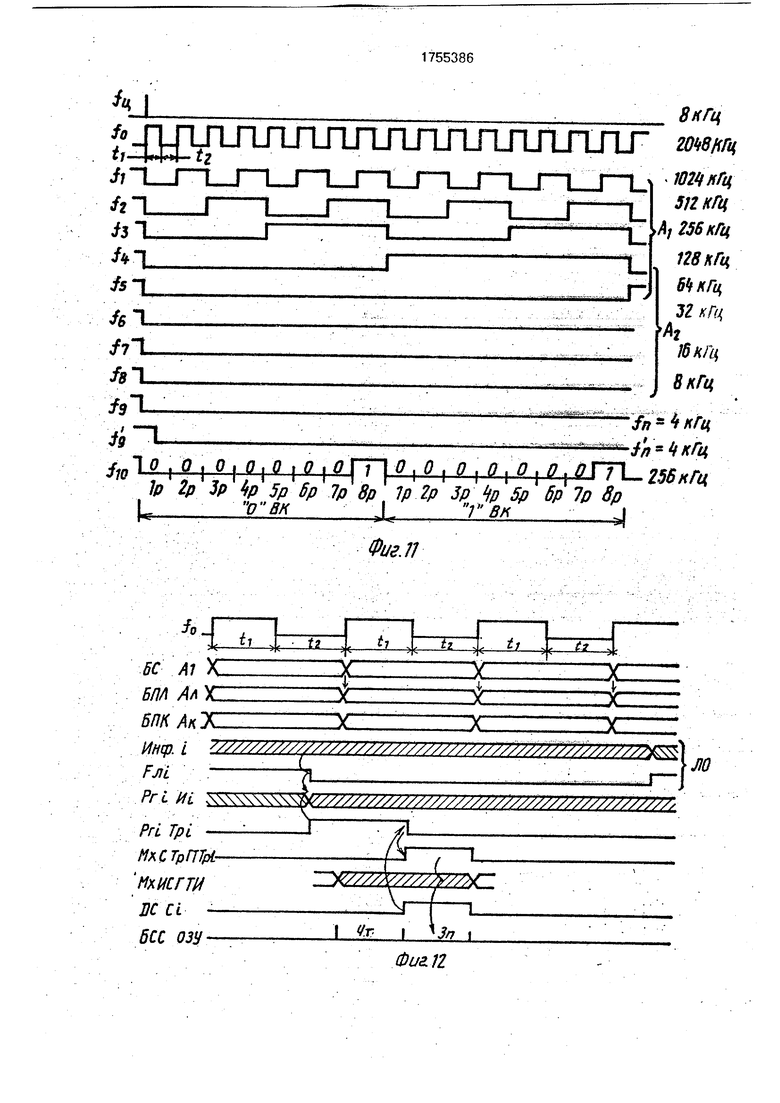

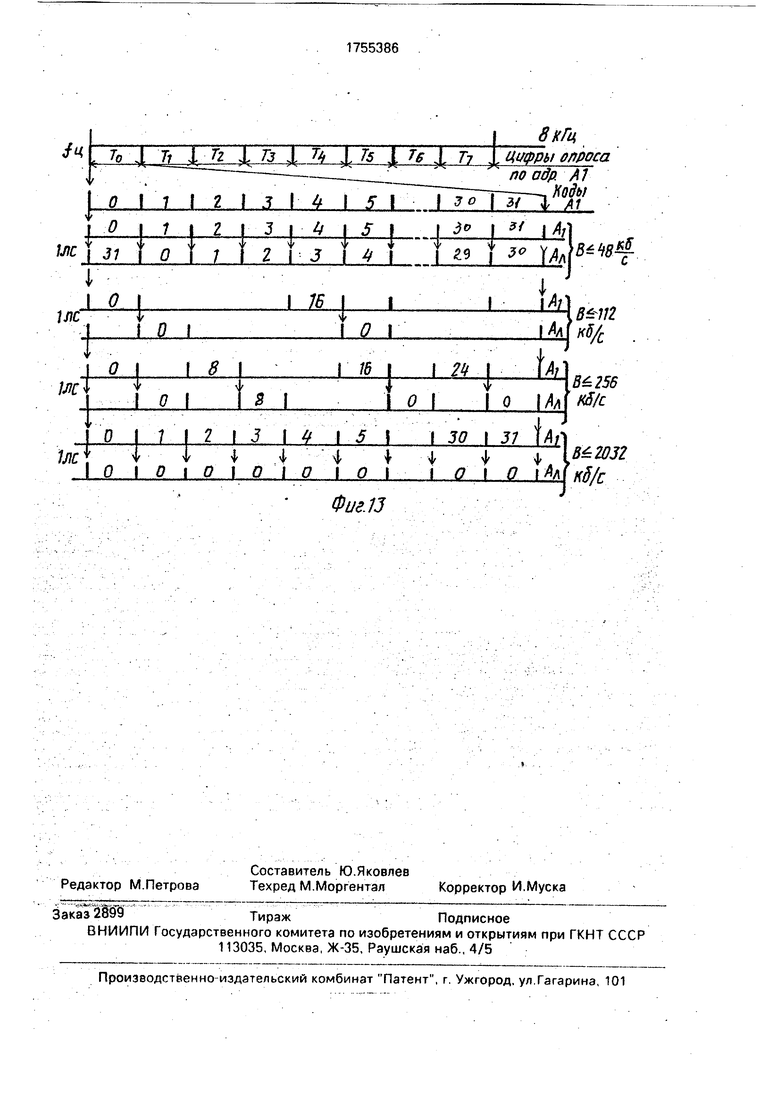

На фиг. 1 представлена структурная схема устройства сопряжения асинхронных разноскоростных цифровых сигналов; на фиг.2 - схема блока синхронизации (БС); на фиг.З - схема входного регистра (Рг); на фиг.4 - схема мультиплексора информационных сигналов (МхИС); на фиг.5 - схема мультиплексора сигналов требований (МхСТр); на фиг.6 - схема дешифратора (ДС); на фиг.7 - схема блока памяти линий (БПЛ); на фиг.8 - схема блока памяти бит (БПБ); на фиг.9 - схема блока памяти каналов (Б Л К); на фиг. 10 - схема блока согласования скорости (БСС); на фиг.11 - временная диаграмма работы блока синхронизации; на фиг.12 - временная диаграмма записи информации в блок согласования скорости; на фиг.13 - временная диаграмма работы ПЗУ.

Устройство сопряжения асинхронных разноскоростных цифровых сигналов содержит п входных регистров 11-1п, блок 2 синхронизации, мультиплексор 3 информационных сигналов, мультиплексор 4 сигналов требований, блок 5 памяти линий, дешифратор б, выходы которого соединены с первыми входами входных регистров 1, вторые входы которых являются информационными входами устройства. Первые выходы входных регистров соединены с первыми входами мультиплексора 3 информационных сигналов, вторые выходы входных регистров подключены к первым входам мультиплексора 4 сигналов требований. Тактовым входом устройства является блок 2 синхронизации, первый выход которого подключен к третьему входу мультиплексора 4 сигналов требований. Кроме того, устройство содержит блок памяти линий, первый и второй блоки 71 и 72 памяти бит, первый и второй 81 и 82 памяти канала, первый и второй блоки 91 и 92 согласования скорости, первые входы которых соединены с первым выходом мультиплексора информационных сигналов. Вторые входы первого и второго блоков согласования скорости объединены с первыми входами дешифратора, первого и второго блоков памяти бит

и подключены к выходу мультиплексора сигналов требований. Третьи входы первого и второго блоков согласования скорости соединены с выходами соответствующих первого и второго блоков памяти канала.

0 Четвертые входы первого и второго блоков согласования скорости объединены с вторым входом дешифратора, четвертым входом мультиплексора сигналов требований и третьим входом мультиплексора информа5 ционных сигналов, первыми входами пероо го и второго блоков памяти канала, вторыми входами первого и второго блоков памятг бит и подключены к выходу блока памяти линий. Выходы первого и второго блоков

0 памяти бит соединены с вторыми входами соответствующих первого и второго блоков памяти канала. Второй выход блока синхронизации соединен с входом блока памяти линий, третий выход подключен к третьим

5 входам первых блока памяти бит и блока памяти канала и пятым входом первого блока согласования скорости, четвертый выход соединен с третьими входами вторых блока памяти бит и блока памяти канала, пятым

0 входом второго блока согласования скорости, пятый и шестой выходы подключены соответственно к шестым входам первого и второго блоков согласования скорости, выходы которых объединены и являются выхо5 дом устройства.

Функциональная схема блока входного регистра 1 (фиг.З) содержит триггеры 13 и 14.

Цифровые сигналы по линиям связи по0 ступают из линейного оборудования (ЛО) на блоки входных регистров 1. Каждой входя - щей линии соответствует свой блок регистров 1. Между ЛО и регистром осуществляется сонаправленный стык.

5 Фиксация информации а регистре 1 (фиг.З) производится на частоте передаваемого цифрового сигнала. Выходной сигнал D- триггера 13 является информационным и поступает в мультиплексор 3 информацион0 ных сигналов, выходной сигнал D-триггера 14 соединен со счетным входом триггера 13 и является сигналом требований Tpi 1, который поступает в мультиплексор 4 сигналов требований.

5 Для приема следующего информационного бита из ЛО триггер 14 обнуляется сигналом Ci из ДС 6. Частота поступления сигнала Ci выше частоты Рл из ЛО не менее чем на 1%, поэтому регистр 1 осуществляет достоверный прием информации из ЛО.

Функциональная схема блока 2 синхронизации (фиг.2) содержит счетчик 10, схему И 11 и схему НЕ 12.

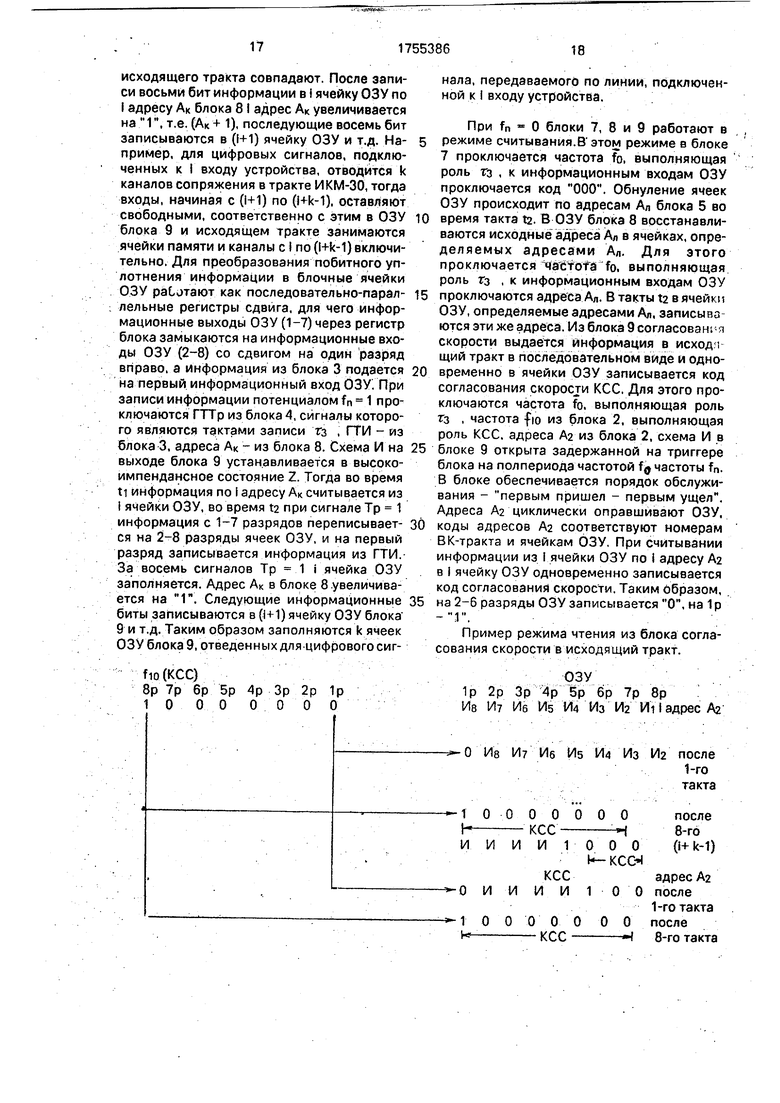

Блок 2 синхронизации (фиг.2) формирует набор необходимых импульсных после- 5 довательностей, управляющих процессами обработки поступающей информации. Поскольку скорость группового сигнала на выходе устройства должна составлять 2048 кбит/с, то на вход девятиразрядного счетчи- 10 ка 10 поступает тактовая частота 2048 кГц от отдельного задающего генератора (ЗГ). С помощью элементов И 11 и НЕ 12 формируются тактовые последовательности f ю и fn, с помощью счетчика 10 формируются часто- 15 ты fi-fg. Частоты fi-fs используются в качестве адресов AI, которые подаются в блок БПЛ 5 для считывания адресов опроса входных линий. Частота смены адресов AI равна 2048 кГц.20

Частота fV-fa используется в качестве адресов А2, при помощи которых информация считывается из БСС 9 во временные каналы исходящего группового потока. Частота смены адресов А2 равна 256 кГц. Час- 25 тота fg со скважностью 6 2 используется в качестве частоты переключения fn линеек блоков БПБ 7, ВПК 8, БСС 9 с режима записи информации из входных линий на режим выдачи информации в исходящий группе- 30 вой поток и наоборот. Частота fn подается в блоки БПБ 71, БПК8Т, БСС9 .частота fn через схему 12 - во вторые блоки БПБ 72, ВПК 82, БСС 92. Частота fo - 2048 кГц используется для привязки асинхронной 35 информации, поступающей из ЛО, к работе устройства. Положительные полупериоды частоты fo используются в качестве тактов ti, во время которых происходит считывание информации из ОЗУ устройства. Отрица- 40 тельные полупериоды частоты fo используются в качестве тактов tz, во время которых происходит запись информации в ОЗУ устройства. Частота fio, вырабатываемая элементом И 11, реализующим функцию И fiX45 f2-f3. имеет частоту следования 256 кГц и используется в качестве кода согласования скорости (КСС). записываемого в ОЗУ и БСС 9, у которого разряды с 1р по 7р имеют потенциал О. 8р- 1. Частота fio подается 50 в БСС 0. Диаграмма работы БС 2 изображена на фиг 11.

Функциональная схема мультиплексора 3 информационных сигналов (МхСИ) изо- бражена на фиг.4. МхСИ 3 содержит 55 мультиплексор 15, на который поступает информация из п регистров 1 и адреса линий Ая из блока 5 памяти линий (БПЛ). МхИС 3 осуществляет побитное объединение в групповой тракт информации (ГТИ) по адре-

сам Ал. Так, по коду адреса Ал, равному 1, проключается информация в первую временную позицию (ВП) из первого Рг по коду п Ал в п ВП из п Рг Информация по ГТИ поступает в БСС 9.

Функциональная схема мультиплексора 4 сигналов требований (МхСТр 4) изобра- жена на фиг.5. МхСТр 4 содержит мультиплексор (Мх) 16 и триггер (Та) 17. На МхСТр 4 из регистров 11-1п поступают сигналы требований Tpi, адреса Ал - из БПЛ 5 и высокая частота fo 2048 кГц - из блока 2 синхронизации. МхСТр 4 осуществляет побитное обьединениев групповой тракт сигналов требований I lip и их привязку к высокой частоте fo устройства. Привязка необходима из-за асинхронного стыка между ЛО и устройством. Так, по коду адреса Ал, равному 1, проключается информация в первую ВП из первого Рг 1 и по заднему фронту фиксируется в Т4 17 по коду п Ал в п ВП из п Рг 1 и по заднему фронту fo фиксируется в Т2 17.Сигналы требований по ГТТр поступают в БСС 9, БПБ 7 и дешифратор 6.

Функциональная схема дешифратора 6 (фиг.б) содержит собственно дешифратор 18 и схемы И 19-1-19-п. На ДС 6 поступают адреса Ал из БПЛ 5, на схемы И 19 - сигналы требований по ГТТо из МхТо 4. ДС 6 вырабатывает сигналы для обнуления триггеров 14 требований в регистрах Рг 11 - Рг 1П. Так, сигнал Ci с выхода схемы И 19-1, сигнал Сп с выхода схемы И 19-п поступают соответственно на Рг 11 и Рг 1 при коде адреса Ал соответственно Г или п и при наличии сигналов требований Тр 1 1 при Трп 1. Частота поступления сигнала Ct на Рп задается частотой повторения адреса Аль

Функциональная схема блока 5 памяти линий (фиг.7) содержит ПЗУ 20 и регистр 21. На ПЗУ 20 поступают текущие адреса At из блока 2 синхронизации с частотой 2048 кГц и высокая частота fo, равная 2048 кГц.

Адреса Ал с выхода регистра 21 поступают в блоки МхСИ 3, МхСТр 4, ДС 6, БСС 9, ВПК 8 и БПБ 7. Считывание адресов Ал производится во время отрицательного полупериода частоты fo, фиксация в регистре 21 - передним фронтом частоты fo.

Функциональная схема блока 7 памяти бит (фиг.8) содержит сумматор (СМ) 22, мультиплексоры (Мх) 23, 24, ОЗУ 25, регистр 26 (Рг), схему И 27. На БПБ 7 поступает из БС 2 частота fo для формирования тактов чтения т и записи тз в ОЗУ 25. Частоты fn(fn) для управления режимами работами блоков, адреса Ал поступают из БЛЛ 5, ГТТр - из мультиплексора 4 сигналов требований. При значении сигналов fn(fn), равных едини1755386

10

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 2011 |

|

RU2450432C1 |

| СПОСОБ ДИНАМИЧЕСКОГО РЕЗЕРВИРОВАНИЯ И РАСПРЕДЕЛЕНИЯ ПРОПУСКНОЙ СПОСОБНОСТИ КАНАЛОВ В СПУТНИКОВОЙ СЕТИ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2015 |

|

RU2614983C1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СТАНЦИЯ ОБМЕНА ДОКУМЕНТАЛЬНОЙ ИНФОРМАЦИЕЙ | 2011 |

|

RU2474869C1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

Изобретение относится к устройствам сопряжения асинхронных разноскоростных цифровых сигналов и может быть использовано в электросвязи. Сущность изобретения1 устройство содержит входные регистры, блок синхронизации, мультиплексор информационных сигналов, мультиплексор сигналов требований, блок памяти линий, первый и второй блоки памяти бит, дешифратор, первый и второй блоки памяти канала и первый и второй блоки согласования скорости. 3 табл., 13 ил.

це, БПБ 7 работает в режиме подсчета сигналов требований в двоичном коде для каждой выходной линии При приеме блоком 8 сигналов требований вырабатывается сигнал признака байта (ПрБ) с выхода элемента И 27 для каждой входной линии, который выдается в БПК 8 Для этого сигналом fn(Fn), равным единице, через Мх 23 к ОЗУ 25 про- ключается ГТТр, сигналы Тр которого выполняет роль гз . через Мх 24 подключается сумматор к информационным входам ОЗУ 25. БПБ 7 является групповым счетчиком, состоящим из ОЗУ 25, сумматора 22 и Рг 24. Адреса входных линий и, соответственно, временных позиций в ГТТр, ячеек памяти в ОЗУ 25 определяется адресами Ал БПЛ 5. По адресу Ал во время ti из i ячейки РЗУ считывается код бит. Во время t2 при сигнале Тр. равном 1, код бит, увеличенный на единицу, вновь записывается в ячейку ОЗУ 25. При коде записи 111 и сигнале Тр 1 схема И 27 вырабатывает сигнал ПрБ, равный 1, поступающий в БПК 8 В этой же временной позиции в ОЗУ 25 записывается код 000. Далее процесс счета повторяет- ся. При fn(fn), равной О ОЗУ обнуляется, Для этого через Мх 23 проключается частота fo, выполняющая роль гз , схема И 27 устанавливается в высокоимпедансное состояние Z. Через Мх 24 к информационным входам ОЗУ 25 проключается код 000. Запись кода 000 происходит в ячейки ОЗУ 25 во время такта t2 по адресам Ал

Функциональная схема бита 8 памяти каналов (фиг.9) содержит сумматор (СМ) 28, мультиплексоры (Мх) 29 и 30, ОЗУ 31, регистр 32, схему И 33. На БПК 8 поступают из блока 2 синхронизации частоты fo 2048 кГц, fn(fn) 4 кГц с Q 2, адреса Ал - из БПЛ 5, сигналы ПрБ - из БПБ 7 При fn(fn1), рав- ной 1, производится считывание адресов канала Ак в БСС 9 с выхода Рг 32 и увеличение адресов Ак на 1 при наличии сигнала ПрБ, равного 1. Для этого адреса входных линий Ал, временных позиций ПрБ, ячеек ОЗУ 31 определяются адресами Ал БПЛ 5. В режиме выдачи адресов Ак из БПК 8 в БСС 9 сигналов fn(fn1), равных 1, через Мх 29 проключается сигналы со схемы И 33, на которой ПрБ 1 стробируются частотой fo, выполняющие роль гз . Через Мх 30 на информационные входы ОЗУ 31 подключаются сигналы сумматора 28 По I адресу Ал во время ti из i ячейки ОЗУ 31 считывается адрес АК, во время t при сигнале ПрБ 1 в i ячейку ОЗУ 31 записывается код (Ак + 1), а код Ак поступает в БСС 9 При сигнале ПрБ 0 в I ячейке ОЗУ 31 значение адреса Ак не меняется. При сигнале fn(fn ). равном О, в

ОЗУ 31 записываются . адреса Ал. Для этого через Мх 29 проключается частота fo, выполняющая роль Гз , через Мх 30 к информационным входам ОЗУ 31 проключаются адреса Ал.

Функциональная схема блока 9 согласования скорости (фиг. 10) содержит мультиплексоры 34, 35 и 36, ОЗУ 37, регистр 38, триггер 39, схему И 40 с тремя состояниями На БСС 9 поступают из БС 2 частоты fo, Fn(fn), f ю, адреса А2. ГТТр из МхТр 4, ГТИ из МхИС 3, адреса Ак из БПК 8. Для согласования времени выдачи информации в тракт ИКМ-30 со временем считывания информации из ОЗУ 37 в блоке БСС 9 на триггере 31 частота fn(fn1) задерживается на полпериогп высокой частоты fo. При fn 1 схема И U устанавливается в высокоимпедансное со стояние 2. При fn(fn1) 1 БСС 9 работает в режиме записи информации из входных линий, при fn(fn ) 0 - в режиме выдачи информации в тракт ИКМ- 30

Сигналом fn(fn1) 1 через Мх 34, 35 и 36 прокяючаются соответственно ГТТр, сигналы которого Тр 1 выполняют роль Тз , ГТИ, адреса Ак В режиме записи производится пареобразование информации из побитного вида в блочный. В зависимости от скорости передачи информации по входным линиям в ОЗУ 37 БСС 9 отводится для накопления информации несколько ячеек подряд, причем номера входной линии и первой ячейки ОЗУ совпадают. Так, i входной линии соответствует i первая ячейка ОЗУ. При записи восьми бит в i ячейку ОЗУ i адрес Ак увеличивается на 1 и т.д. В соответствии с этим соответствующие входы устройства оставляют свободными. Например, для скорости передачи по i входной линии отводится k каналов сопряжения в тракте ИКМ-30, тогда входные линии, начиная с (1+1) по (i+k-1) оставляют свободными, соответственно с этим в ОЗУ 37 БСС 9 отводятся ячейки памяти с 1 по (i+k-1) включительно. Адрес Ак при этом в процессе записи изменяет код от I до (i+k-1).

Так, если к пятому входу устройства подключается линия связи со скоростью передачи 192 кбит/с,то k 4. Линия связи с 6 по 8 оставляют свободными, В ОЗУ 37 БСС 9 отводятся ячейки памяти с 5 по 8, адреса Ак также изменяются от 5 до 8 включительно. Информация в ИКМ-тракте с I входной линией выдается во временных каналах с 5 по 8 включительно. Для преобразвоания побитного уплотнения информации в блочные ячейки ОЗУ 37 работают как последовательно-параллельные регистры сдвиги, для чего информационные выходы ОЗУ 37 1р-7р через регистр 38 замыкаются на информационных входах ОЗУ 37 2р-8р со сдвигом на один разряд, а информация подается на 1р ОЗУ 37. Тогда во время ti информация по I адресу Ак считывается из I ячейки ОЗУ 37, во время t2 при наличии сигнала Тр 1 информация с 1р-7р разрядов ячеек ОЗУ 37 переписывается на 2-8 разряды ячеек ОЗУ, а на 1 разряд записывается информация из ГТИ. За восемь тактов сигналов Тр f ячейки ОЗУ 37 заполняется. Далее адрес I ячейки ОЗУ 37 Ак в ВПК 8 увеличивается на 1, т.е. становится равным (Ак+1). Следующие биты информации из i линии в данном цикле записи записываются уже по адресу Ак (1+1) в (1+1) ячейку ОЗУ 37 и т.д. Таким образом заполняются все k ячеек ОЗУ, отведенные для f входной линии связи в данном цикле записи.

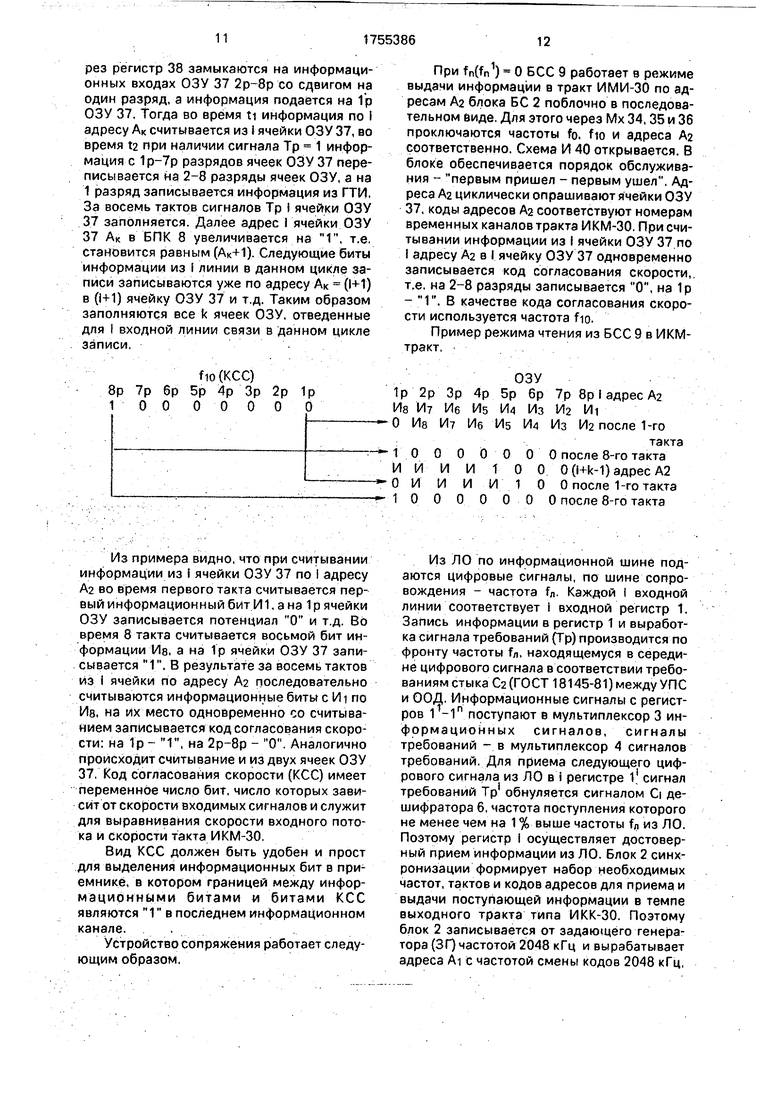

f ю (КОС)

8р 7р 6р 5р Ар Зр 2р 1р 1 00 0000 О

Из примера видно, что при считывании информации из i ячейки ОЗУ 37 по I адресу А2 во время первого такта считывается первый информационный бит И1. а на 1р ячейки ОЗУ записывается потенциал О и т.д. Во время 8 такта считывается восьмой бит информации Ив, а на 1р ячейки ОЗУ 37 записывается 1. В результате за восемь тактов из i ячейки по адресу А2 последовательно считываются информационные биты с HI по Ив, на их место одновременно со считыванием записывается код согласования скорости: на 1р - 1, на 2р-8р - О. Аналогично происходит считывание и из двух ячеек ОЗУ 37, Код согласования скорости (КСС) имеет переменное число бит, число которых зависит от скорости входимых сигналов и служит для выравнивания скорости входного потока и скорости такта ИКМ-30.

Вид КСС должен быть удобен и прост для выделения информационных бит в приемнике, в котором границей между информационными битами и битами КСС являются 1 в последнем информационном канале.

Устройство сопряжения работает следующим образом.

При fn(fn ) О БСС 9 работает в режиме выдачи информации в тракт ИМИ-30 по адресам Аа блока БС 2 поблочно в последовательном виде. Для этого через Мх 34,35 и 36 проключаются частоты fo, fio и адреса А2 соответственно. Схема И 40 открывается. В блоке обеспечивается порядок обслуживания - первым пришел - первым ушел. Адреса А2 циклически опрашивают ячейки ОЗУ 37, коды адресов А2 соответствуют номерам временных каналов тракта ИКМ-30. Присчитывании информации из I ячейки ОЗУ 37 по I адресу А2 в I ячейку ОЗУ 37 одновременно записывается код согласования скорости, т.е. на 2-8 разряды записывается О, на 1р - 1. В качестве кода согласования скорости используется частота fio.

Пример режима чтения из БСС 9 в ИКМ- тракт,

ОЗУ

1р 2р Зр 4р 5р бр 7р 8pi адрес А2 Иа И7 Ие Из И4 Из И2 Mi - 0 Ив Иу Ив Из Из Из И2 после 1-го

такта

-10000000 после 8-го такта И И И И 1 О О О (i+k-1) адрес А2 О И И И И 1 О О после 1-го такта 10000000 после 8-го такта

Из ЛО по информационной шине подаются цифровые сигналы, по шине сопровождения - частота тл. Каждой I входной линии соответствует i входной регистр 1. Запись информации в регистр 1 и выработка сигнала требований (Тр)производится по фронту частоты тл, находящемуся в середине цифрового сигнала в соответствии требованиям стыка С2 (ГОСТ 18145-81) между УПС и ООД. Информационные сигналы с регистров 11-1п поступают в мультиплексор 3 информационных сигналов, сигналы требований - в мультиплексор 4 сигналов требований. Для приема следующего цифрового сигнала из ЛО в i регистре 11 сигнал требований Тр1 обнуляется сигналом Ci дешифратора 6, частота поступления которого не менее чем на 1 % выше частоты fn из ЛО. Поэтому регистр 1 осуществляет достоверный прием информации из ЛО. Блок 2 синхронизации формирует набор необходимых частот, тактов и кодов адресов для приема и выдачи поступающей информации в темпе выходного тракта типа ИКК-30. Поэтому блок 2 записывается от задающего генератора (ЗГ)частотой 2048 кГц и вырабатывает адреса AI с частотой смены кодов 2048 кГц,

поступающих в блок 5 для считывания адресов опроса входных линий, адреса Аа - с частотой смены кодов 256 кГц для считывания информации из блока БСС 9 во временные каналы (ВК) исходящего тракта, частоты и такты fo,fn,fio. Частота fo 2048 кГц используется для привязки асинхронной информации, поступающей из ЛО. к работе устройства. Положительные полупериоды частоты fo используются в качестве тактов ti для считывания информации из ОЗУ устройства, отрицательные полупериоды частоты f о - в качестве тактов t2 для записи информации р ОЗУ устройства Частота переключений fn 4 кГц со скважностью Q 2 используется для переключения блоков БПБ 7, ВПК 8, БСС 9 с режима записи информации из входных линий на режим выдачи информации в исходящий тракт и наоборот, для чего блоки работают в противофазе. Ча- стота fn подается в первые блоки БПБ 71.БПК 81. БСС 91, частота fn - во вторые блоки БПБ 72, БПК 82, БСС 92

Частота f ю 256 кГц, логическое значение которой на 8 разряде временного кана- ла исходящего тракта равно 1, а на разрядах с 1р по 7р - нулю, используется в качестве кода согласования скорости (КСС) при обнулении ОЗУ блока 9 Временная диаграмма работы блока 2 синхронизации изображена на фиг. 11.

Мультиплексоры 3 и 4 осуществляют побитное уплотнение поступающих сигналов по адресам линий (Ал), поступающих из блока 5 памяти линий. В мультиплексоре 4 сиг- налы требований привязываются к заднему фронту частоты fo. Групповые тракты информации (ГТИ) и требований (ПТр) из Мх 3 и Мх 4 поступают в блоки 91 и 92, ГТТр дополнительно поступает в дешифратор 6.

Для обеспечения однократного приема информационных сигналов из входных линий дешифратор 6 по адресам Ал, поступающим из блока 5 памяти линий, и сигналам требований, равным 1, поступающим по ГТТр, вырабатывает сигналы Ci...Cn, подаваемые в соответствующие регистры 11-1п для обнуления сигналов требований. При I коде адреса Ал и i сигнале требований, равном Г, вырабатывается сигнал Ci, равный 1, которым i сигнал требований в J регистре обнуляется.

Частота опроса входных линий определяется частотой выдачи адресов Ал из блока 5 памяти линий, которая для достоверного приема цифровых сигналов должна быть выше не менее чем на 1 % частоты входных сигналов fn. Блок 5 памяти линии осуществляет равномерное распределение опроса каждой входной линии следующим образом. Устройство осуществляет прозрачное поблочное уплотнение из п входных линий связи цифровых сигналов на п выходных каналов тракта Если скорости цифровых сигналов меньше скорости каналов, то каждой линии соответствует одноименный канал в выходном тракте. Если скорость цифрового сигнала превышает скорость канала, то занимается несколько каналов подряд и, соответственно, входы устройства, следующие за занятым входом, не задейст- вуются. Число занятых каналов определяется из условия, что их суммарная скорость должна обеспечивать превышение скорости входного потока на несколько процентов.

Временная диаграмма работы ПЗУ бло ка 5 памяти линий в зависимости от скоро стм цифровых сигналов изображена HJ фиг. 13.

Цикл работы тракта ИКМ-30, равный 8 кГц, содержит восемь (То-Т) циклов опроса адресов AI блока 2 синхронизации. Каждый цикл AI содержит адреса с 0 по 31. При В 48 кбит/с коды адресов AI и Ал совпадают. Если к первой линии подключается ЛО со скоростью передачи В 112 кбит/с, то во время кода адресов AI О и 16 из ПЗУ блока 5 считываются коды адресов Ал соответственно О и О.

При подключении к первой линии ЛО со скоростью передачи до 256 кбит/с по кодам AI О, 8, 16, 24 считываются коды Ал О, О, О, О соответственно. При подключении к первой линии ЛО с В 2032 кбит/с по адресам AI с О по 31 из ПЗУ считываются коды Ал О...б. При таком выборе временных позиций адресов AI обеспечивается равномерный опрос первой линии связи.

Устройство обеспечивает сопряжение с трактом разноскоростных асинхронных цифровых сигналов.

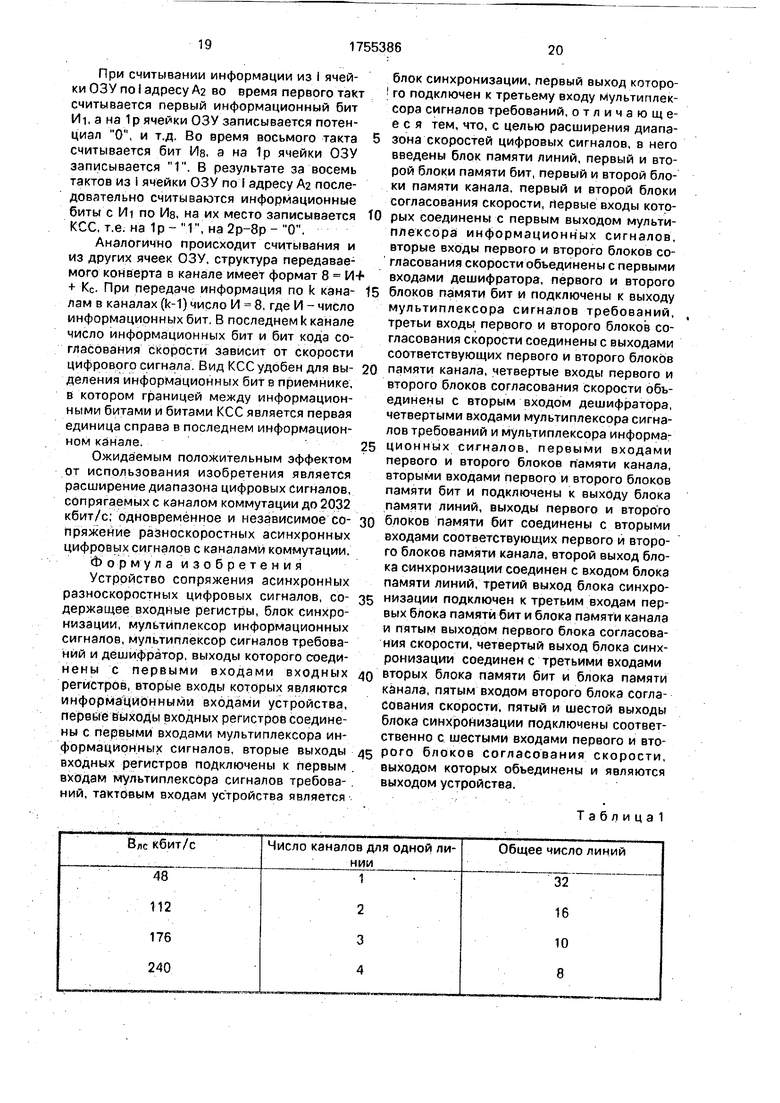

Число обслуживаемых линий для разных скоростей сведено в табл.1.

Примеры числа занятых входов при подключении к устройству разноскоростных линий приведены е табл.2, при этом число каналов в тракте не должно превышать 32 исходя из Ti и Т2, m - число входов устройства.

В соответствии с табл.2 для первой строки одной из возможных распределений входов устройства и каналов сведено в табл.3.

По кодам Ai 0(4...)28 из ПЗУ блока 5 считываются равномерно коды Ал 0, которыми опрашивается первый вход устройства. Частота опроса равна 512 кГц.

По кодам Ai 1(5...)29 из ПЗУ блока 5 считываются равномерно коды Ал 8, которыми опрашивается девятый вход устройства. Частота опроса равна 512 кГц.

Частота опроса входов с 17 по 32 равна 64 кГц.

К первому входу устройства подключается первая линия с В 496 кбит/с, входы с 2 по 8 свободны. В исходящем тракте каналы с О по 7 заняты для передачи ин- формации, поступающей по первой линии.

К девятому входу устройства подключается вторая линия сВ 496 кбит/с, входы с 10 по 16 свободны. В тракте каналы с 8 по 15 заняты для передачи информации, посту- пающей по второй линии.

Шестнадцать линий связи с В 48 кбит/с подключаются соответственно к шестнадцати входам устройства с 17 по 32, соответственно им выделяются каналы в тракте с 16 по 31.

Аналогично происходит выбор входов устройств, распределение времени опроса, составляется таблица прожига ПЗУ для блока 5 памяти линий и для других строк - табл.2.

На ПЗУ блока 5 поступают текущие адреса А2 из блока 2 синхронизации с частотой 2048 кГц и частота fo, равная 2048 кГц. Производится считывание адресов Ал из ПЗУ блока 5 во время такта t2 и фиксация в блоке 5 передним фронтом частоты fo. Адреса Ал поступают в блоки 3, 4, б, 71, 72, 81, 8 , 91, 92.

Блоки 7, 8 и 9 работают в противофазе. Для этого из блока 2 синхронизации на бло- ки 7 , 81, 91 подается частота fn 4 кГц со скважностью импульсов Q -2, на блоки 72, 82, 92 - инверсная частота - fn,

При потенциале fn 1 линейка блоков 7. 8 и 9 работает в режиме накопления инфор- мации из входящих линий при fn 0 линейка блоков работает в режиме выдачи информации в исходящий тракт,

Блоки 7, 8 и 9 содержат ОЗУ, в которых каждой входной линии и каждому каналу в исходящем тракте соответствует ячейки памяти. Номера входных линий и ячеек памяти ОЗУ в блоках 7. 8 и 9 определяются адресами Ал, поступающими из блока 5. Номера каналов в исходящем тракте и номера ячеек ОЗУ в блоках 9 определяются адресами А2, поступающими из блока 2 синхронизации в режиме чтения.

Блоки 7 и 8 управляют записью информации в ОЗУ блока 9. Число разрядов в ячейках ОЗУ блока 9 равно числу разрядов в каналах тракта ИКМ-30, т.е. равно 8. Поэтому блок 7 подсчитывает число принятых бит. При записанном байте из блока 7 в блок

8 выдается сигнал признака байта ПрБ. При значении ПрБ 1 блок 8 вырабатывает адрес следующей ячейки ОЗУ блока 9.

Поэтому ячейки ОЗУ блока 7 имеют по 3 разряда, в которых двоичный код меняется от значения 000 до 111, Ячейки ОЗУ блока 8 имеют по 5 разрядов в соответствии с числом временных каналов исходящего тракта, число которых равно 32.

Начальное значение кода в ОЗУ блока 8 равно коду Ал в ОЗУ блока 5 и соответствует номеру входа устройства.

Далее начальное значение кода в ОЗУ блока 8 может меняться от i значения до значения 1+31.

Блоки 7 и 8 выполнены по схеме группового счетчика, содержащего ОЗУ, регистр Рг и сумматор СМ, у которого считанная информация из t ячейки во время такта ti запоминается в Рг и подается на СМ, где значение кода увеличивается на 1. Во время такта ta при наличии сигналов Тр 1 или ПрБ 1 соответственно новый код переписывается обратно в i ячейку ОЗУ, причем каждому I входу устройства в блоках 7 и 8 соответствует i ячейка ОЗУ. В режиме записи в блоке 7 по сигналу fп 1 к ОЗУ проклю- чается групповой тракт требования ГТТр из блока 4, сигналы которого выполняют роль записи Гз . По I коду адреса Ал блока 5 во время ti из i ячейки ОЗУ считывается текущий код бит. Во время t2 при сигнале Тр 1 увеличенный на 1 код бит переписывается в i ячейку ОЗУ. При коде 111 подается в блок 8 сигнал ПрБ 1 при наличии сигнала Тр 1. В этой же временной позиции во время такта t2 и в 1 ячейку ОЗУ записывается код 000. При сигнале Тр 0 выдается сигнал ПрБ 0 и в i ячейке ОЗУ остается прежний код, т.е. групповой счетчик считает число сигналов требований Тр 1.

Аналогично в режиме записи в блоке 8 по сигналу fп 1 проключаются простроби- рованные частотой fo сигналы ПрБ из блока 7, выполняющие роль тактов записи Гз . По i коду Ал блока 5 по время такта ti из i ячейки ОЗУ считывается текущий адрес канала Ак. Во время t2 при сигнале ПрБ 1 код (А + 1) переписывается в I ячейку ОЗУ. Адреса каналов Ак поступают в блок 9 согласования скорости, В режиме записи в блоке 9 согласования скорости производится согласование скорости входного потока со скоростью исходящего тракта и преобразование информации из побитного вида в блочный. В зависимости от скорости входного потока в ОЗУ отводится для накопления информации k ячеек подряд, причем номера входной линии первой ячейки ОЗУ и первого канала

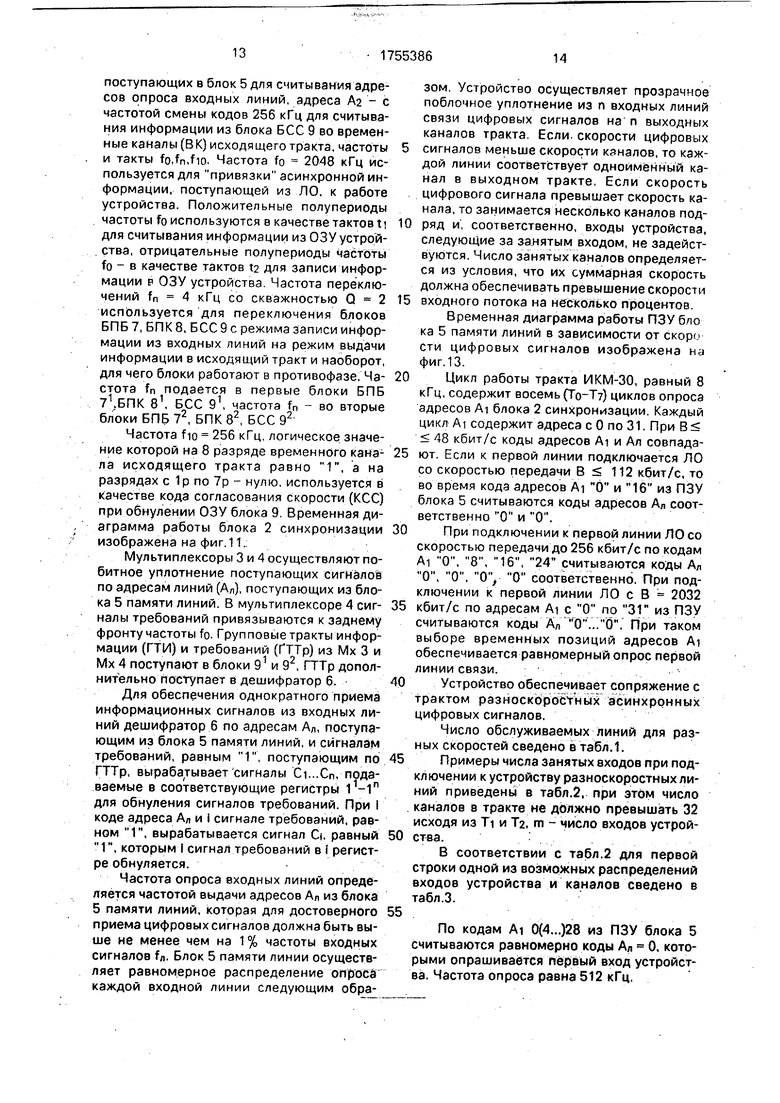

исходящего тракта совпадают. После записи восьми бит информации в I ячейку ОЗУ по I адресу Ак блока 81 адрес Ак увеличивается на 1, т.е. (Ак + 1), последующие восемь бит записываются в (i+1) ячейку ОЗУ и т.д. На- пример, для цифровых сигналов, подключенных к I входу устройства, отводится k каналов сопряжения в тракте ИКМ-30, тогда входы, начиная с (i+1) no (i-t-k-1). оставляют свободными, соответственно с этим в ОЗУ блока 9 и исходящем тракте занимаются ячейки памяти и каналы с I no (l+k-1) включительно. Для преобразования побитного уплотнения информации в блочные ячейки ОЗУ работают как последовательно-парал- лельные регистры сдвига, для чего информационные выходы ОЗУ (1-7) через регистр блока замыкаются на информационные входы ОЗУ (2-8) со сдвигом на один разряд вправо, а информация из блока 3 подается на первый информационный вход ОЗУ. При записи информации потенциалом fn 1 про- ключаются ГТТр из блока 4, сигналы которого являются тактами записи тз , ГТИ - из блока 3, адреса Ак - из блока 8. Схема И на выходе блока 9 устанавливается в высоко- импендансное состояние Z. Тогда во время ti информация по i адресу Ак считывается из I ячейки ОЗУ, во время ta при сигнале Тр 1 информация с 1-7 разрядов переписывает- ся на 2-8 разряды ячеек ОЗУ, и на первый разряд записывается информация из ГТИ. За восемь сигналов Тр 1 i ячейка ОЗУ заполняется. Адрес Ак в блоке 8 увеличивается на 1. Следующие информационные биты записываются в (1+1) ячейку ОЗУ блока 9 и т.д. Таким образом заполняются k ячеек ОЗУ блока 9, отведенных для цифрового сигf ю (КСС)

8р 7р 6р 5р 4р Зр 2р 1р

10 00 0000

нала, передаваемого по линии, подключенной к I входу устройства.

При fn - 0 блоки 7, 8 и 9 работают в режиме считывания.В этом режиме в блоке

7проключается частота fo, выполняющая роль гз , к информационным входам ОЗУ проключается код 000. Обнуление ячеек ОЗУ происходит по адресам Ал блока 5 во время такта t2. В ОЗУ блока 8 восстанавливаются исходные адреса Ал в ячейках, определяемых адресами Ал. Для этого проключается частота fo, выполняющая роль Гз , к информационным входам ОЗУ проключаются адреса Ал. В такты t2 в ячейки ОЗУ, определяемые адресами Ал, записывз ются эти же адреса. Из блока 9 согласован я скорости выдается информация в исходч щий тракт в последовательном виде и одновременно в ячейки ОЗУ записывается код согласования скорости КСС. Для этого проключаются частота fo, выполняющая роль гз , частота fio из блока 2, выполняющая роль КСС, адреса А2 из блока 2, схема И в блоке 9 открыта задержанной на триггере блока на полпериода частотой f$ частоты fn.

8блоке обеспечивается порядок обслуживания - первым пришел - первым ущел. Адреса А2 циклически оправшивают ОЗУ, коды адресов Аа соответствуют номерам ВК-тракта и ячейкам ОЗУ. При считывании информации из I ячейки ОЗУ по I адресу А2 в i ячейку ОЗУ одновременно записывается код согласования скорости. Таким образом, на 2-6 разряды ОЗУ записывается О, на 1р - 1.

Пример режима чтения из блока согласования скорости в исходящий тракт.

ОЗУ

1р 2р Зр 4р 5р 6р 7р 8р Из И Иб Из И4 Из И2 Hi i адрес Аа

Ив И Иб Ив И4 Из И2 после

1-го такта

- 10000000 ИКССН

после 8-го (i+ k-1)

И И И И 1 О О О I- КСС-1

КССадрес А2

- ОИИИИ 00после

1-го такта

00000 00после

V КССН8-го такта

При считывании информации из I ячейки ОЗУ по I адресу Аа во время первого так считывается первый информационный бит HI. а на 1р ячейки ОЗУ записывается потенциал О, и т.д. Во время восьмого такта считывается бит Ив, а на 1р ячейки ОЗУ записывается Г. В результате за восемь тактов из i ячейки ОЗУ по i адресу А2 последовательно считываются информационные биты с Mi no Us, на их место записывается КСС, т.е. на 1р - 1, на 2р-8р - О.

Аналогично происходит считывания и из других ячеек ОЗУ, структура передаваемого конверта в канале имеет формат 8 И + Кс. При передаче информация по k кана- лам в каналах (k-1) число И 8, где И - число информационных бит. В последнем k канале число информационных бит и бит кода согласования скорости зависит от скорости цифрового сигнала. Вид КСС удобен для вы- деления информационных бит в приемнике, в котором границей между информационными битами и битами КСС является первая единица справа в последнем информационном канале.

Ожидаемым положительным эффектом от использования изобретения является расширение диапазона цифровых сигналов, сопрягаемых с каналом коммутации до 2032 кбит/с; одновременное и независимое со- пряжение разноскоростных асинхронных цифровых сигналов с каналами коммутации.

Формула изобретения

Устройство сопряжения асинхронных разноскоростных цифровых сигналов, со- держащее входные регистры, блок синхронизации, мультиплексор информационных сигналов, мультиплексор сигналов требований и дешифратор, выходы которого соединены с первыми входами входных регистров, вторые входы которых являются информационными входами устройства, первые выходы входных регистров соединены с первыми входами мультиплексора информационных сигналов, вторые выходы входных регистров подключены к первым входам мультиплексора сигналов требований, тактовым входам устройства является

блок синхронизации, первый выход которого подключен к третьему входу мультиплексора сигналов требований, отличающееся тем, что, с целью расширения диапазона скоростей цифровых сигналов, в него введены блок памяти линий, первый и второй блоки памяти бит, первый и второй блоки памяти канала, первый и второй блоки согласования скорости, первые входы которых соединены с первым выходом мультиплексора информационных сигналов, вторые входы первого и второго блоков согласования скорости объединены с первыми входами дешифратора, первого и второго блоков памяти бит и подключены к выходу мультиплексора сигналов требований, третьи входы первого и второго блоков согласования скорости соединены с выходами соответствующих первого и второго блоков памяти канала, четвертые входы первого и второго блоков согласования скорости объединены с вторым входом дешифратора, четвертыми входами мультиплексора сигналов требований и мультиплексора информа- ционных сигналов, первыми входами первого и второго блоков памяти канала, вторыми входами первого и второго блоков памяти бит и подключены к выходу блока памяти линий, выходы первого и второго блоков памяти бит соединены с вторыми входами соответствующих первого и второго блоков памяти канала, второй выход блока синхронизации соединен с входом блока памяти линий, третий выход блока синхронизации подключен к третьим входам первых блока памяти бит и блока памяти канала и пятым выходом первого блока согласования скорости, четвертый выход блока синхронизации соединен с третьими входами вторых блока памяти бит и блока памяти канала, пятым входом второго блока согласования скорости, пятый и шестой выходы блока синхронизации подключены соответственно с шестыми входами первого и второго блоков согласования скорости, выходом которых объединены и являются выходом устройства.

Т а б л и ц а 1

Продолжение табл 1

Т а б л и ц р 5

ТаблицаЗ

Физ.1

ш

/ft ЛИ Ннф.1}

ИЗ ЛО Fjti //J DC Ci

МхСТр в БПЛ В 5П61,

5/162, Бпкг,Бссг

БСС1

дбссг

Фиг. 2.

Фиг,3

(О

со со in ю

Г-35

«

5

5 5 3

Л|

fo ti- Jl

T

T

/5T

ЩЯЛТ1Г1Г1Штя т

ШЛ/2

J

L.

1L

tilKty Af 256 кГц

т к Гц

ЪЦ КГц

/5-U

/7-L. AT. ЛТ.

зг кГц

Аг

16 КГц

8 кГц

+

--. j fjxlfKfy

0|Q{gi((, (,

// J/ /7 5/7 7/7 8р 1р 2р Зр ty 5p 6р 1р 8р ( о ВКЗ1г Г 8к

1

Г /17 X ВЛА Ал )С ШГ /UX

////9. / Ji

77//7////////////////V///////77/У7/77//////7/77/77777 (

Sr

Pri ИI

чI

/Vi i :

Л

L

K/////s/////y// /

уТ-т::

I УГ V/7 I

8нГц

L.

1L

tilKty Af 256 кГц

т к Гц

ЪЦ КГц

зг кГц

Аг

16 КГц

8 кГц

1

/г/7

}

ЛО

Л

L

г/г/

Фие.13

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

Авторы

Даты

1992-08-15—Публикация

1990-11-05—Подача