устройства, соответствующие выходы которого соединены с выходами блока управления, а иервая и вторая группы входов блока нередачи соединены с соответствующими входами-выходами устройства 2.

Недостатком устройства является низкая производительность, обусловленная наличием двух донолннтельных разрядов, служащих признаком информации в каждом нередаваемом между ЭВМ словом. Кроме того, ирнем настроечной информации из настраивающей ЭВМ в устройство соиряження настраиваемой ЭВМ возможен только нри наличии управляющего сигнала из иастраиваемой ЭВМ.

Целью изобретения является иовыщение быстродействия устройства для сопряжеиия однородной вычислительиой системы.

Поставленная цель достигается тем, что в устройство, содержащее блок коммутации, блок настройки, включающий дещифратор кода настройки, регистр кода настройки и первый элемеит ИЛИ, регистр синхронизации и блок иередачи, включающий регистр обмена, причем первый и второй уиравляющие входы-выходы блока коммутации являются соответственно первым и вторым управляющими входами-выходами устройства, иервый и второй информационные входы-выходы блока коммутации являются соответственно первым и вторым ииформациоиными входами-выходами устройства, третий ииформациоиный вход-выход блока коммутации соединен с первым информационным входом регистра кода настройки, первым входом регистра синхроиизации, ииформациоииьш входом-выходом регистра обмена и являетея третьим информационным входом-выходом устройства, выход регистра синхроиизации соединен со входом синхронизации блока коммутации, ииформациоииьш выход которого соединен с информационным входом регистра обмена и с вторым ииформационным входом регистра кода настройки, выход которого соединен с входом дещифратора, выход которого соедииеи с управляющим входом иастройки блока коммутации, уиравляющий выход которого соедииен с нервым входом элемента ИЛИ, выход которого соединен с управляющим входом регистра кода настройки, введены блок прерывания, дешифратор адреса регистра, регистр обобщенного безусловного иерехода, регистр состояиия, второй элемент ИЛИ, в блок передачи введеи элемент ИЛР1. Управляющий выход блока коммутации соединен с первым входом второго элемента ИЛИ, иервым входом элемента ИЛИ блока иередачи, первым управляющим входом регистра состояиия, входом блока прерывиия, вход-выход которого соединен с ииформациоиным входомвыходом регистра состояиия, информационным входом-выходом регистра обобщенного безусловного перехода, входом дещифратора адреса регистра и соединен с третьим ииформациоиным входом-выходом блока коммутации, вход системных сигналов которого соедииеи с первым выходом дешифратора адреса регистра, второй, третий и четвертый выходы которого соедииеиы соответственно со вторыми входами первого, второго элементов ИЛИ и элемента ИЛИ блока иередачи. Пятый выход дешифратора адреса регистра соединен с входом регистра синхронизации. Выходы первого, второго элемеитов ИЛИ и элементов ИЛИ блока передачи соединеиы соответственно с вторым, третьим и четвертым управляющими входами регистра состояния. Ииформациоииьш вход регистра обобщенного безусловного иерехода соедииен с информационным входом регистра обмена. Выходы второго элемеита ИЛИ и элемента ИЛИ блока передачи соединены соответственно с управляющим входом регистра.обмеиа и управляющим входом регистра обобщенного безусловиого перехода.

Блок прерывания может быть реализоваи аналогично блоку прерываиия известного устройства.

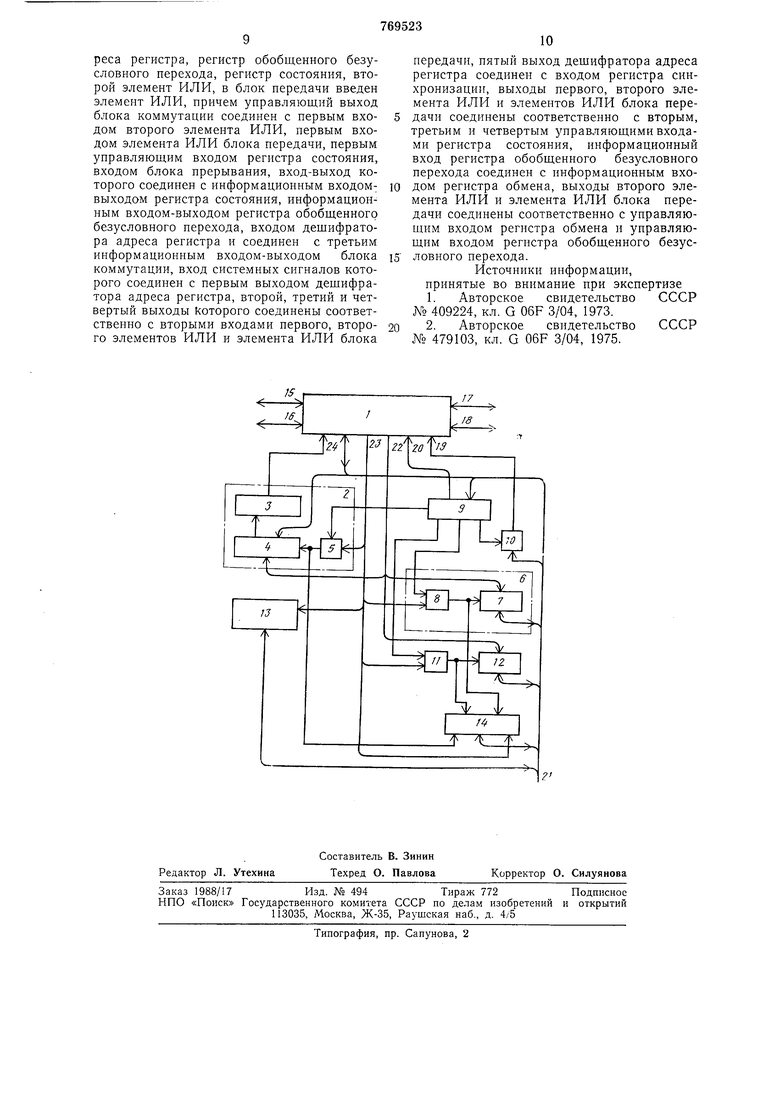

Структуриая схема устройства для сопряжения одиородной вычислительной системы показана на чертеже.

Устройство для сопряжения однородной вычислительиой системы содержит блок 1 коммутации, блок 2 настройки, состоящий из дещифратора 3 кода иастройки, регистра 4 кода настройки и иервого элемента ИЛИ 5, блок иередачи 6, состоящий из регистра обмеиа и второго элемента ИЛИ 8, дешифратор 9 адреса регистра, регистр 10 синхронизации, третий элемеит ИЛИ 11, регистр 12 обобщенного безусловного перехода, блок 13 ирерывания, регистр 14 состоянием, первый уиравляющий вход-выход (щии)) 15 устройства, иервый информационный вход-выход (щину) 16 устройства, второй уиравляющий вход-выход (шину) 17 устройства, второй ииформациоиный вход-выход (щину) 18 устройства, вход синхронизации (шипу) 19 блока коммутации, вход системиых сигналов (щину) 20 блока коммутации, третий ииформациоииьш вход-выход (шииу) 21 устройства, информационный выход (щину) 22 блока коммутации, унравляющий выход (щииу) 23 блока коммутаций и управляющий вход иастройки (щину) 24 блока коммутации.

В вычислительной системе, построенной с использованием устройства для сопряжения, вьшолияется следующий иабор системных операций: настройка, обмен, обобщенный безусловный переход и обобщенный условный иереход.

Устройство для соиряжения одиородной вычислительиой системы работает следующим образом.

Рассмотрим выполнение системных операций.

Операция настройки. Операция настройки позволяет выделить (.V машин) подсистему для решения задачи, настроить граничные микро-ЭВМ подсистемы ia приемпередачу информации только внутри подсистемы, настроить каждую промежуточную микро-ЭВМ на прием и трансляцию принятой информации или передачу из любой микро-ЭВМ подсистемы.

Настройка осуществляется из какой-либо одной микро-ЭВМ. Онерация настройки заключается в заиесении необходимой информации в регистры 4 устройств для сопряжения.

Наетраиваюшая микро-ЭВМ начинает процесс настройки подсистемы с занесения информации в регистр 4 своего устройства для соиряжения. Из микро-ЭВМ по шнне 21 в дешифратор 9 иоетуиает адрес регистра 4, и на втором выходе дегнифратора 9 появляется сигнал, который через элемент ИЛИ 5 ноступит на управляюш,ий вход регистра 4, разрешая запиеь слова настройки по первому информационному входу регистра 4 с шины 21. В процессе самонастройкн сигналы на шинах 15, 17 и 16, 18 не появляются.

На втором шаге настранваюнитя микроЭВМ выбирает из своей оперативной иамяти настроечное слово для второго устройства для сопряжения и пересылает его по адресу регистра 4 по шине 21, но на этот раз слово не заносится в регистр 4 устройства для сопряжения настраиваюш,ей микро-ЭВМ, а поступает по шине 21 в блок 1 коммутации. Дешифратор 9 при этом вырабатывает по шине 20 сигнал системной настройки (Спастр.), который поступает в блок 1 коммутации,

Направление передачи определяется кодом, записанным в регистр 4, который поступает в дешифратор 3, с выхода которого по шинам 24 в блок 1 коммутации поступают управляющие сигналы. Настроечное слово проходит по шинам 16 или 18, а сигнал настройки Снастр. - по шииам 15 или 17 на соответствующие входы второго устройства сопряжения.

Во втором устройстве для сопряжения настроечное слово из блока 1 коммутации поступает на второй информациоиный вход регистра 4 по шине 22, а управляющий сигнал Снастр поступает из блока 1 коммутации по щине 23 через элемент ИЛИ 5 на управляющий вход регистра 4, разрешая запись настроечного слова в регистр. Одновременно с этим сигнал Сцастр с выхода элемента ИЛИ 5 поступит на вход регистра 14, устанавливая соответствующий разряд в «единицу,

На третьем щаге настраивающая микроЭВМ выдает по шине 21 слово настройки, которое, пройдя через первое и второе устройства для сопряжения, заносится в регистр 4 третьего устройства для сопряжения.

После того как устройство для сопряжения получило настроечное слово, связанная с ним микро-ЭВМ переходит на режим работы по прерыванию. Это осуществляется следуюищм образом. Сигнал Спастр по шине 23 иоступит на вход блока 13 прерывания, подготавливая его к работе. По окончаиии сигнала Снастр с выхода блока 13 по щине 21 поступит снгиал запроса прерывания и, если микро-ЭВМ ответит по шине 21 сигналом готовности, то из блока 13 считывается соответствующий адрес команды

прерывания, который по щине 21 поступит в микро-ЭВМ.

Обобщенный условный переход (ОУП). Процесс настройки происходит асинхронно, т. е. как только устройство для сопряжения

получит код иастройки, то связаиная с ним микро-ЭВМ сразу же переходит к подпрограмме системных операций. Для синхронизации всех микро-ЭВМ подсистемы сразу же после операции настройки выполняется

снстемная операция ОУП, после выполнения которой все микро-ЭВМ подсистемы одовременно переходят к выполнению параллельной программы. Операция ОУП выполняется следуюи1им

образом. Микро-ЭВМ, заверщившая .свою работу но программе (подпрограмме) параллельной ветви, устанавливает регистр 10 но шиие 21 при разрешении с пятого выхода дешифратора 9 в едииичное состояние.

С выхода регистра 10 по шине 19 сигнал системной синхронизации поступит в блок 1 коммутации. В тот момент, когда все регистры .10 устройств для сопряжения подсистемы установлены в единичное состояние, в блоках 1 коммутации выработается сигнал обобщенного условия, который поступит с выхода блока коммутации и по шине 23 занесется в соответствующий разряд регистра 14. Одновременно с этим этот

сигнал поступит в блок 13 прерывания, с выхода которого по щине 21 в микро-ЭВМ поступит запрос на прерывание, и если микро-ЭВМ ответит по шине 21 сигналом готовности, то из блока 13 считывается соответствующий вектор прерывания, который по щине 21 поступнт в микро-ЭВМ. С выхода регистра 14 текущее слово состояния устройства по щине 21 в микроЭВМ, и после этого микро-ЭВМ перейдет

к следующему этапу параллельных вычислений.

Обычно операцня ОУП выполняется перед операцией обмена, синхронизируя все микро-ЭВМ подсистемы.

Обмен. Системная операция обмена наиболее часто выполняется при параллельной работе всех микро-ЭВМ. При этом осуществляется трансляционный режим обмена, т. е. одна микро-ЭВМ передает, а остальные принимают. Микро-ЭВМ, в программе

которой предусмотрено выполнение этой операции, посылает по шинам 21 в дешифратор 9 адрес регистра 7. При этом по шине 20 в блок 1 коммутации поступит сигнал системного обмена (Собм.). Прц считывании информационного слова нз оперативной памяти микро-ЭВМ оно по шине 21 поступит на вход блока I коммутации и с его выходов по шинам 18, 16 совместно с сигналом Собм., который поступает на шины 15, 17, поступит на входы-выходы принимающих устройств для сопряжения. В принимающих устройствах сигнал Собм. поступит с шин 15, 17 через блок 1 коммутации по шине 23 на вход элемента ИЛИ 8, разрешая запись в регистр 7 информационного слова, которое поступает на него по шине 22 через блок 1 коммутации с шин 16, 18. Одновременно с этим сигнал Собм. по шине 23 поступит в соответствующий разряд регистра 14 и в блок 13 прерывания, с выхода которого по шине 21 в микро-ЭВМ поступит сигнал запроса прерывания. При этом все микроЭВМ подсистемы переходят по прерыванию на обслуживание устройства для сопряжения. Из регистра 14 считывается информация по шине 21 Б микро-ЭВМ, которая анализирует разряды регистра 14, и определив, что выполняется оиерация обмена, считывает по шиие 21 из регистра 7 информациопное слово в регистр иазначения микро-ЭВМ.

После выполиепия операции обмена все микро-ЭВМ выполняют операцию ОУП и все микро-ЭВМ подсистемы переходят к следующему этапу параллельной работы.

Обобшениый безусловный переход. Операция обобщенного безусловного перехода выполняется после команды ОУП, т. е. все микро-ЭВМ переходят к следующему этапу параллельных вычислений. Унравление дальнейшим ходом параллельпых вычислений берет на себя одна из микро-ЭВМ подсистемы. При этом по шине 21 в дешифратор 9 поступает адрес регистра 12 и на первом и четвертом выходах дешифратора 9 появится сигнал системного обобщенного безусловного перехода (Со.бу.п.)- С четвертого выхода Со.бу.п. поступит через элемент ИЛИ 11 на управляющий вход регистра 12 и в соответствующий разряд регистра 14. С первого выхода дешифратора 9 сигнал Со.бу.п. по шине 20 поступит в блок 1 коммутации. По шине 21 ииформационное слово записывается в регистр 12, а также через блок 1 коммутации на шины 16, 18 устройства. В принимающих устройствах для сопряжения сигнал Со.бу.п. поступит с шин 15, 17 через блок 1 коммутации по шине 23 в блок 13 прерывания, с выхода которого по шине 21 в микро-ЭВМ поступит сигнал запроса прерывания. Кроме того, по щине 23 сигнал Со.бу.п. поступит в соответствующий разряд регистра 14 и на чход элемента ИЛИ 11, разрешая запись в

регистр 12 информационного слова ио шине 22 через блок 1 комутации с шин 16, 18.

Все микро-ЭВМ подсистемы переходят по прерыванию на обслуживание устройства для сопряжения. Из регистра 14 считывается информация по шине 21 в микро-ЭВМ, которая анализирует разряды регистра 14, определяет, что выполняется операция обобщенного безусловного нерехода и по щине 21 из регистра 12 в микро-ЭВМ считывается информационное слово, которое воснринимается как адрес, либо как команда. И все микро-ЭВМ переходят на новую ветвь параллельных вычнслений.

Однородная вычислительная система, построенная с использованием предложенного устройства для сопряжения, предназначена для решения сложных сильносвязанных задач по параллельным алгоритмам. Производительность однородной вычислительной системы зависит от скорости выполнения системиых операций.

Введение дополнительных блоков и связей позволяет повысить производительность вычислительной системы за счет уменьшения времени выполнения системиых операций.

Формула изобретения

Устройство для соиряжения однородной вычислительной системы, содержащее блок ко.ммутацин, блок настройки, включающий дешифратор кода настройки, регистр кода настройки и первый элемент ИЛИ, регистр синхронизации, и блок передачи, включающий регистр обмена, причем первый и второй управляющие входы-выходы блока коммутации являются, соответственно, первым и вторым управляющими входами-выходами устройства, первый и второй информационные входы-выходы блока коммутации являются соответственно первым и вторым информационными входами-выходами устройства, третий информационный входвыход блока коммутации соединен с первым информационным входом регистра кола настройки, первым входом регистра синхронизации, информационным входом-выходом регистра обмена и является третьим информационным входом-выходом устройства, выход регистра CHHXJ, оннзации соединен со входом синхронизации блока коммутации, информационный выход которого соединен с информационным .входом регистра обмена и с вторым информационным входом регистра кода настройки, выход которого соединен с входом дешифратора, выход которого соединен с управ.пяющим входом настройки блока коммутации, управляющий выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с управляющим входом ре.гистро кода настройки, отличающееся тем, что, с целью повышения быстродействия, в него введены блок прерывания, дешифратор ад9

реса регистра, регистр обобщеиного безусловного перехода, регистр состояния, второй элемент ИЛИ, в блок иередачи введен элемент ИЛИ, причем уиравляющий выход блока коммутации соединен с иервым входом второго элемента ИЛИ, первым входом элемента ИЛИ блока передачи, первым управляющим входом регистра состояния, входом блока прерывания, вход-выход которого соединен с информационным входомвыходом регистра состояния, информационным входом-выходом регистра обобщенного безусловного перехода, входом дешифратора адреса регистра и соединен с третьим информационным входом-выходом блока коммутации, вход системных сигналов которого соединен с иервым выходом дешифратора адреса регистра, второй, третий и четвертый выходы kOTOporo соединены соответственно с вторыми входами первого, второго элементов ИЛИ и элемента ИЛИ блока

10

передачи, пятый выход дешифратора адреса регистра соединеи с входом регистра синхронизации, выходы первого, второго элемента ИЛИ и элементов ИЛИ блока передачи соединены соответственно с вторым, третьим и четвертым управляющими входами регистра состояния, информациоиный вход регистра обобщенного безусловного перехода соединен с информационным входом регистра обмена, выходы второго элемента ИЛИ и элемента ИЛИ блока передачи соединены соответственно с управляющим входом регистра обмена и управляющим входом регистра обобщенного безусловного перехода.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 409224, кл. G 06F 3/04, 1973.

2. Авторское свидетельство СССР № 479103, кл. G 06F 3/04, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU885989A1 |

| Устройство сопряжения для однороднойВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU851387A1 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU951287A2 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1986 |

|

SU1365090A2 |

| Устройство сопряжения для однородной вычислительной системы | 1981 |

|

SU1068928A1 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Устройство для сопряжения однородной вычислительной системы | 1983 |

|

SU1117625A1 |

Авторы

Даты

1980-10-07—Публикация

1978-12-05—Подача