1

Изобретение относится к вычислительной технике и предназначено для сопряжения элементарных масюн в однородную вычислительную систему или структуру.

Известны устройства для сопряжения распределительных вычислительных систем, содержащие блок коммутации, блок управления, блок передачи и блок настройки 1.

Недостаток известного устройства состоит в низком быстродействии,Обусловленном необходимостью перезаписи настроечной информации из блока передачи в блок настройки всякий раз, когда связанная с ним микро-ЭВМ принимает участие в обмене.

Наиболее близким к предлагаемому по сущности технического решения является устройство для сопряжения однородной вычислительной системы, содержащее блок коммутации, блок настройки, состоящий из регистра кода настройки, дешифратора кода настройки и первого элемента ИЛИ, блок передачи, состоящий из регистра обмена и второго элемента ИДИ, даиифратор адреса регистра, регистр синхронизации/ третий элемент ИЛИ, регистр обобщенного безусловного перехода, блок прерывания, регистр состояния, первый управляющий вход выход (шина) устройства, первый информационный вход-выход (шина) устройства, второй управляющий вход-выход (шина) устройства, второй информационный вход-выход (шина) устройства, вход синхронизации (шина) блока коммутации, вход системных

10 сигналов.(шина) блока коммутации, третий информационный вход-выход (шина) устройства информационный выход ,шина) блока кoммyтaцйи управляющий выход (шина) блока коммутации, уп15равляющий вход настройки (шина) блока KOMMyTatXHH. Первые и вторяле информационные и управляющие входы-выходы устройства и третий информационный вход-выход устройства соедине20ны соответственно с , вторыми, .третьими, четвертыми и пятыми входами-выходами блока коммутации, причем третий информационный вход-выход устройства соединен также с первым

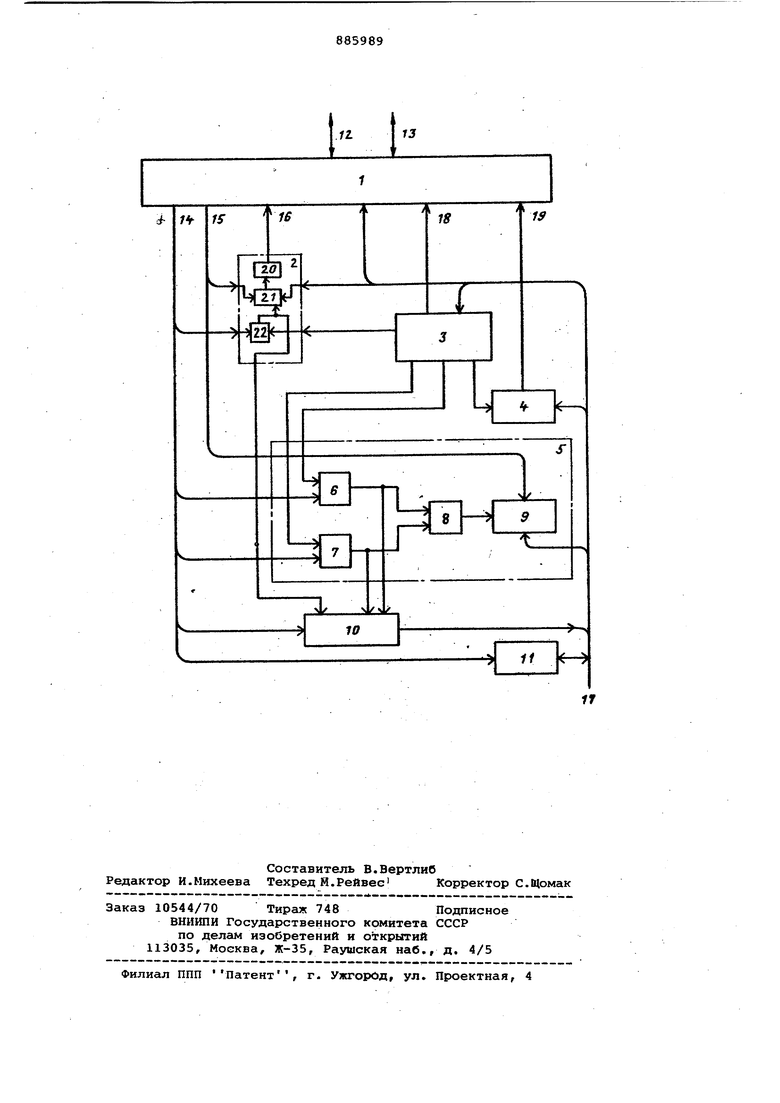

25 входом регистра кода настройки, входом дешифратора адреса регистра, вхоцом-выходом регистра обмена, входомвыходом регистра состояния, входом-выходом блока прерывания, входом30выходом регистра обобщенного безусловного перехода и вторым входом регистра синхронизации, информационный выход блока коммутации соединен с первым входом регистра обмена, вторы информационным входом регистра обобценного безусловного перехода вторым входом регистра кода настройки, упра шлющий выход блока коммутации соединен со вторыми входами первого, второго и третьего элемента ИЛИ, с первым входом регистра состояния и входом блока прерывания , управляющий вход настройки блока коммутации соединен с выходом дешифратора кода настройки, вход которого соединен с выходом регистра кода настройки, вход системных сигналов блока коммутации соединен с пятым выходом дешифратора адреса регистра, первый, второй, третий и четвертый выходы которого соединены соответственно с первыми входамипервого, второго и третьего элементов ИЛИ и регистра синхронизации, выходы первого, второго и третьего элементов ИЛИ соединены соответственно с управляющими входами регистра кода настройки, регистра обмена и регистра обобщенного безусловного перехода а также с первым и третьим входами регистра состояния. При решении задачи на однородной вычислительной системе (ОВС) выполняется слеДукжщй набор системных операций: настройка, обмен, обобщенный условный переход, обоб1аенный безусловный переход, причем эти операции не могут выполняться одновременно 2. Недрстатком данного устройства является большой объем оборудования, обусловленный .наличием двух регистров: регистра обмена и регистра обобщенного перехода, которые работают последовательно и выполняют аналогичные функции. Цель изобретения - сокращение объема оборудования. Поставленная цель достигается тем что в усггройство, содержащее блок коммутации, первый и второй информационные и управляющий входы-выходы являются соответственно первым и вто рым информационным и управляющим входами-выходами устройства, блок настройки, дешифратор адреса регистра, первым выходом соединенный с пер 1ВЫМ управляющим входом блока коммута Ции, регистр системной синхронизации блок взаимодействий, включанвдий первы1г и второй элементы ИЛИ и регистр взаимодействия, регистр состояния и блок прерывания, причем управляющий выход блока коммутации соединен с перВЕЛМи входами блока настройки, первого и второго элементов ИЛИ, регистра состояния и входом блока прерывания, вход-выход которого соеди,нен с выходом регистра состояния, с выходом регистра взаимодействия, пер вым входом регистра системой синхронизации, входом дешифратора адреса регистра, вторым входом блока настройки и вторым информационным входомвыходом блока коммутации, информационный выход которого соединен с информационным входом регистра взаимодействия и третьим входом блока настройки, четвертый вход которого соединен с первым выходом дешифратора адреса регистра, второй, третий, четвертый ипятый выходы которого соединены соответственно со вторыми входами первого элемента ИЛИ, второго элемента ИЛИ, регистра системной синхронизации и вторым управЛяквдим входом блока коммутации, третий управляющий вход которого соединен с выходом регистра системной синхронизации, второй выход блока настройки соединен со вторым входом регистра состояния,третий и четвертый входы которого соединены соответственно с выходами первого и второго элементов ИЛИ, введен третий элемент ИЛИ, причем первый вход третьего элемента ИЛИ соединен с выходом первого элемента ИЛИ, второй вход - с выхо- . дом второго элемента ИЛИ, а выход с управляющим входом регистра взаимодействия . Блок-схема устройства для сопряжения показана на чертеже. Устройство для сопряжения содержит блок 1 коммутации, блок 2 настройки, дешифратор 3 адреса регистра, регистр 4 системной синхронизации, блок 5 взаимодействий, включающий первый, второй, третий элементы ИЛИ 6,7 и 8 и регистр 9 взаимодействия, регистр 10 состояния и блок 11 прерывания, информационный вход-выход (шина) 12 устройства, управляющий вход-выход (шина) 13, управлякяций выход (шина) 14 блока коммутации, информации выход (шина) 15 блока коммутации, первый управляющий вход 16 (настройки) блока коммутации, второй информационный вход-выхоя (ши- на) 17 устройства, второй управляющий вход (шина) 18 (системных сигналов) блока коммутации, третий вход (шина) 19 (синхронизации) блока коммутации., Блок 2 настройки содержит дешиЛратор 20 кода настройки, регистр 21 -кода настройки и ИЛИ 22. Устройство работает следующим образом. В системе или структуре, построенной с использованием предлагаемого устройства, вьтолняются настройка, обмен, обобщенный условный переход и обобщенный безусловный переход. Операция настройки. Реализация взаимодействия между микро-ЭВМ, входящими в состав однородной вглчислительной системы (ОВС) или

структуры, происходит через настроенные устройства, связанные с данными микро-ЭВМ. Для настройки устройства необходимо занести настроечную информацию в регистр 21 блока 2 настройки, с выхода которого на управляющий вход 16 блока 1 поступает информация разрешающая прохождение управляющих и информационных данных с шин 12 и

13через блок 1 коммутации на шины

14и 15 блока коммутации или с шин 17,18 и 19 через блок 1 коммутации

на информационные и управляющие шины 12 устройства.

Настроечная информация в блок 2 может поступить или из микро-ЭВМ, связанной с данным устройством по ши 17, при разрешении с первого выхода дешифратора 3, или из другой микроЭВМ по шине 12 при разрешении по управлякядей шине 13 через блок 1 по шинам 15 и 14 соответственно.

Операция обмена.

После настройки всех устройств дл сопряжения связанные с ними микроЭВМ, образующие подсистег- переходя к выполнению параллельной программы.

В процессе выполнения подсистемой ОВС параллельной программы микро-ЭВМ обмениваются мелсду собой информацией. При этом осуществляется трансляционный режим обмена, т.е. одна микро-ЭВМ передает, а остальные принимают. Микро-ЭВМ, в программе которой предусмотрено выполнение этой операции, посылает по шине 17 в дешифратор 3 код, соотве тствую1аий операции обмена, при этом по шине 18 в-блок 1 поступает сигнал системного обмена. При считывании информационного слова из оперативной памяти микро-ЭВМ оно по шине 17 поступает на вход блока 1 коммутации и с его выходов по шине 12 совместно с сигналом системного обмена на шине 13 - на входывыходы принимающих устройств для сопряжения. В принимающих устройства сигнал системного обмена поступает с шины 13 через блок 1 коммутации по шине 14 на вход первого элемента ИЛИ 6 и через третий элемент ИЛИ 8 ,- на вход регистра 9 взаимодействия, разрешая запись в него информационного слова обмена, которое поступает на него по шине 15 через блок 1 с шины 12.

Одновременно с этим сигнал системного обмена с выхода элемента ИЛИ 8 поступает в соответствующий разряд регистра 10 состояния, а по шине 14 на вход блока 11 прерывания, с выхода которого по шине 17 в микро-ЭВМ поступает сигнал запроса прерывания. При этом все микро-ЭВМ подсистемы переходят по прерыванию на обслуживание устройства для сопряжения. Из регистра. 10 считывается информация по шине 17 в микро-ЭВМ, которая анализирует разряды регистра 10, и опре

делив, что выполняется ojrepaukH обмена, считывает по шине 17 из регистра 9 информационное слово в регистр общего назначения микро-ЭВМ, и это слово воспринимается как данные. . Обобщённый условный переход (OST1)

Операция ОУП служит для синхрони зацйи микро-ЭВМ, входящих в подсистему и является переходной между выполнением системных операций обмена и обобщенного безусловного перехода. Операция ОУП выполняется следующим образом. Микро-ЭВМ, завершившая работу по программе (подпрограмме) параллельной ветви, устанавливает регистр 4 синхронизации по шине 17 и разрешении с четвертого выхода дешифратора 3 в единичное состояние, С выхода регистра 4 по шине 19 сигна системной синхронизации поступает в блок 1. В момент установки всех регистров 4 устройств для сопряжения подсистемы в единичное состояние в блоках 1 вырабатывается сигнал обобщенного условия, который поступает с выхода блока коммутации и по шине 14 заносится в соответствукяций разряд регистра 10. Одновременно этот сигнал поступает в блок 11, с выхода которого по шине 17 в микро-ЭВМ поступает запрос.на прерывание, и если микро-ЭВМ отвечает по шине 17 сигналом готовности, то из блока 11 считы:вается соответствующий вектор прерывания, который по шине 17 поступает в микро-ЭВМ, с выхода регистра 10

J текущее слово состояния устройства по шине 17 поступает в микро-ЭВМ, а после этого микро-ЭВМ переходит к следующему этапу параллельных вычислений.

Обобщенный безусловный переход (ОБУП).

Операция,ОБУП выполняется после операции ОУП, т.е. все микро-ЭВМ переходят к следующему этапу параллельных вычислений. Управление дальнейшим ходом параллельных вычислений берет на себя одна из микро-ЭВМ подсистемы. При этом по шине 17 в даиифратор 3 поступает код, соответствующий операции ОБУП, и на втором и пятом выходах дешифратора 3 появляется сигнал системного ОБУП. Со второго ВЕЯхода дешифратора 3 этот сигнал поступает через элементы ИЛИ 7 и 8 на управлякмций вход регистра 9 и с выхода элемента ИЛИ 7 в соответствующий разряд регистра 10 состояния. С пятого выхода дешифратора 3 сигнал ОБУП по шине 18 поступит в блок 1 коммутации. По шине 17 информационно слово записывается в регистр 9 взаимодействия, а также через блок 1 коммутации поступает на шину 12 устройства. В принимающих устройствах для сопряжения сигнал поступает с шины 13 через блок 1 коммутации по шле 14- в блок .1J. прерывания с выхода

которого по шине 17 в микро-ЭВМ поступает Сигнал запроса прерывания. Кроме того, по шине 14 сигнал ОБУЛ поступает через элементы ПЛИ 7 и ИЛИ В на управ: яющий вход регистра 9, разрешая запись в регистр 9 информационного слова по шине 15 через блок 1 коммутации с шины 12, С выхода элемента ИЛИ 7 сигнал ОБУП поступает также в соответствующий разряд регистра 10.

По прерыванию все микро-ЭВМ переходят на обслуживание устройства для сопряжения. Из регистра (, считывается информация по шине 17 в микро-ЭВМ, которая анализирует, что выполняется операция ОБУП, и по шине 17 из регистра 9 взаимодействия в микро-ЭВМ считывает информационное слово, которое воспринимается как адрес либо как команда, и все микроЭВМ переходят на новую ветвь параллельных вычислений.

Таким образом, предлагаемое устройство обеспечивает выполнение всех функций известного при сокращенном объеме оборудования.

Формула.изобретения

Устройство для сопряжения однородной вычислительной системы, содержащее блок коммутации, первый и второй информационные и управляющий входывыходы которого являются соответственно первым и вторым информационными и управляющим входами-выходами устройства, блок настройки, дешифратор адреса регистра, первым выходом соединенный с первым управляющим входом блока коммутации, регистр системной синхронизации, блок взаимодействий, включающий первый и второй элементы ИЛИ и регистр взаимодействия, регистр состояния и блок прерывания, причем управляющий выход блокакоммутации соединен с первыми входами блока настройки, первого и второго

элементов ИЛИ, регистра состояния и входом блока прерывания, вход-выход .которого соединен с выходом, регистра состояния, с выходом -регистра взаимодействия, первым входом регистf pa системной синхронизации, входом дешифратора адреса регистра, вторым входом блока настройки и вторым информационным входом-выходом блока ком мутации,информационный выход KOTOpoigo

Q соединен с информационным входом регистра взаимодействия и третьим входом рлока настройки,четвертый вход которого соединен с первым выходом дешифратора адреса регистра,второй, ;третий. четвертый и пятый выходы которого соединены соответственно со вторыми входами первого элемешра ИЛИ/ второго элемента ИЛИ, регистра системной синхронизации и вторым управляющим входом блока коммутации, третий управляющий вход которого соединен с выходом регистра системной синхронизации, второй выход блока настройки соедине н jco вторым входом регистра

5 сос ояния третий и четвертый входы которого соединены соответственнос выходами первого и второго элементов ИЛИ, отличающееся тем, что, с целью сокращения объема обо0 РУДОвания.в блок взаимодействий устройства введен третий элемент ИЛИ. причем первый вход третьего элемента ИЛИ соединен с выходом первого элемента ИЛИ. второй вход - с выходом

5 второго элемента ИЛИ/ а выход - с управляющим входом регистра взаимодействия.

Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР 479103, кл. G Об F 3/04, 1972.

2. Авторское свидетельство СССР по заявке № 2713451/18-24, кл. G 06 F 3/04, 1978 (прототип).

Ь 1

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения для однороднойВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU851387A1 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU951287A2 |

| Устройство для сопряжения однородной вычислительной системы | 1983 |

|

SU1117625A1 |

| Устройство для сопряжения ЭВМ в однородной вычислительной системе | 1985 |

|

SU1280379A1 |

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

| Устройство для сопряжения однородной вычислительной системы | 1978 |

|

SU769523A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения однородной вычислительной системы | 1986 |

|

SU1312588A2 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

Авторы

Даты

1981-11-30—Публикация

1980-03-18—Подача