1

Изобретение относится к вычислительной технике и предназначено для получения целочисленных решений прямой и обратной задач оптимального резервирования при любых законах распределения времени 5 между отказами устройств.

Предлагаемое техническое решение является усовершенствованием известного устройства, описанного в авт. свид. № 419917.10

Аналоговый оптимизатор по основному изобретению содержит k блоков нелинейности, выходы которых соединены со входами блока перемножения, k блоков умножения на постоянный коэффициент, выходы is которых соединены со входами сумматора и первыми входами соответствуюших блоков нелинейности, переключатель, k схем установки затрат, блок развертки и блок измерения градиента, первый и второй 20 входы которого через переключатель подключены ко вторым входам и выходам блоков нелинейности. Выход блока развертки соединен со входами k схем установки затрат, первый и второй выходы каж- 25 дои из которых соединены со входами соответствуюшего блока умножения на постоянный коэффициент и через переключатель с третьим и четвертым входами блока измерения градиента.30

Недостатком такого оптимизатора являются малые точность и быстродействие, связанные с большим объемом переключений, ручных регулировок и измерений, выполняемых оператором в процессе решения с субъективными ошибками.

Целью изобретения является повышение точности работы и быстродействия аналогового оптимизатора.

Эта цель достигается тем, что в аналоговый оптимизатор введены k блоков памяти, блок сравнения, интегратор и блок синхронизации, первый выход которого через интегратор соединен с управляюш,им входом блока сравнения, выходы которого подключены к дополнительным входам блоков умножения на постоянный коэффициент и к группе входов блока синхронизации, второй выход которого соединен с дополнительным входом переключателя, дополнительные выходы которого подключены к первым входам блоков памяти, вторые входы которых соединены с третьим выходом блока синхронизации, первый и второй входы которого подключены соответственно к выходам блока перемножения и сумматора.

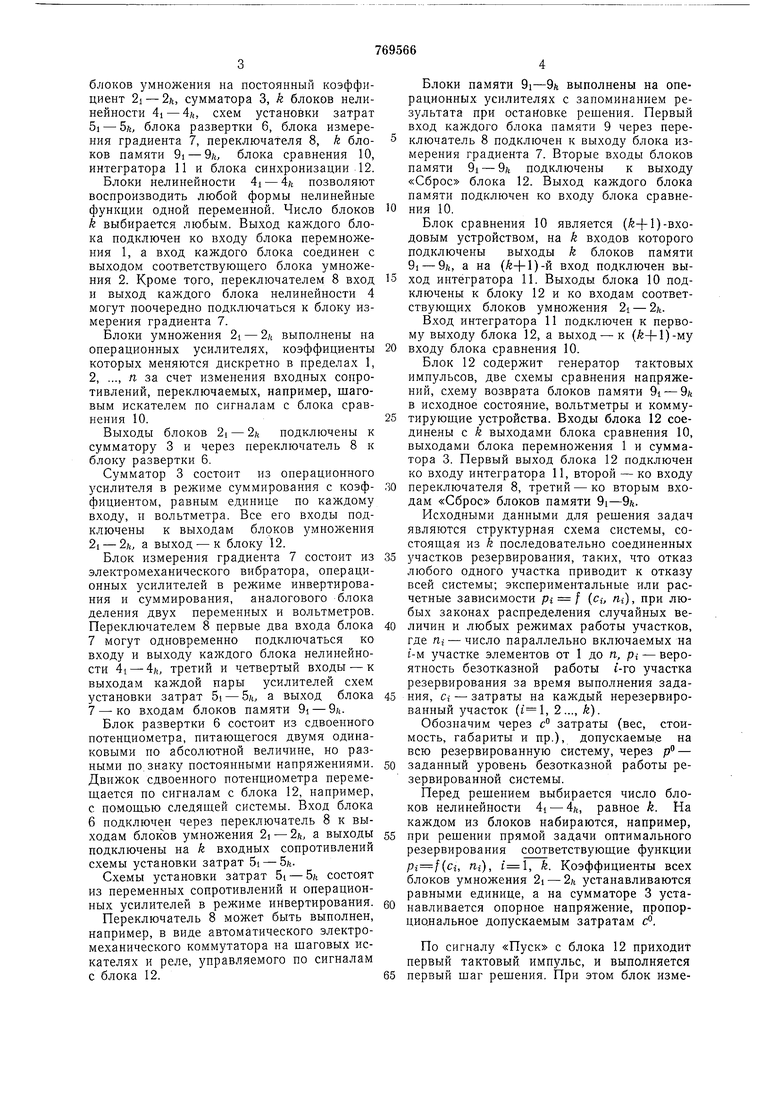

На чертеже приведена структурная схема предлагаемого аналогового оптимизатора. Он состоит из блока перемножения 1, k

блоков умножения на постоянный коэффициент 2 - 2ft, сумматора 3, k блоков нелинейности 4i - 4ft, схем установки затрат 5 - 5ft, блока развертки 6, блока измерения градиента 7, переключателя 8, k блоков памяти 9i - 9ft, блока сравнения 10, интегратора 11 и блока синхронизации 12.

Блоки нелинейности 4i - 4ft позволяют воспроизводить любой формы пелинейпые функции одной переменной. Число блоков k выбирается любым. Выход каждого блока подключен ко входу блока перемножения 1, а вход каждого блока соединен с выходом соответствующего блока умножения 2. Кроме того, переключателем 8 вход и выход каждого блока нелинейности 4 могут поочередно подключаться к блоку измерения градиента 7.

Блоки умножения 2i - 2/; выполнены на операционных усилителях, коэффициенты которых меняются дискретно в пределах 1, 2, ..., п за счет изменения входных сопротивлений, переключаемых, например, шаговым искателем по сигналам с блока сравнения 10.

Выходы блоков 2i - 2ft подключены к сумматору 3 и через переключатель 8 к блоку развертки 6.

Сумматор 3 состоит из операционного усилителя в режиме суммирования с коэффициентом, равным единице по каждому входу, п вольтметра. Все его входы подключены к выходам блоков умножения 2i - 2ft, а выход - к блоку 12.

Блок измерения градиента 7 состоит из электромеханического вибратора, операционных усилителей в режиме инвертирования и суммирования, аналогового блока деления двух переменных и вольтметров. Переключателем 8 первые два входа блока 7 могут одновременно подключаться ко входу и выходу каждого блока нелинейности 4i - 4ft, третий и четвертый входы - к выходам каждой пары усилителей схем установки затрат 5i - 5й, а выход блока 7 - ко входам блоков памяти 9i - 9ft.

Блок развертки 6 состоит из сдвоенного потенциометра, питающегося двумя одинаковыми по абсолютной величине, но разными по, знаку постоянными напряжениями. Движок сдвоенного потенциометра перемещается по сигналам с блока 12, например, с помощью следящей системы. Вход блока 6 подключен через переключатель 8 к выходам блокЪв умножения 2i - 2ft, а выходы подключены на k входных сопротивлений схемы установки затрат Si - 5ft.

Схемы установки затрат 5i - 5ft состоят из переменных сопротивлений и операционных усилителей в режиме инвертирования.

Переключатель 8 может быть выполнен, например, в виде автоматического электромеханического коммутатора на шаговых искателях и реле, управляемого по сигналам с блока 12.

Блоки памяти 9i-9ft выполнены на операционных усилителях с запоминанием результата при остановке рещения. Первый вход каждого блока памяти 9 через переключатель 8 подключен к выходу блока измерения градиента 7. Вторые входы блоков памяти 9i - 9ft подключены к выходу «Сброс блока 12. Выход каждого блока памяти подключен ко входу блока сравнения 10.

Блок сравнения 10 является (+1)-входовым устройством, на k входов которого подключены выходы k блоков памяти 9i - 9ft, а на )-й вход подключен выход интегратора 11. Выходы блока 10 подключены к блоку 12 и ко входам соответствующих блоков умножения 2i - 2ft.

Вход интегратора И подключен к первому выходу блока 12, а выход - к (/г+1)-му

входу блока сравнения 10.

Блок 12 содержит генератор тактовых импульсов, две схемы сравнения напряжений, схему возврата блоков памяти 9i-9ft в исходное состояние, вольтметры и коммутирующие устройства. Входы блока 12 соединены с k выходами блока сравнения 10, выходами блока перемножения 1 и сумматора 3. Первый выход блока 12 подключен ко входу интегратора 11, второй - ко входу

переключателя 8, третий - ко вторым входам «Сброс блоков памяти 9i-9ft.

Исходными данными для решения задач являются структурная схема системы, состоящая из k последовательно соединенных

участков резервирования, таких, что отказ любого одного участка приводит к отказу всей системы; экспериментальные или расчетные зависимости pi f (Сг, Пг), ПрИ ЛЮбых законах распределения случайных величин и любых режимах работы участков, где Пг - число параллельно включаемых на 1-м участке элементов от 1 до п, р, - вероятность безотказной работы t-ro участка резервирования за время выполнения задания, Сг - затраты на каждый нерезервированный участок (, 2..., k).

Обозначим через с затраты (вес, стоимость, габариты и пр.), допускаемы.е на

|0 -

всю резервированную систему, через р

заданный уровень безотказной работы резервированной системы.

Перед решением выбирается число блоков нелинейности 4i - 4ft, равное k. На каждом из блоков набираются, например,

при решении прямой задачи оптимального резервирования соответствующие функции (ci, Пг), , k. Коэффициенты всех блоков умножения 2i - 2ft устанавливаются равными единице, а на сумматоре 3 устанавливается опорное напряжение, пропорцианальное допускаемым затратам с°.

По сигналу «Пуск с блока 12 приходит

первый тактовый импульс, и выполняется

первый шаг решения. При этом блок измерения градиента 7 переключателем 8 подключается к клеммам первого блока нелинейности 4i и первой схемы установки затрат 5i, а также к первому блоку памяти 9i. Напряжение на третьем и четвертом входах блока измерения градиента 7 модулируется вибратором и подается на вход блока нелинейности 4i. С его выхода снимается модулированное напряжение, которое преобразуется в переменное напряжение, пропорциональное по амплнгуде приращению функции pi на шаге Ci. Это напряжение подается как делимое на вход блока деления в блоке измерения градиента 7. На другой вход блока деления подается как делитель напряжение, полученное как разность напряжений на третьем и четвертом входах блока измерения градиента 7. Напряжение AI с выхода блока 7 подается на вход блока памяти 9i и запоминается.

С приходом второго тактового импульса переключатель 8 подключает входы и выход блока измерения градиента 7 к клеммам следующих блока нелинейности 42, схемы установки затрат 62, блока памяти 92 и аналогично запоминается величина А2 и т. д. до последнего блока нелинейности 4k.

При этом напряжения с выходов блоков умножения 2 - 2h последовательно синхронно подаются переключателем 8 на вход блока развертки 6. Его следящая система перемещает движок сдвоенного потенциометра, последовательно обеспечивая равенство напряжений на выходе каждого блока 2i - 2k и на выходе блока развертки 6.

По окончании первого цикла замеров и запоминания по сигналу с блока 12 запускается интегратор 11, с выхода которого на (й+1)-й вход блока сравнения 10 подается линейно убывающее напряжение. Как только линейно убывающее напряжение по абсолютной величине станет равным какомулибо одному из напряжений Дъ , k оказавшемуся максимальным среди всех остальных, с соответствующего выхода блока сравнения 10 подается сигнал на соответствующий блок умножения 2ь 1, k, и его коэффициент увеличивается на единицу,

Одновременно с третьего выхода блока 12 подается импульс «Сброс на вторые входы блоков памяти 9i - 9h, и блоки памяти возвращаются в исходное состояние, с первого - сигнал на переключатель 8, и клеммы блоков 4i, 5i, 9i снова подключаются к блоку измерения градиента 7. Интегратор И возвращается в исходное состояние автоматически.

С приходом следующего тактового импульса начинается выполнение второго шага решения, и цикл повторяется.

После выполнения ;V шагов решения напряжение на выходе сумматора 3 может быть равным нулю (наложенное ограничение по затрате израсходовано точно) либо больше нуля (перерасход). В последнем случае уменьшается на единицу коэффициент того блока умножения, у которого на шаге этот коэффициент был увеличен на единицу. Оценивается показание прибора сумматора 3 и, если оно по абсолютной величине меньше любого из значений с, тс решение закончено.

Напряжение на выходе блока перемножения 1 соответствует достигнутому значению целевой функции для всей резервированной системы, напряжение на выходе сумматора 3 соответствует суммарной затрате, а зафиксированный коэффициент каждого блока умножения 2,-, , k соответствует числу параллельно включенных устройств на каждом участке резервирования.

Благодаря введению новых элементов и связей устройство обеспечивает более высокую точность и быстродействие получения статистических характеристик проектируемой аппаратуры.

Формула изобретения

Аналоговый оптимизатор по авт. свид. N° 419917, отличающийся тем, что, с целью повышения точности работы и быстродействия, в него введены k блоков памяти, блок сравнения, интегратор и блок сннхронизации, первый выход которого через интегратор соединен с управляющим входом блока сравнения, выходы которого подключены к дополнительным входам блоков умножения на постоянный коэффициент И к группе входов блока синхронизации, второй выход которого соединен с дополнительным входом переключателя, дополнительные выходы которого подключены к первым входам блоков памяти, вторые входы которых соединены с третьим выходом блока синхронизации, первый и второй входы которого подключены соответственно к выходам блока перемножения и сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый оптимизатор | 1973 |

|

SU475630A1 |

| АНАЛОГОВЫЙ ОПТИМИЗАТОР | 1971 |

|

SU419917A1 |

| Аналоговый оптимизатор числа запасных блоков | 1978 |

|

SU752386A1 |

| Аналоговый оптимизатор | 1977 |

|

SU708365A1 |

| Аналоговый оптимизатор числа запасных элементов | 1981 |

|

SU1042040A1 |

| Устройство для решения задач дискретного программирования | 1977 |

|

SU739562A1 |

| Система идентификации параметров многомерного нелинейного динамического объекта | 1986 |

|

SU1385122A1 |

| Аналоговый оптимизатор числа запасных блоков технической системы | 1987 |

|

SU1547003A2 |

| БИКОРРЕЛОМЕТР | 1992 |

|

RU2022358C1 |

| Аналоговый оптимизатор | 1976 |

|

SU643899A1 |

Авторы

Даты

1980-10-07—Публикация

1978-09-25—Подача