1

Изобретение относится к технике связи и может использоваться в системах передачи данных.

Известно устройство формирования импульсного отклика канала связи, содержащее линию задержки с п+1 отводами, каждый из которых соединен соответственно с первыми входами каждого из п+1 регуляторов и с первыми входами каждого из п + корреляторов, выходы которых соответственно подсоединены ко вторым входам каждого из п+ регуляторов, первый сумматор, вход которого подключен к объединенным выходам п+1 регуляторов, второй сум.матор, выход которого соединен с объединенными входа.ми каждого из п+1 корреляторов 1.

Однако такое устройство имеет невысокую точность формирования импульсного отклика канала связи.

Цель изобретения - повышение точности формирования импульсного отклика канала связи.

Для этого в устройство формирования импульсного отклика канала связи, содсржаш,ее линию задержки с п+1 отводами, каждый из которых соединен соответственно с первыми входа.ми каждого из п+1 регуляторов и с первыми входами каждого из rt+1 корреляторов, выходы которых соответственно подсоединены ко вторым входам каждого из п+1 регуляторов, первый сумматор, вход которого подключен к объединенным выходам п+1 регуляторов, второй сумматор, выход которого соединен с объединенными входами каждого из п + 1 корреляторов, введены генератор испытательной иоследовательности сигналов, приемник синхросигналов, блок памяти, фор1П мирователь сигнала готовности приемника, инвертор, элемент сравнения, блок формирования иорога, элемент совпадения, ири этом первый выход приемника синхросигналов через последовательно соединенные

115 ключ II элемент совпадения подключен ко входу блока памяти, второй выход подключен ко входу формирователя сигнала готовности приемника и через генератор испытательной последовательности сигналов ко

20 входу линии задержки с п+1 отводами и вход ириемника сиихросигналов подсоединен через второй сумматор к первому входу элемента сравнения, второй вход которого подключен к выходу блока формирования порога, а выход подсоедииен ко второму входу элемента совпадения, вы.чод первого сумматора через иивертор иодключеи ко второму входу второго сумматора, и выходы n-f 1 корреляторов объединены и

2iQ подключены ко входу блока памяти.

3

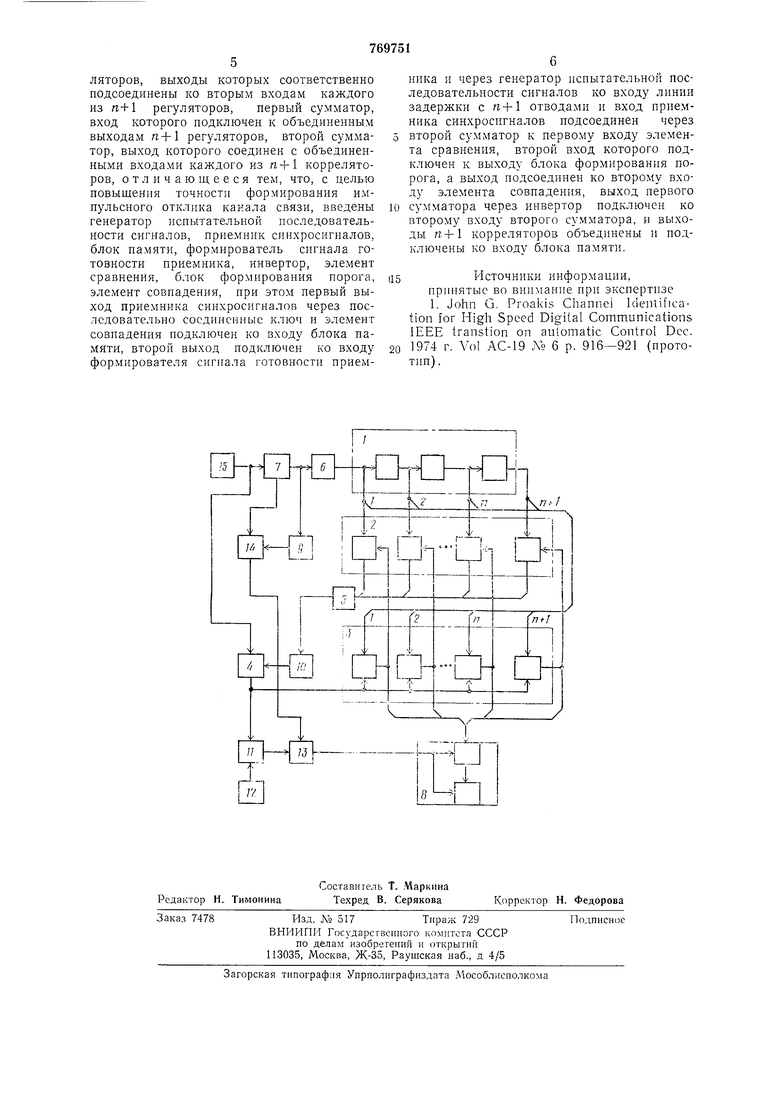

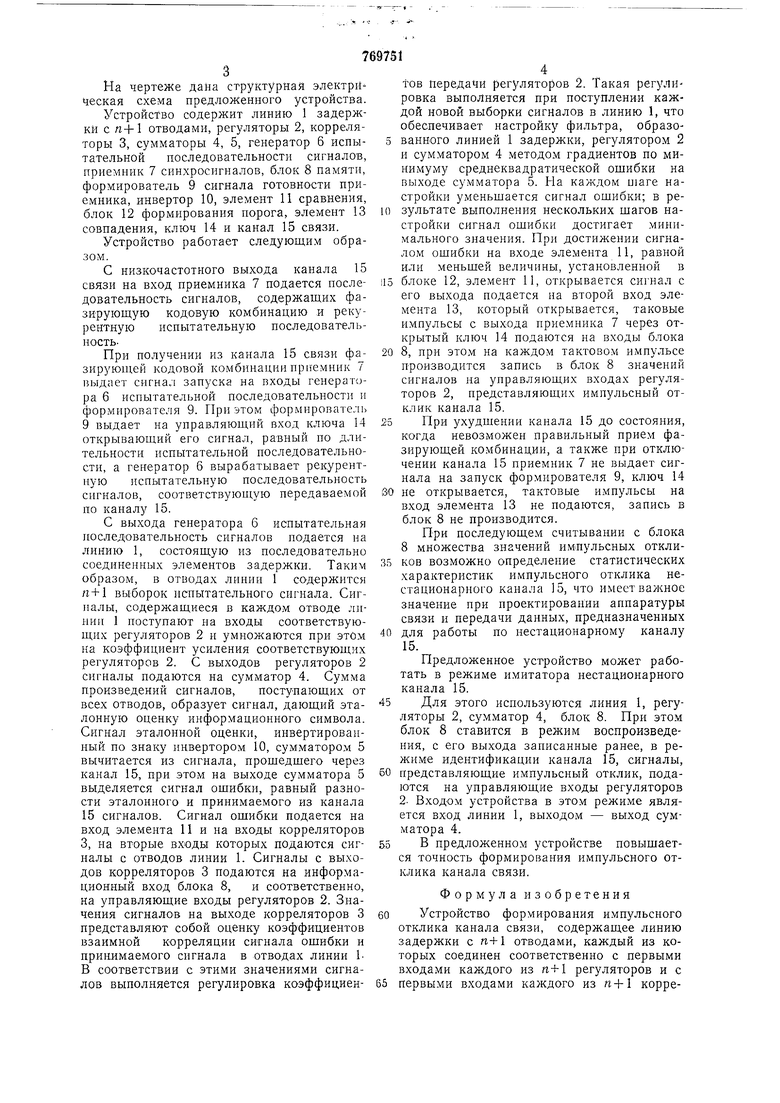

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит линию 1 задержки с п+1 отводами, регуляторы 2, корреляторы 3, сумматоры 4, 5, генератор 6 испытательной последовательности сигналов, приемник 7 синхросигналов, блок 8 памяти, формирователь 9 сигнала готовности приемника, инвертор 10, элемент 11 сравнения, блок 12 формирования иорога, элемент 13 совпадения, ключ 14 и канал 15 связи.

Устройство работает следующим образом.

С низкочастотного выхода канала 15 связи на вход приемника 7 подается последовательность сигналов, содержащих фазирующую кодовую комбинацию и рекурентную испытательную последовательность.

При получении из канала 15 связи фазируюп1,ей кодовой комбинации приемник 7 выдает сигнал запуска на входы генератора 6 испытательной последовательности и формирователя 9. При этом формирователь 9 выдает на управляющий вход ключа 14 открывающий его сигнал, равный по длительности испытательной последовательности, а геиератор 6 вырабатывает рекурентпую испытательную последовательность сигналов, соответствующую передаваемой по каналу 15.

С вы.хода генератора 6 испытательная последовательность сигналов подается па линию 1, состоящую из последовательно соединенных элементов задержки. Таким образом, в отводах лииии 1 содержится п+ выборок испытательного сигнала. Сигпалы, содержащиеся в каждом отводе линии 1 поступают на входы соответствующих регуляторов 2 и умножаются при этом на коэффициент усиления соответствующих регуляторов 2. С выходов регуляторов 2 сигналы подаются на сумматор 4. Сумма произведений сигналов, поступающих от всех отводов, образует сигнал, дающий эталонную оценку информационного символа. Сигнал эталонной оценки, инвергирова)ный по знаку инвертором 10, сумматором 5 вычитается из сигнала, прошедшего через канал 15, при этом на выходе сумматора 5 выделяется сигнал ошибки, равный разности эталонного и принимаемого из канала 15 сигналов. Сигнал ошибки подается на вход элемента 11 и на входы корреляторов 3, на вторые входы которых подаются сигналы с отводов линии 1. Сигналы с выходов корреляторов 3 подаются на информационный вход блока 8, и соответственно, на управляющие входы регуляторов 2. Значения сигналов на выходе корреляторов 3 представляют собой оценку коэффициентов взаимной корреляции сигнала ошибки и принимаемого сигнала в отводах линии 1В соответствии с этими значениями сигналов выполняется регулировка коэффициен769751

тов передачи регуляторов 2. Такая регу.тировка выполняется при поступлении каждой новой выборки сигналов в линию 1, что обеспечивает настройку фильтра, образованного линией 1 задержки, регулятором 2 и сумматором 4 методом градиентов по минимуму среднеквадратической ошибки на выходе сумматора 5. Па каждом niare настройки уменьшается сигнал ошибки; в результате выполнения нескольких шагов настройки сигнал ошибки достигает мииимального значения. При достижении сигналом ошибки на входе элемента 11, равной или меньшей величины, установленной в

15 блоке 12, элемент И, открывается сигнал с его выхода подается на второй вход элемента 13, который открывается, таковые импульсы с выхода приемника 7 через открытый ключ 14 подаются на входы блока

20 8, при этом на каждом тактовом импульсе производится запись в блок 8 значений сигналов на управляющих входах регуляторов 2, иредставляющих импульсный отклик канала 15.

5 При ухудшении канала 15 до состояния, когда невозможен правильный прием фазирующей комбинации, а также при отключении канала 15 приемник 7 не выдает сигнала на запуск формирователя 9, ключ 14

i30 не открывается, тактовые импульсы на вход элемента 13 не подаются, запись в блок 8 не производится.

При последующем считывании с блока 8 множества значений им1пульсных откликов возможно определение статистических характеристик импульсного отклика нестационарного канала 15, что имеет важное значение ири проектировании аппаратуры связи и передачи данных, предназначенных

0 для работы по нестационарному каналу 15.

Предложенное устройство может работать в режиме имитатора нестационарного канала 15.

5 Для этого используются линия 1, регуляторы 2, сумматор 4, блок 8. При этом блок 8 ставится в режим воспроизведения, с его выхода заиисанные ранее, в режиме идентификации канала 15, сигналы,

0 представляющие импульсный отклик, подаются на управляющие входы регуляторов 2. Входом устройства в этом режиме является вход линии 1, выходом - выход сумматора 4.

5 В предложенном устройстве повышается точность формирования имиульсного отклика канала связи.

Формула изобретения

0 Устройство формирования импульсного отклика канала связи, содержащее линию задержки с п+1 отводами, каждый из которых соединен соответственно с первыми входами каждого из п+1 регуляторов и с

первыми входами каждого из п+1 корреляторов, выходы которых соответственно подсоединены ко вторым входам каждого из п+1 регуляторов, первый сумматор, вход которого подключен к объединенным выходам п+1 регуляторов, второй сумматор, выход которого соединен с объединенными входами каждого из n-f 1 корреляторов, отличающееся тем, что, с целью повышения точности формирования импульсного отклика канала связи, введены генератор испытательной последовательности сигналов, приемник синхросигналов, блок памяти, формирователь сигнала готовности приемника, инвертор, элемент сравнения, блок формирования порога, элемент совпадения, при этом первый выход приемника синхросигналов через последовательно соединенные ключ и элемент совпадения иодключен ко входу блока памяти, второй выход подключен ко входу формирователя сигнала готовности приемника и через генератор испытательной последовательности сигналов ко входу линии задержки с п+1 отводами и вход приемника синхросигналов подсоединен через

второй сумматор к первому входу элемента сравнения, второй вход которого подключен к выходу блока формирования порога, а выход подсоединен ко второму входу элемента совпадения, выход первого

сумматора через инвертор подключен ко второму входу второго сумматора, и выходы п+1 корреляторов объединены и подключены ко входу блока памяти.

Источники информации,

принятые во внимание ири экспертизе 1. John G. Proaids Channei Identification for High Speed Digital Communications IEEE transtion on automatic Control Dec. 1974 Г. Vol AC-19 Л9 6 p. 916-921 (ирототии).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный корректор сигнала с парциальным откликом | 1982 |

|

SU1073890A1 |

| Устройство для контроля качества сигнала многоканальных систем связи | 1978 |

|

SU777835A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ, РАСПРОСТРАНЯЮЩИХСЯ В МНОГОЛУЧЕВОМ КАНАЛЕ | 2014 |

|

RU2560102C2 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПРОШЕДШИХ МНОГОЛУЧЕВОЙ КАНАЛ СВЯЗИ | 2013 |

|

RU2528134C1 |

| Нелинейный корректор многолучевого сигнала | 1984 |

|

SU1197096A2 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПРОШЕДШИХ МНОГОЛУЧЕВОЙ КАНАЛ СВЯЗИ | 2013 |

|

RU2541908C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ, ПРОШЕДШИХ МНОГОЛУЧЕВОЙ КАНАЛ СВЯЗИ | 2013 |

|

RU2544178C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ, РАСПРОСТРАНЯЮЩИХСЯ В МНОГОЛУЧЕВОМ КАНАЛЕ | 2014 |

|

RU2549888C1 |

| ПРИЕМНИК СИНХРОСИГНАЛА | 2002 |

|

RU2242093C2 |

| ЦИФРОВОЙ АДАПТИВНЫЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2039416C1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-02—Подача