8го&

I Выпад

О

««ч

О СО

ot

Изобретение относится к системам передачи дискретной информации по каналам с частотно-временной дисперсией (многолучевостью), а именно к устройствам, снижающим межсимвольную интерференцию в многолучевом канале, и является усовершенствованием известного устройства по основному авт. св. № 11А6808.

Цель изобретения - повышение помехоустойчивости приема.

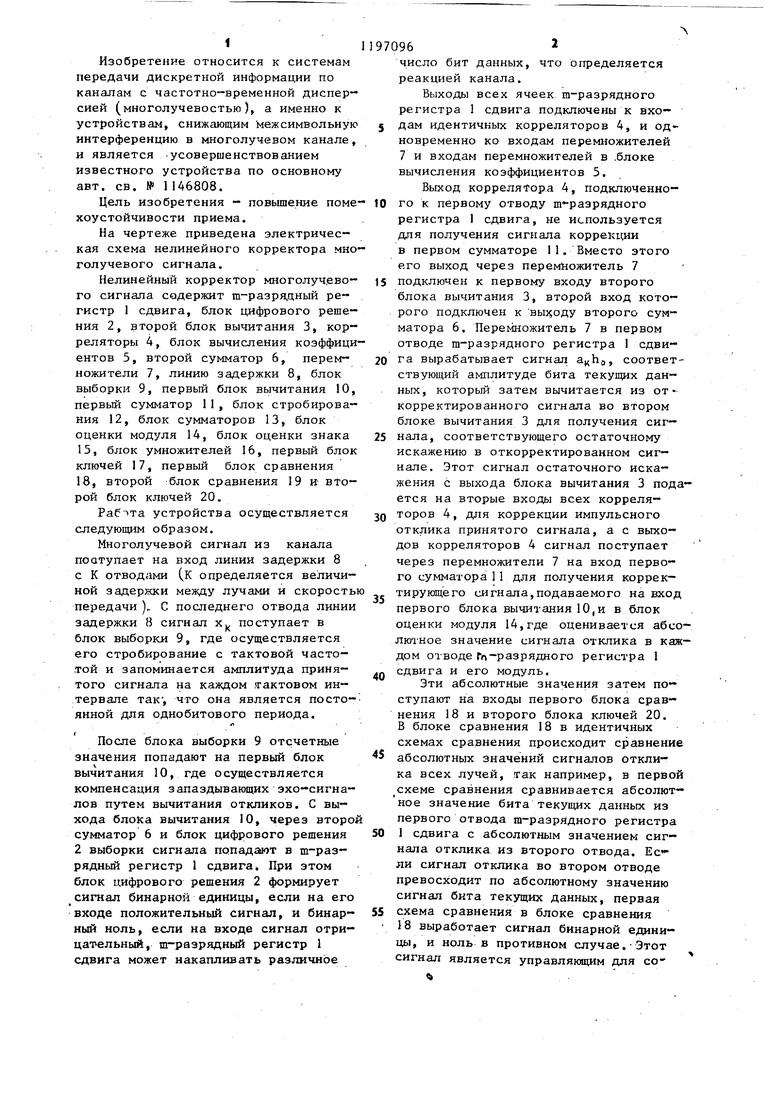

На чертеже приведена электрическая схема нелинейного корректора многолучевого сигнала.

Нелинейный корректор многолуч.евого сигнала содержит т-разря,цный регистр 1 сдвига, блок цифрового решения 2, второй блок вычитания 3, корреляторы 4, блок вычисления коэффициентов 5, второй сумматор 6, перем- ножители 7, линию задержки 8, блок выборки 9, первый блок вычитания 10, первый сумматор 11, блок стробирова- ния 12, блок сумматоров 13, блок оценки модуля 14, блок оценки знака 15, блок умножителей 16, первый блок ключей 17, первый блок сравнения 18, второй :блок сравнения 19 и- второй блок ключей 20.

устройства осуществляется следующим образом.

Многолучевой сигнал из канала псотупает на вход линии задержки 8 с К отводами (к определяется величиной задержки между лучами и скорость передачи )„ С последнего отвода линии задержки В сигнал х поступает в блок выборки 9, где осуществляется его стробирование с тактовой частотой и запоминается амплитуда принятого сигнала на каждом .тактовом интервале так , что она является посто- янной для однобитового периода.

1После блока выборки 9 отсчетные значения попадают на первый блок вычитания 10, где осуществляется компенсация запаздывающих эхо-сигналов путем вычитания откликов. С выхода блока вычитания 10, через второ сумматор 6 и блок цифрового решения 2 выборки сигнала попадают в т-раз- рядный регистр 1 сдвига. При этом блок цифрового решения 2 формирует сигнал бинарной единицы, если на его входе положительный сигнал, и бинарный ноль, если на входе сигнал отрицательный, пг-раэрядный регистр 1 сдвига может накапливать различное

970962

число бит данных, что определяется реакцией канала.

Выходы всех ячеек т-разрядного регистра 1 сдвига подключены к вхо- 5 дам идентичных корреляторов 4, и одновременно ко входам перемножителей

7и входам перемножителей в .блоке вычисления коэффициентов 5.

Выход коррелятора 4, подключенно-

0 го к первому отводу т-разрядного регистра 1 сдвига, не используется для получения сигнала коррекции в первом сумматоре I1. Вместо этого его выход через перемйожитель 7

15 подключен к первому входу второго блока вычитания 3, второй вход которого подключен к выз;оду второго сумматора 6. Пере 1ножитель 7 в первом отводе т-разрядного регистра 1 сдвига вырабатывает сигнал ацЬд, соответствующий амплитуде бита текущих данных, который затем вычитается из откорректированного сигнала во втором блоке вычитания 3 для получения сиг-

5 нала, соответствующего остаточному искажению в откорректированном сигнале. Этот сигнал остаточного искажения с выхода блока вычитания 3 подается на вторые входы всех корреля-

0 торов 4, для коррекции импульсного отклика принятого сигнала, а с выходов корреляторов 4 сигнал поступает через перемножители 7 на вход первого сумматора 1 1 для получения корректирующего сигнала,подаваемого на вход первого блока вычитания 10,и в блок оценки модуля 14,где оценивается абсолютное значение сигнала отклика в каждом отводе Гц-разрядного регистра 1 сдвига и его модуль.

Эти абсолютные значения затем поступают на входы первого блока сравнения 18 и второго блока ключей 20.

8блоке сравнения 18 в идентичных

схемах сравнения происходит сравнение абсолютных значений сигналов отклика всех лучей, .так например, в первой схеме сравнения сравнивается абсолютное значение бита текущих данньгх из первого отвода га-разрядного регистра 0 1 сдвига с абсолютным значением сигнала отклика из второго отвода. Если сигнал отклика во втором отводе превосходит по абсолютному значению сигнал бита текущих данных, первая 5 схема сравнения в блоке сравнения 18 выработает сигнал бинарной единицы, и ноль в противном случае.Этот сигнал является управляющим для соответствующего ключа в блоке ключей 17 и первого ключа в блоке ключей 20. Первый ключ блока ключей 20, сработав, пропускает сигнал отклика с, большим абсолютным значением для дальнейшего сравнения во второй схеме сравнения блока сравнения 18, с абсолютным значением сигнала из третьего отвода т-разрядного регистра 1 сдвига. Вторая схема сравнения блока сравнения 18 также выработает сигнал бинарной единицы или нуля, который будет управляющим для соответствующего .ключа в блоке ключей 17 и второго ключа в блоке ключей 20, Второй ключ блока ключей 20, сработав пропустит сигнал отклика с большим абсолютным значением для дальнейшего сравнения в третьей схеме сравнения . блока сравнения 18 с абсолютным значе ,нием сигнала из четвертого отвода т-разрядного регистра 1 сдвига.Третья схема сравнения блока сравнения 18 в свою очередь выработает сигнал бинарной единицы или ноль, и он также будет управлякнцим для соответствующе- го ключа в блоке 17 ключей и третье го ключа в блоке ключей 20. Срабатыва|Ние третьего ключа в блоке кЛючей 20 приводит к тому, что в четвертой схеме сравнения будет сравниваться абсолютное значение сигнала из пятого отвода т-разрядного регистра 1 сдвига с абсолютным значением сигнала с выхода третьего ключа блока ключей 20 и т.д. На последнюю схему сравнения с номером т-1 блока сравнения 18 поступает абсолютное значение сигнала из последнего отвода т-разряд-. Кого регистра 1 сдвига и аб- солютное значение сигнала с выхода ключа, имеющего номер т-1 в блоке ключей 20, Выход последней схемы сравнения с номером т-1 соединен только с входом соответствующего ключа в блоке ключей 17. На вторые входы блока ключей 17 подаются сигналы, являющиеся произведением данных о суммарном энергетическом значении откликов и их знаке. Эти сигналы вы- рабатываются в блоке умножителей16 куда они поступают на первые входы с выходов блока сумматоров 13, где на каждый из идентичных сумматоров поступают отсчеты амплитуды (простробированные выборки многолучевого сигнала, полученные в блоке стробирования 12, на входы которого искаженный в канале -сигнал подается в .аналоговом виде с отводов линии задержки 8, в виде отсчетов Х(,, ,

К-г ° линии задержки 8 сигнал с откликами подается непосредственно с канального оборудования приема.

На остальные входы блока сумматоров 13 поступают сигналы с перемно- жителей блока вычисления коэффицией- тов 5, Идентичные перемножители блока вычисления коэффициентов 5 собраны в группы с номерами от К-1 до K-IJ// по числу сумматоров в блоке сумматоров 13. Внутри каждой группы пере- множители имеют номера с первого до ,п-1. На первый вход первого перемножителя из группы К-1 блока вычисления коэффициентов 5 поступает сигналпоказатель значения импульсного отклика hj из коррелятора 4, подключенного к третьему отводу т-разрядного регист pfL 1 сдвига. На второй вход первого перемножителя поступает бит данных а 1 из ячейки т-разрядного регистра 1 сдвига с номером два. Этот бит принимает значение О или 1 в зависимости от того, какой бит был записан в предшествующий момент времени в ячейку с номером один т-разрядного регистра сдвига 1. Таким образом, на выходе первого перемножителя блока вычисления коэффи151иентов 5 появится сигнал с амплитудой, равной той , что и у импульсного отклика h2 и.с . той же полярностью, если бит данных a. принял значение 1. На второй перемножитель этой же группы поступает бит данных з ячейки с номером три т-разрядного регистра 1 сдвига, а также импульсный ртлик h из коррелятора 4, подключенного к четвертому отводу т разрядного регистра 1 сдвига. Соответственно на перемножитель с номером п-1 этой же группы поступают сигналы бита данных а ) и импульсного отклика hjj.

Результаты перемножения в блоке вычисления коэффициентов 5 поступают на соответствующие входы блока сумматоров 13,На вторые входы перемножителей блока умножителей 16 поступают биты данных, принимающих значение 1 или О из второго блока сравнения 19. Сигналы на выходах перемножителей блока умножителей I6 будут изменять знак под их воздействием. Второй .блок сравнения 19 содержит п + 1 идентичную схему сложения по модулю 2, причем на все первые входы этих схем подается одновременно бит данных о знаке импульсного отклика h , полученного йэ текущего значения бита данных в первом отводе т-раз- рядного регистра 1 сдвига. Бит данных о знаке h, вырабатывается одной из идентичных схем определения знака в блоке оценки знака 15. Схема определения знака вырабатывает бинарную I, если h имеет положительный знак,, и О, если сигнал импульс ного отклика h имеет отрицательное значение, т.е. реализует известную функцию М, sign h О, h О Аналогично работают остальные схемы определения знака в блоке оцен ки знака 15, на входы которых с выходов корреляторов 4 подаются соотве ственно h, , hj, .,.,h,j импульсные отклики. Выходы блока оценки знака 15 с номерами 1-п подключены к вторым вхо дам соответствующих сумматоров по модулю 2 блока сравнения 19, которые своими выходами соединены со вторыми входами перемножителей блока умножителей 16, сигналы на выходах которьк несут информацию об амплитуде и знаке мешающих хвостов искаженного канале рабочего сигнала. Поскольку процесс приема сигнала в условиях межсимвольной интерференции сопровож дается динамическим изменением количества лучей и их амплитуд в условия частотно-временного рассеяния сигнала, форма импульсной характеристики изменяется во времени, отражая .динамику отдельных зхо-сигналов. При зтом возможны случаи, когда кoмплekc ные .огибающие, например, двух лучей в результате интерференции временно уничтожаются, хотя за пределами интервала посылки в области ее фронтов имеют место переходные процессы с большой энергией. В следующий момент времени произойдет перераспределение энергии между лучами - основной луч будет подвержен замираниямj но в то же время резко увеличится опережа,ю- щии или наоборот - запаздывающий луч. Колеблющиеся отсчеты комплексной огибающей полной реакции канала на рабочий сигнал служат исходным материалом для выработки данных по всем лучам одновременно. Решение о переходе на лучи с большей энергетикой при одновременном отслеживании основного, запоминающего луча осуществляется в первом блоке сравнения 18, по командам которого управляются ключи в блоке ключей 17, подающие сигналы дополнительной коррекции на соответствующие первые входы блока цифрового рещения 2. Б канале часто создается такая ситуация, когда мешающие лучи по энергетике превосходят основной луч, и тогда их реакция будет немедленно учтена данным устройством без потери синхронизма. Например, если мешающих лучей несколько и все они превосходят по эиерге тике основной луч, устройство учитывает их суммарное воздействие, поскольку одновременно срабатывают несколько ключей блока ключей 17, и на второй сумматор 6 будут поданы отсчеты амплитуды сигналов дополнительной коррекции с учетом их знака. Таким образом, работой блока ключей 20 и первого блока сравнения 18 исключается возможность одновременного включения всех выходов блока сумматоров 13 на вход второго сумматора 6 при глубоких замираниях основного луча, так как будет превосходить поочередное подключение одного за другим или группы выходов блока 13 сумматоров. на вход второго сумматора 6. При этом лучи с малой мощностью и большим преддействием из процесса суммирования в сумматоре 6 будут исключены, тем самым мешающее воздействие суммарного преддействия будет минимальным, а значит, уменьшается межсимвольная интерференция и повышается помехоустойчивость приема дискретной информации. Формула изобретения Нелинейный корректор многолучевого сигнала по авт. ев, № 1146808, отличающийся тем, что, с целью повышения помехоустойчивости приема вонего введен второй блок ключей, входы которого соединены с

7 ,П970968

соответйтвующими выходами блока оцен блока сравнения, выходы которого кн модуля, а выходы подключены к со- подключены к соответствующим управответствующим вторым входам первого ляющим входам второго блока ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Адаптивный корректор межсимвольныхиСКАжЕНий B КАНАлАХ C фАзОВОйМАНипуляциЕй | 1979 |

|

SU801270A2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1985 |

|

SU1840083A1 |

| Адаптивный ранговый обнаружитель | 1979 |

|

SU800927A2 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| Адаптивный корректор межсимвольных искажений | 1983 |

|

SU1121784A2 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

Изобретение относится к системам передачи дискретной информации по сиг налам с частотно-временной дисперс-;ной (многолучевостью.Изобретение повышает помехоустойчивость приема. Блок ключей 20 и 1-и блок сравнения 18 исключает возможность одновременного включения всех выходов блока сумматоров 13 на вход второго сумматора 1с I 6 при глубоких замираниях основного луча. Происходит 1;1оочередное подключение одного за, другим, или группы выходов блока С 13 на вход .2-го С 6, Лучи с малой мощностью и большим преддействием из процесса суммирования в С 6 исключены, тем самым мешающее воздействие .-суммарного преддей- ствия будет минимальным и уменьшится межсимвольная интерференция и повысится помехоустойчивость приема дискретной информации. Изобретение зависимое от авт.свид.№ 1146808. 1 ил. СО

| Нелинейный корректор многолучевого сигнала | 1983 |

|

SU1146808A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-07—Публикация

1984-09-13—Подача