Устройство относится к электросвязи и другим областям, связанным с приемом модулированных сигналов -данных, передаваемым по каналам связи. Оно предназначено для коррек ции межсимвольной интерференции МСИ в модулированных сигналах, передава мых многопозиционными методй«1И моду ляции с использованием корреляционн го кодирования, в результате чего на выходе передатчика формируются сигналы с парциальным откликом или биимпульснуе сигналы. Известен цифровой адаптивный кор ректор сигнала с парциальным откликом содержащий первую линию задержки, вход которой через регулятор подключен к входу устройства, а выходы через соответствующие регуляторы подключены к сумматору, один из выходов которого является выходом устройства, а два других подключены к второй и третьей линия задержки, выходы которых подключены к соответствующим корреляторам, дру гие входы которых соединены с выход ми четвертой линии задержки, вход-к торой подключен к четвертому выходу сумматора, а выходы соответствующих корреляторов подключены к соответствующим регуляторам fj . Недостатком этого корректора явля ется недостаточная точность настройки ,поскольку для выработки сигналов управления коэффициентами переда чи регуляторов отводов используются коррелированные зависимые сигналы. Кроме того, этот корректор рассчитан на коррекцию многопозиционных сигналов с парциальным откликом. Известен также ци,фровой адапативный корректор сигнала с парциальным откликом, содержащий первую И -элементную линию задержки, вход которой является входом корректора, а П +1 выходов через соответствующие регуля торы подключены к входам основного сумматора, выход которого, являющийся выходом корректора, подключен к входу цифрового блока анализа и к одному из входов блока вычит-ания, выход которого подключен к входу второй (nv К) -элементной линии задержки, каждый из П t v: промежуточных выходов которой подключен через последовательно соединенные коррелятор, дополнительный сумматор и интегратор к управляющему входу соответствующего регулятора, причем вход второй ntк)-элементной линии задержки соединен через(.уп t К f 1)-и коррелятор с другим входом первого дополнительного сумматора, а другой вход каждого i- 20 из VJ+K дополнительных сумматоров соединен с выходом ti + V) ГО коррелятора, выход бл .ка перекодирования биимпульсного сиг нала,через третью линию задержки подключен к ДРУГИМ входам корреляторов И Однако это устройство обеспечивает недостаточно высокую скорость и точность настройки при коррекции МСИ в многопозиционных сигналах с парциальным откликом счислом позиций амплитуды .больше трех. Цель изобретения - повышение скорости и точности настройки корректора путем учета многопозиционности амплитуды принимаемого сигнала с парциальным откликом. Поставленная цель достигается тем, что в цифровой адаптивный корректор сигнала с парциальным откликом, содержащий первую ц -элементную линию задержки, вход которой является входом корректора, а ц +1 выходов .через соответствующие регуляторы подключ ены к входам основного сумматора, выход которого являющийся вьлходом корректора, подключен к входу цифрового блока анализа и к одному из входов блока вычитания, вы- ход которого подключен к входу второй (п ч к) -элементнойлинии зайержки, каждый из у1 + к промежуточных выходов которой подключен через последовательно соединенные коррелятор, дополнительный сумматор и интегратор к управляющему входу соответствующего регулятора, причем вход второй (htfcl -элементной линии задержки соединен через ( цi-K + )-и коррелятор с другим входом первого дополните ль нохо сумматора, а другой вход каждого I -го из и f к дополнительных сумматоров соединен с выходом (4 + к) -го коррелятора, выход блока перекодирования биимпульсного сигнала через третью линию задержки подключен к другим входам корреляторов, введены первый и второй элементы ИДИ и распределитель, состоящий из элемента памяти, блока сравнения и вспомогательного сумматора,- причем первый выход цифрового блока анализа,соединен с первыми входами первого элемента ИЛИ элементу памяти и блока сравнения, второй вход цифрового блока анализа, вторые вхрды первого элемента ИЛИ,, элемента памяти.и первые входы вспомогательного сумматора и второго элемента ИЛИ подключены к второму выходу цифрового блока анализа, третий выход которого соединен со вторыми входами второго элемента ИЛИ и вспомогательного сумматора, выход элемента памяти через блок сравнения подключен к третьему входу вспомогательного сумматора, выход которого подключен к входу блока перекодирования биимпульсного сигнала, а выходы элементов ИЛИ соединены с другими входами блока вычитания.

где n К , ,2, 3 , . , . i , где

i - порядковый номер дополнительного сумматора.

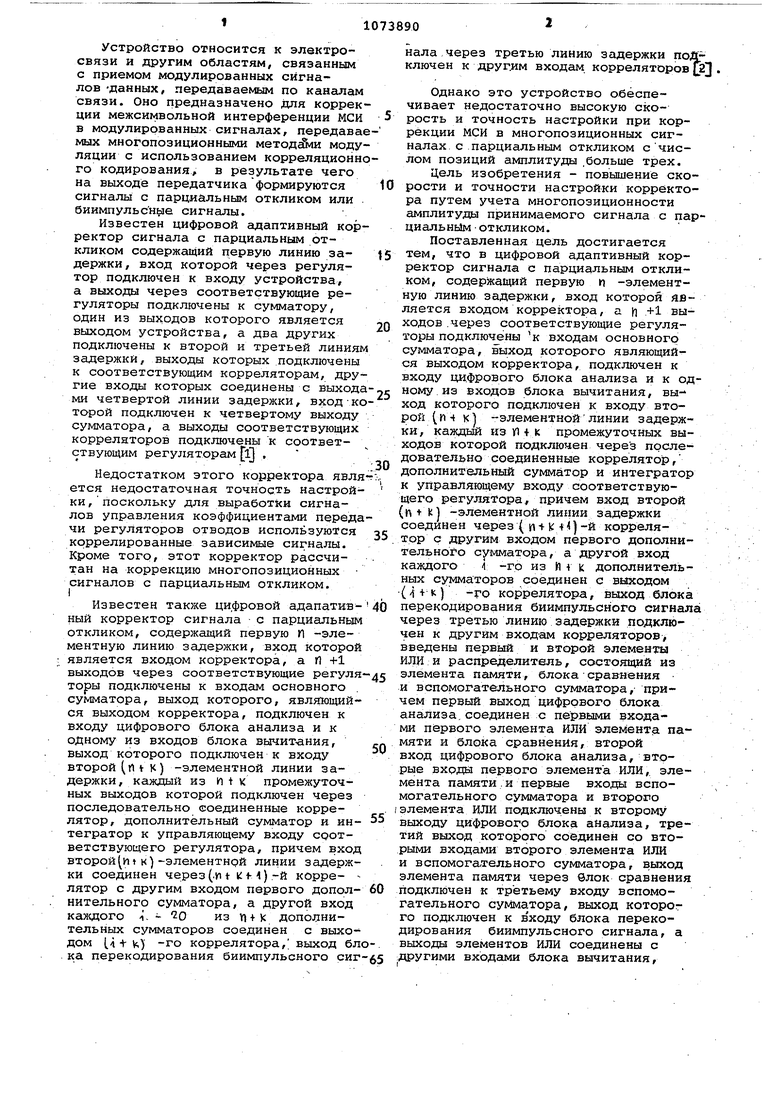

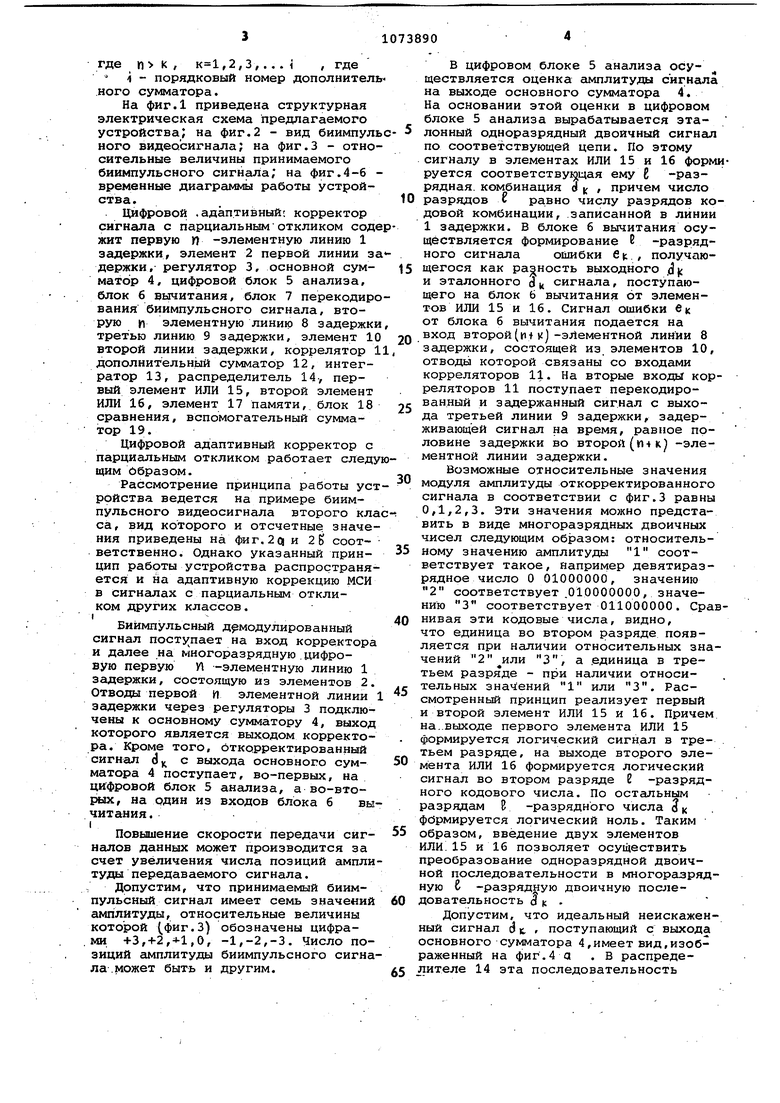

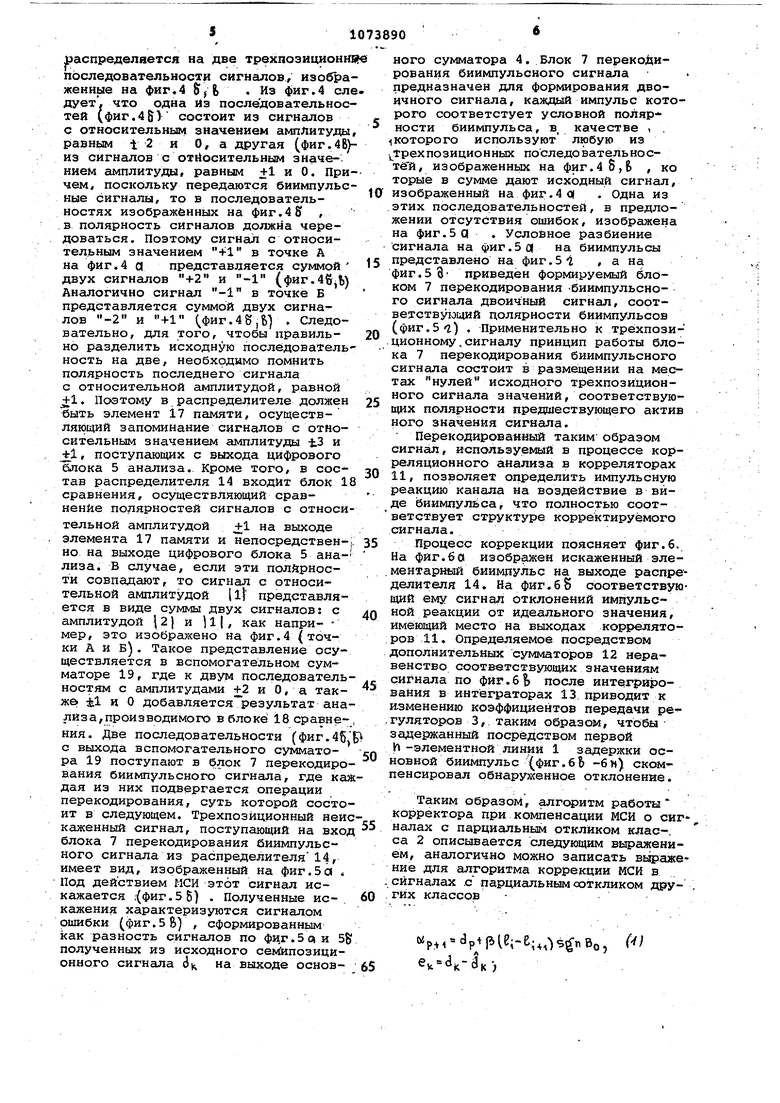

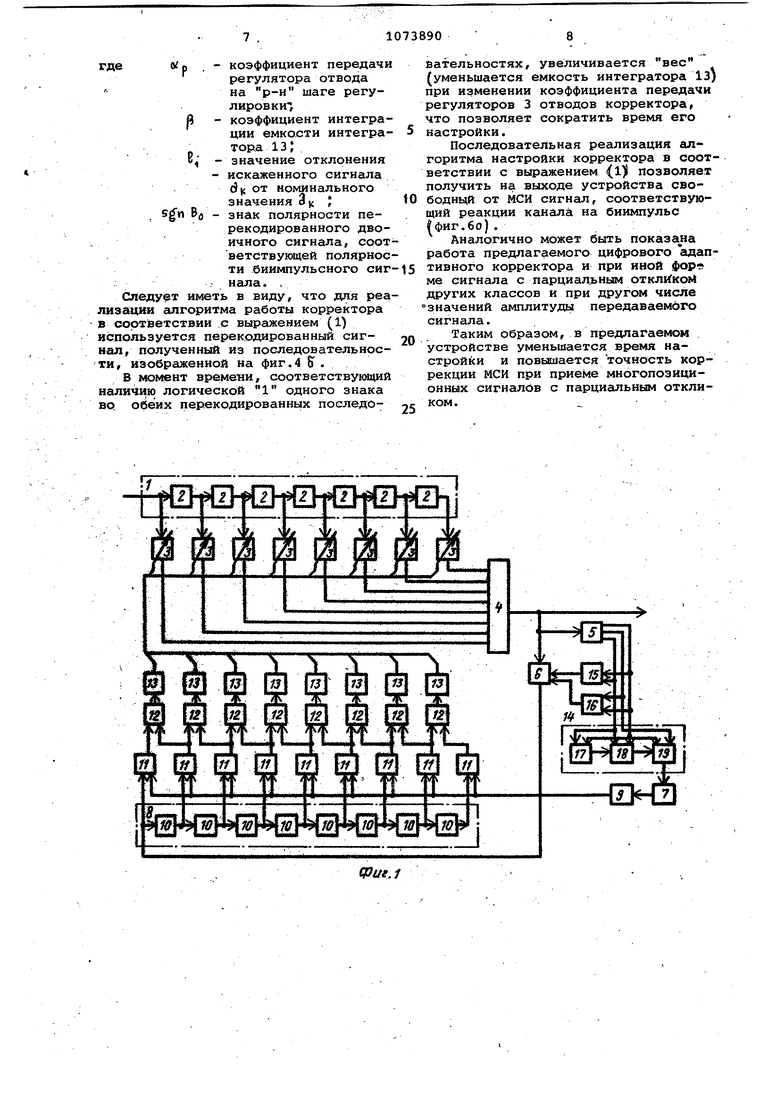

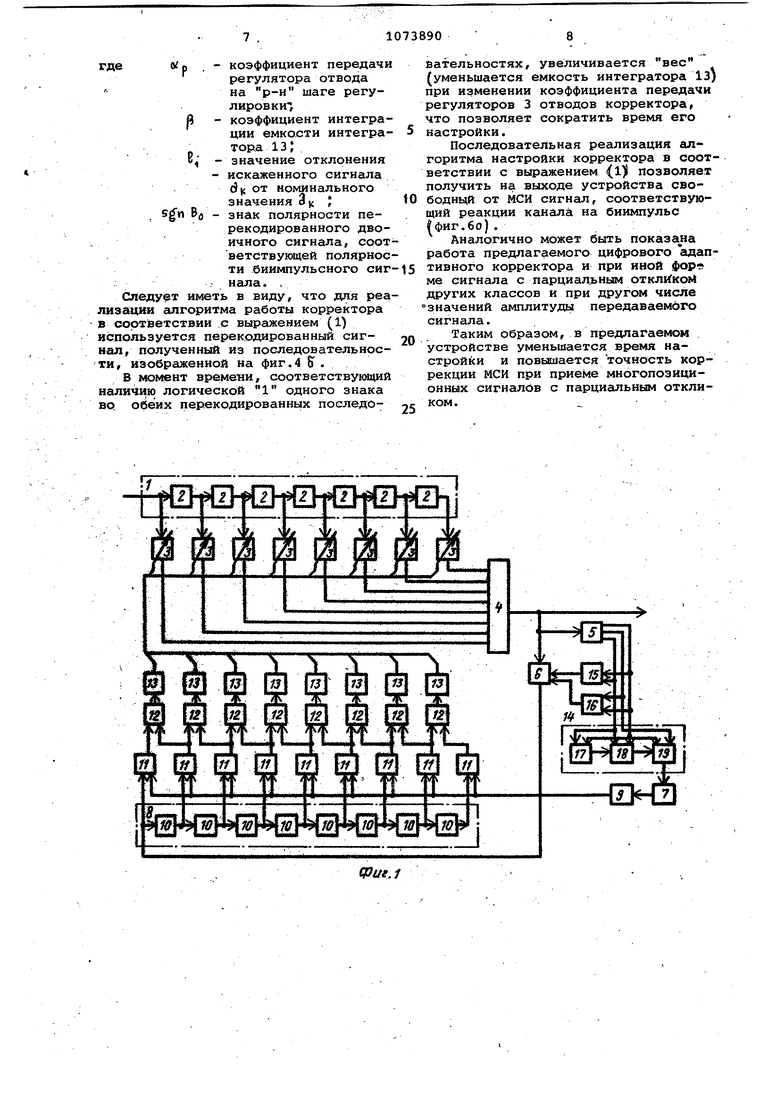

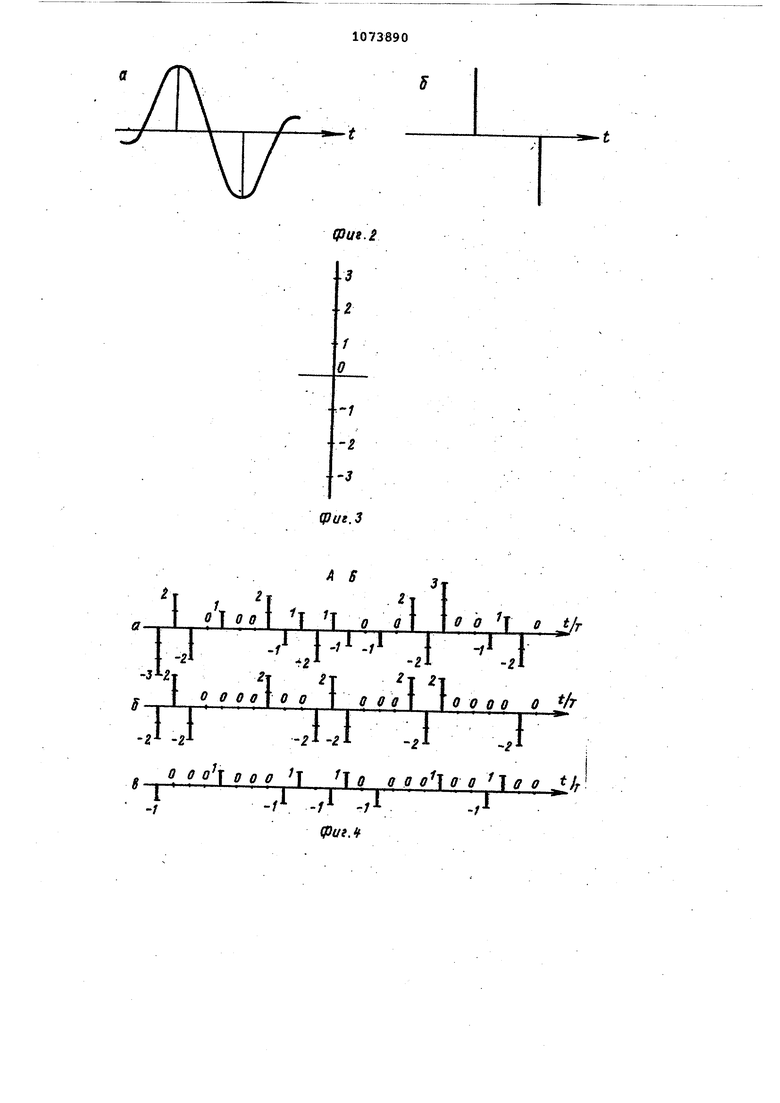

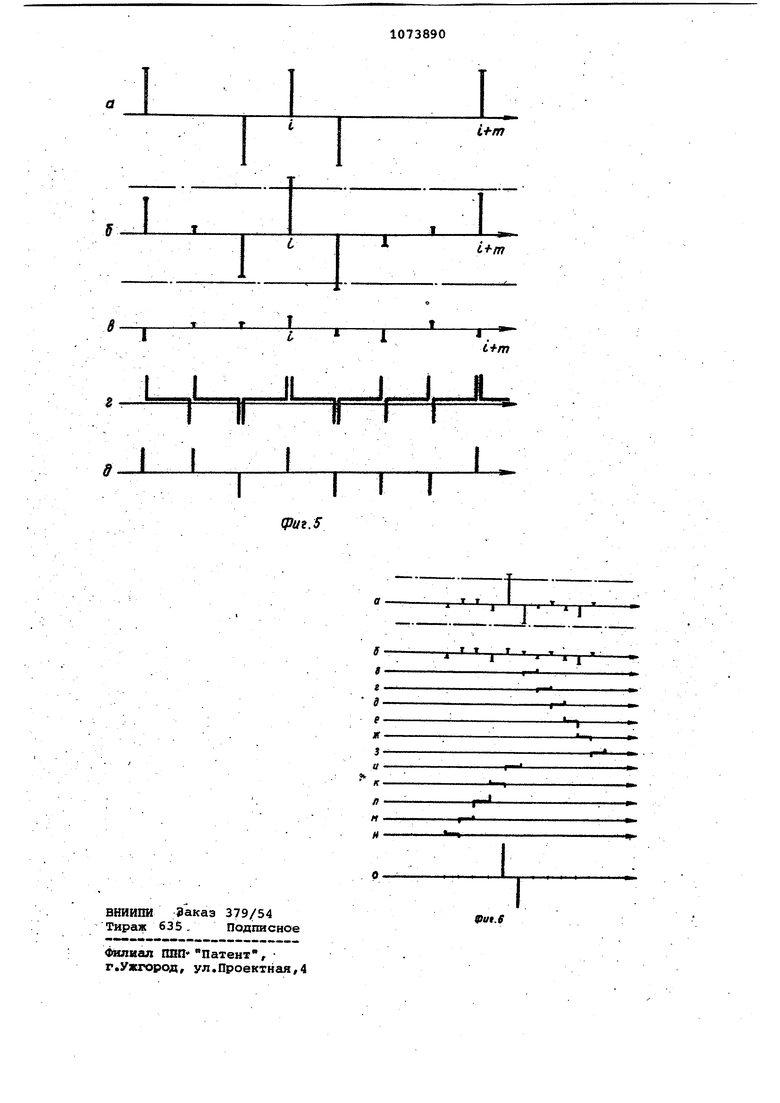

На фиг.1 приведена структурная электрическая схема предлагаемого устройства; на фиг.2 - вид биимпульного видеосигнала; на фиг.3 - относительные величины принимаемого биимпульсного сигнала; на фиг.4-6 временные диаграммы работы устройства.

Цифровой .адаптивный: корректор сигнала с парциальным откликом содежит первую Г) -элементную линию 1 задержки, элемент 2 первой линии задержки, регулятор 3, основной сумматор 4, цифровой блок 5 анализа, блок б вычитания, блок 7 перекодирования биимпульсного сигнала, вторую ц элементную линию 8 задержки третью линию 9 задержки, элемент 10 второй линии задержки, коррелятор 1 дополнительный сумматор 12, интегратор 13, распределитель 14-, первый элемент ИЛИ 15, второй элемент ИЛИ 16, элемент 17 памяти, блок 18 сравнения, вспомогательный сумматор 19.

Цифровой адаптивный корректор с парциальным откликом работает следущим Образом.

Рассмотрение принципа работы устройства ведется на примере биимпульсного видеосигнала второго класа, вид которого и отсчетные значения приведены на фиг, 2Q и 2 К соот- ветственно. Однако указанный принцип работы устройства распространяется и на адаптивную коррекцию МСИ в сигнсшах с парциальным откликом других классов. IБиймпульсный дрмодулированный сигнал на вход корректора и далее на многоразрядную.цифровую первую И -элементную линию 1 задержки, состоящую из элементов 2. Отводы первой ц элементной линии 1 задержки через регуляторы 3 подключены к основному сумматору 4, выход которого является выходом корректора. Кроме того, откорректированный сигнал d ц с выхода основного сумматора 4 поступает, во-первых, на цифровой блок 5 анализа, а во-вторых, на один из входов блока б вычитания.

Повышение скорости передачи сигИсшов данных может производится за счет увеличения числа позиций амплитуды передаваемого сигнала. Допустим, что принимаемый биимпульсный сигнал имеет семь значений амплитуды, относительные величины которой 1ФИГ.З) обозначены цифрами н-3,+2,1,0, -1,-2,-3. Число позиций си 1плитуды биимпульсного сигнала .может быть и другим.

В цифровом блоке 5 анализа осуществляется оценка амплитуды сигнала на выходе основного сумматора 4. На основании этой оценки в цифровом блоке 5 анализа вырабатывается эталонный одноразрядный двоичный сигнал по соответствующей цепи. По этому сигналу в элементах ИЛИ 15 и 16 формруется соответству 5{цая ему 6 -разрядная, комбинация d , причем число разрядов С равно числу разрядов кодовой комбинации, записанной в линии 1 задержки. В блоке б вычитания осуществляется формирование Е -разрядного сигнала ошибки б t , получающегося как разность выходного .с) и эталонного d сигнала, поступающего на блок 6 вычитания от элементов ИЛИ 15 и 16. Сигнал ошибки бк от блока б вычитания подается на вход второй(цtк)-элементной линии 8 задержки, состоящей из. элементов 10, отводы которой связаны со входами корреляторов 11. На вторые входы корреляторов 11 поступает перекодированный и задержанный сигнал с выхода третьей линии 9 задержки, задерживающей сигнал на время, равное половине задержки во второй(мч кJ -элементной линии Зсщержки.

Возможные относительные значения модуля амплитуды откорректированного сигнала в соответствии с фиг.З равны 0,,3. Эти значения можно представить в виде многоразрядных двоичных чисел следующим образом: относительному значению амплитуды 1 соответствует такое, например девятиразрядное число О 01000000, значению 2 соответствует .010000000, значению 3 соответствует 011000000. Сранивая эти кодовые числа, видно, что единица во втором разряде появляется при наличии относительных значений 2 или 3, а .единица в третьем разряде - при наличии относительных 1 или 3. Рассмотренный принцип реализует первый и второй элемент ИЛИ 15 и 16. Причем на..выходе первого элемента ИЛИ 15 формируется логический сигнал в третьем разряде, на выходе второго элемента ИЛИ 16 формируется Логический сигнал во втором разряде -разрядного кодового числа. По остальным разрядам В -разрядного числа о к формируется логический ноль. Таким образом, введение двух элементов и 16 позволяет осуществить преобразование одноразрядной двоичной последовательности в многоразрядную С -разрядную двоичную последовательность d к .

Допустим, что идеальный неискаженный сигнал d t , поступающий с выхода основного сумматора 4,имеет вид,изображенный на фиг.4 а . В распределителе 14 эта последовательность распределяется на две трвхпозиционнв последовательности сигналов, изображенные на фиг.4 Sif Ь Из фиг.4 еле дует, что одна Из последовательностей (фИг.4&У состоит из сигналов с относительным значением амплитуды равным 12 и О, а другая (фиг. из сигналов с отйосительным значением амплитуда, равным +1 и 0. При чем, поскольку передаются биимпульс ные сигналы, то в последовательностях изображённых на фиг.4Ё1 , в полярность сигналов должна чередоваться. Поэтому сигнгш с относительным значением +1 в точке А на фиг.4 а представляется суммой двух сигналов +2 и -1 (фиг.46) АНсШогично сигнал -1 в точке Б представляется суммой двух сигналов -2 и 41 (фиг.4б,)) . Следовательно, для того, чтобы правильно разделить исходную последователь ность на две, необходимо помнить полярность последнего сигнала с относительной амплитудой, равной 1. Поэтому в распределителе должен ыть элемент 1 памяти, осуществляйзщий запоминание сигналов с относительным значением амплитуды -tS и 1, поступающих с выхода цифрового блока 5 анализа. Кроме того, в соетав распределителя 14 входит блок 1 сравнения, осуществляющий сравнение полярностей сигналов с относи тельной амплитудой +i на выходе элемента 17 памяти и Непосредственно на выходе цифрового блока 5 анализа. В случае, если эти полйрности совпадают, то сигнал с относительной амплитудой Ut представляется в виде суммы двух сигналов: с амплитудой |2| и 11|, как напри- мер, это изображено на фиг.4 (точки А и в) . Такое представление осуществляется в вспомогательном сумматоре 19, где к двум последователь ностям с амплитудами +2 и О, а также. ±1 и О добавляетсярезультат ана лиза,производимого в блоке 18сравнеВИЯ. Две последовательности (фиг.4б с выхода вспомогательного сумматора 19 поступают в блок 7 перекодиро вания биимпульсного сигнала, где ка дая из них подвергается операции перекодирования, суть которой состо ит в следующем. ТрехпозИционный неи каженный сигнал, поступающий на вхо блока 7 перекодирования биимпульсного сигнала из распределителя 14, имеет вид, изображенный на фиг.Зск Под действием МСИ этот сигнал искажается .(фиг.5 5) . Полученные искажения характеризуются сигналом ошибки (фиг.5 6) , сформированным как разность сигналов по фи.г. 5 q и 5 полученных из исходного секй1позиционного сигнала 6ц, на выходе основного сумматора 4. Блок 7 перекодирования биимпульсного сигнала предназначен для формирования двоичного сигнала, каждый импульс которого соответстует условной поляр ности биимпульса, в, качестве , . которого используют любую из Трехпозиционных последовательностей, изображенных на фиг.48,& , ко торые в сумме дают исходный сигнал, изображенный на фиг.4 а| . Одна из этих последовательностей, в предложении отсутствия ошибок, изображена на фиг.5 а . Условное разбиение сигнала на фиг.5 а на биимпульсы представлено на фиг.З- , а на фиг.5 9 приведён формируемый блоком 7 перекодирования биимпульсного сигнала двоичный сигнал, соответствующий полярности биимпульсов (фиг.Бг) . Применительно к трехпозиционному.сигналу принцип работы блока 7 перекодирования биимпульсного сигнала состоит в размещении на местах нулей исходного трехпозиционного сигнала значений, соответствующих полярности предшествующего актив ного значения сигнала. Перекодирова«ный таким образом сигнал, используемый в процессе корреляционного анализа в корреляторах 11, позволяет определить импульсную реакцию канала на воздействие в виде биимпульса, что полностью соответствует структуре корректируемого сигнала. Процесс коррекции поясняет фиг.б. На фиг. б а изобр ен искаженный элементарный биимпульс на выходе распределителя 14. На фиг.68 соответствующий ему сигнал отклонений импульсной реакции от идеального значения, имеющий место на выходах корреляторов 11. Определяемое посредством дополнительных сумматоров 12 неравенство соответствующих значениям по фиг. б после интегрирования в интеграторах 13. приводит к изменению коэффициентов передачи регуляторов 3,: таким образом, чтобы задержанный посредством первой И -элементной линии 1 задержки основной биимпульс (фиг.бЬ -бн) скомпенсировал обнаруженное отклонение. Таким образом, алгсфитм работы корректора при компенсации МСИ о сигналах с парциальным откликом клас-. са 2 описывается следующим выражением, аналогично можно записать выражение для алгоритма коррекции МСИ в Сигналах .спарциальнымооткликом дру- . гйх классов , (i) )

где ei р , - коэффициент передачи

Р регулятора отвода на р-н шаге регулировки,

Р коэффициент интеграции емкости интегратора 13 ;

В: значение отклонения - искаженного сигнала йц от номинального значения 3ц J

sg BO - знак полярности перекодированного двоичного сигнала, соответствующей полярности биимпульсного сиг. нала. ,

Следует иметь в виду, что для реализаиши алгоритма работы корректора в сортйетствии с выражением (1) используется перекодированный сигнал, полученный из последовательности, изображенной на фиг,4 &.

В момент времени, соответствуимдий наличию логической 1 одного знака во. обеих перекодированных последовательностях, увеличивается вес (уменьшается емкость интегратора 13) при изменении коэффициента передачи регуляторов 3 отводов корректора, что позволяет сократить время его настройки.

Последовательная реализация Шгоритма настройки корректора в соответствии с выражением (1) позволяет получить на выходе устройства сво0бодньцй от МСИ сигнал, соответствующий реакции канала на биимпульс (фиг.бо).

Аналогично может быть показана работа предлагаемого цифрового адап5 тивного корректора и при иной фар-п ме сигнала с парциальным откликом других классов и при другом числе -значений амплитуды передаваемдго сигнала.

Таким образом, в предлагаем 1

0 устройстве уменьшается время настройки и повышается точность коррекции МСИ при приеме многопоэиционных сигналив с парциальным отклид ком.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с парциальным откликом | 1983 |

|

SU1117855A1 |

| Адаптивный корректор межсимвольных искажений сигнала | 1978 |

|

SU936441A1 |

| Взаимно-базисный корректор | 1986 |

|

SU1403382A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Устройство для передачи и приема цифровых сигналов | 1986 |

|

SU1415452A1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 2014 |

|

RU2584456C2 |

| Цифровой адаптивный корректор межсимвольной интерференции | 1982 |

|

SU1083374A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Устройство синхронизации приемника многопозиционных сигналов | 1984 |

|

SU1288924A1 |

-#

(pui.2 .3 Q ff 0 T 0 J/r

., l-/r:;r J I

p

1

..y.... j

.I -2 -fl-fl-fl.I

, 0 0 o 0 0 0 } f1 0 00 o IT

i

.,y -/Г .71

-/

(Of/.

jj

:д

I I

t II I . I

II I I

(Риг.5

Т r

J

-1

J

Т т . Т.

г i I

-г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3508153, ;КЛ; 325-42, 1970. | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Адаптивный корректор межсимвольных искажений сигнала | 1978 |

|

SU936441A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-15—Публикация

1982-04-02—Подача