Изобретение относится к области вычислительной техники и может найти применение при создании высокоточных систем переработки цифровой информации. Известны способ и устройство округления 1 результата элементарной операции-(сложение, сдвиг, умножение, деление), содержащее регистр результата с дополнительными разрядами для округления. При выполнении операции округления производят отбрасывания дополнительных разрядов. Недостаток этого устройства состоит в том, что независимо от своей величины ошибка округления всегда имеет один и тот же знак, противоположный знаку округляемого операнда, что приводит к быстрому накапливанию ошибки вычислений. Наиболее близким к данному изобретению является устройство для округления числа 2, содержащее регистр результата с дополнительными разрядами для округления, шину тактовых сигналов и элемент И. При выполнении операции округления анализируют сигналы старшего дополнительного разряда регистра результата, формируют единичный сигнал округления, при единичном значении старшего дополнительного разряда регистра результата и добавляют его в младший разряд регистра результата. Недостаток этого устройства заключается в том, что при выполнении последовательности операций округления в ошибке округления появляется систематическое смещение. Систематическое смешение ошибки объясняется тем, что оишбка округления результата элементарной операции, равная половине младшего разряда результата, оставшегося после отбрасывания младших разрядов результата, не может быть скомпенсирована, а это ведет к неоправданно; большому росту общей ошибки вышслений. Целью изобретения является повышение точности вычислений путем устранения систематического смешения в общей ошибке вычислений. Цель достигается тем, что в устройство для округления числа, содержащего регистр результата с дополнительными разрядами для округления, шину тактовых сигналов и элемент И, первый вход .которого подключен к шине тактовых сигналов, введены два элемента ИЛИ, два

дополнительных элемента И, триггер со счетным входом, причем входы первого элемента ИЛИ подключены к выходам всех дополнительных разрядов регистра результата, исключая старший догголнительный разряд, выход первого элемента ИЛИ соединен с инверсным входом первого дополнительного элемента Икс лервьЕМ входом второго дополнительного элемента И, старший дополнительный разряд соединен с прямым входом первого дополнительного элемента И и со вторым входом второго дополнительного зле-мента И, третий вход которого соединен с шиной тактовых сигналов, выход первого дополнительного элемента И соединен со вторым входом элемента И и со счетным входом триггера, выход которого соединен с третьим входом элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго дополнительного элемента И,, а выход второго элемента ИЛИ подключен к младшему разряду регистра результата.

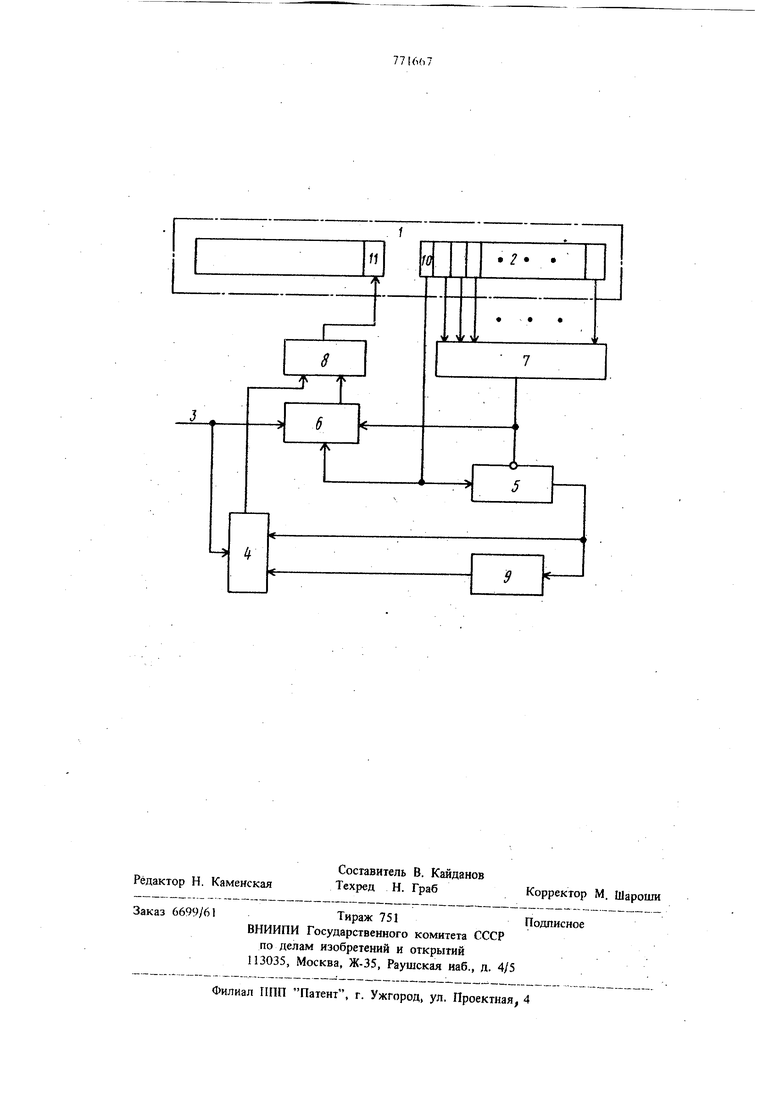

Структурная схема устройства приведена на чертеже.

Устройство содержит регистр результата 1 с дополнительными разрядами 2 для округлейия, шину тактовых сигналов 3, элемент И 4, два дополнительных элемента И 5, 6, два эле-мента ИЛИ 7, 8, триггер 9 со счетным входом. При этом входы элемента ИЛИ 7 подключены к выходам всех дополнительных разрядов 2 регистра результата 1, исключая старший разряд а выход элемента ИЛИ 7 соединен с инверсным входом элемента И 5 и с входом элемента И 6 второй вход элемента; И 6 подключен к старшему дополнительному разряду 10 регистра 1 и к прямому входу элемента И 5, а выход элемента И 6 соединен со входом элемента ИЛИ 8, другой вход которого подключен к выходу элемента И 4, входь которого соединены с единичным выходом и со счетным входом триггера 9, счетный вход триггера 9 соединен с выходом элемента И 5, выход элемента ИЛИ 8 подключен к младшему разряду 11 регистра результата 1, шина тактовых сигналов 3 подключена к третьему входу элементов ИЛИ. Устройство работает следующим образом. Пусть в результате выполнения последовательибсти операций сложения, в регистре результата 1 получилась следующая последовательность двоичных кодов Xj. Пусть после первого сложения в регистре результата 1 и дополнительных разрядов 2 находится код

X, О, 001 011 ; 111.В этом случае по сигналу с шины тактовых сигналов 3 на выходе элемента И 6 возникает единичный сигнал, так как на его первый вход поступает единичный сигнал со старшего 10 дополнительно о разряда регистра 1, и на второй

вход также поступает единичный си1пал с выхода элемента ИЛИ 7, так как в допо;шительных разрядах содержатся единицы, а на выходе элемента И 4 единичный сигнал будет отсутствовать, так как на его вход (независимо от состояния триггера 9) с выхода элемента И 5 не поступает единичный сигнал, потому что на его инверсном входе не нулевой сигнал.

По единичному сигналу с элемента И 6 на выходе элемента ИЛИ 8 будет сформирован единичный сигнал округления, поступающий на младший разряд 11 регистра результата 1.

Таким образом, в регистре результата для нашего примепа ПОЛУЧИМ совокупность сигнало представляющих код Xj 0,001100. Ошибка округления равна ДХ1 + 0,000 000 001.

Суммируя этот код с кодом следующего слагаемого получим совокупность сигналов, представляющих код Х2 О, 000 010 f 010. Для этого кода сигнал округления не формируется, так как на единичные входы элементов И 6, И 5 со старшего дополнительного разряда 10 поступает нулевой сигнал. Результат округления будет равен ДХ О, 000 010, а ошибка округления ДХ2 - 0,000 000 010.

Суммируя этот код с кодом следующего слагаемого, получим совокупность сигналов, представляющих код Хз О, 000 111 / 100. Для этого кода по сигналу с шины тактовых сигналов 3 на выходе элемента И 4 возникает единичный сигнал, так как на его первый вход с триггера 9 поступает единичный сигнал (делаем допущение, что в исходном состоянии триггер 9 находится в единичном состоянии), и на второй вход так же поступает единичный сигнал с выхода элемента И 5, который возникает, потому что на его инверсном вхоДе находится нулевой сигнал с элемента ИЛИ 7 и на прямом входе имеется единичный сигнал со старшего дополнительного -10 разряда. На выходе элемента И б единичный сигнал отсутствует, так как не его второй вход поступает нулевой сигнал с элемента ИЛИ 7. По единичному сигналу с выхода элемента И 5, поступающему на счетный вход триггера 9, триггер будет переведен в нулевое состояние.

Таким образом, по единичному сигналу с элемента И 4 на выходе Элемента ИЛИ 8 будет сформирован единичный сигнал округления поступающий на младший разряд 11 регистра результата 1.

Результат округления будет равен Хз О, 001 000, а ошибка округления АХз + О, 000 000 100..

Суммируя этот код с кодом следующего слагаемого, получим совокупность сигналов, представляемих код Х4 О ,001 100 100.

Для этого кода сигнал округления не формируется, так как на второй вход элемента И 6 с выхода элемента ИЛИ 7 поступает нулево сигнал и на первый вход с выхода триггера 9 также поступает нулевой сигнал, потому что триггер на предыдущем такте округления был переведен в нулевое состояние. Результат округления будет равен Х4 О, 001 100, а оши ка округления равна ДХ4 - О, 000 000 100 Рассуждая аналогично, запишем результаты округления и значения ошибок для последовательностиХ; О, 000 110. 100; Хб О, 001 ПО 110; Х7 О, 000 111 100; Xg О, 000 001 011; Х; О, 000 111; х; о, 001 111; Х О, 000 111; О, 000 001; 5 + 0,000000 100; AXs + 0,000 000 010; Д XT -0,000 000 100; ДХа -0,000000011. Суммарная абсолютная ошибка приведенного примера - Д д К ., составит величину Ду -0,000 000 010. При работе же прототипа при вьшолнении это последовательности операдий приведенного примера суммарная абсолютная ошибка округления составит величину Ду| + 0,000 001 110, т.е. ; суммарная абсолютная ошибка в этом случае значительно больше. Это объясняется тем, что у ошибок округления (ДХз, ДХ4, ДХ5, ДХ7) происходит чередо вание знака и поэтому при их сложении происходит компенсация обшей ошибки Ду, а соотве ствующие ошибки при работе прототипа имеют один и тот же знак, поэтому при их сложении происходит накапливание обшей ошибки ДУ. Из описания работы схемы устройства и приведенного примера следует, что использование данного устройства позволяет существенно увеличить точность выичслений (для поиведенного примера в семь раз) по сравнению с прототипом. Формула изобретения Устройство для округления числа, содержащее регистр результата с дополнительными разрядами для округления, шину тактовых сигналов и элемент И, первый вход которого подключен к шине тактовых сигналов, о т л ич а ю щ ее с я тем, что, с целью повышения точности вычисления, в устройство введены два элемента ИЛИ, два дополнительных элемента И, триггер со счетным входом, причем входы первого элемента ИЛИ подключены к выходам всех до-полнительных разрядов регистра результата, исключая старший дополнительный разряд, выход первого элемента ИЛИ соединен с инверсным входом первого дополнительного элемента И с первым входом второго дополнительного элемента И, старший дополнительный разряд соединен с прямым входом первого дополнительного элемента И и со вторым второго дополнительного элемента И, третий вход которого соединен с шиной тактовых сигналов, выход первого дополнительного элемента И соединен со вторым входом элемента И и со счетным входом триггера, выход которого соединен с третьим входом элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которогосоединен с выходол второго дополнительного элемента И, а выход второго элемента ИЛИ подключен к младшему разряду регистра результата. Источники информации, принятые во внимание при экспертизе 1. В. В. Воеводин. Вычислительные основы линейной алгебры, Наука, 1977, с. 16. 2. Ю. П. Журавлев. Системное проектирование управляющих ЦВМ. М., Сов.радио, 1974., с. 165 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Преобразователь кода во временной интервал | 1984 |

|

SU1221756A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

Авторы

Даты

1980-10-15—Публикация

1978-11-09—Подача