Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.

Целью изобретения является упрощение устройства.

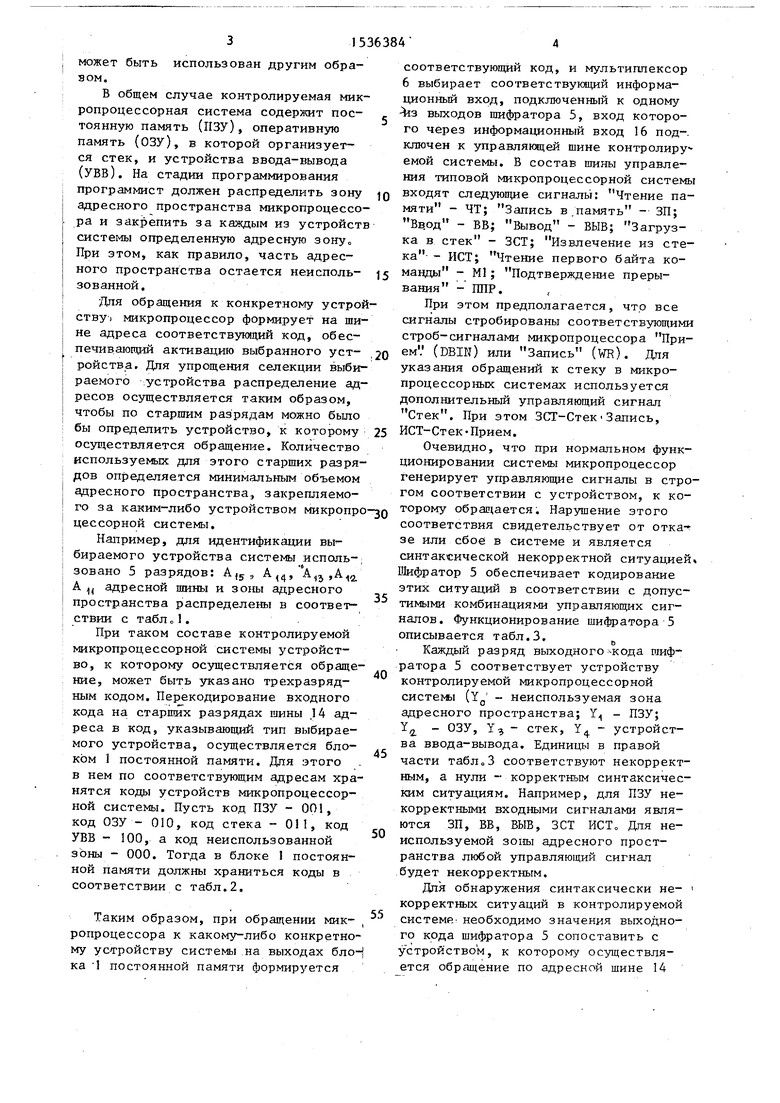

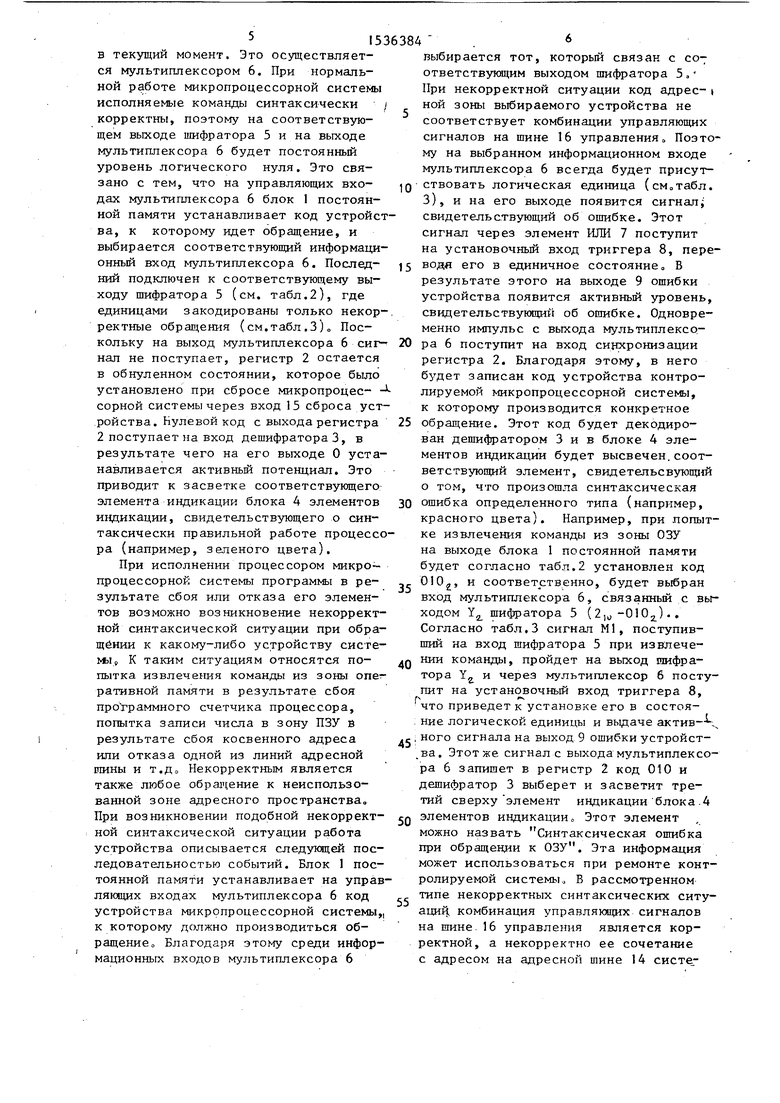

На фиг.1 изображена структурная схема устройства; на фиг.2 - временные диаграммы его работы

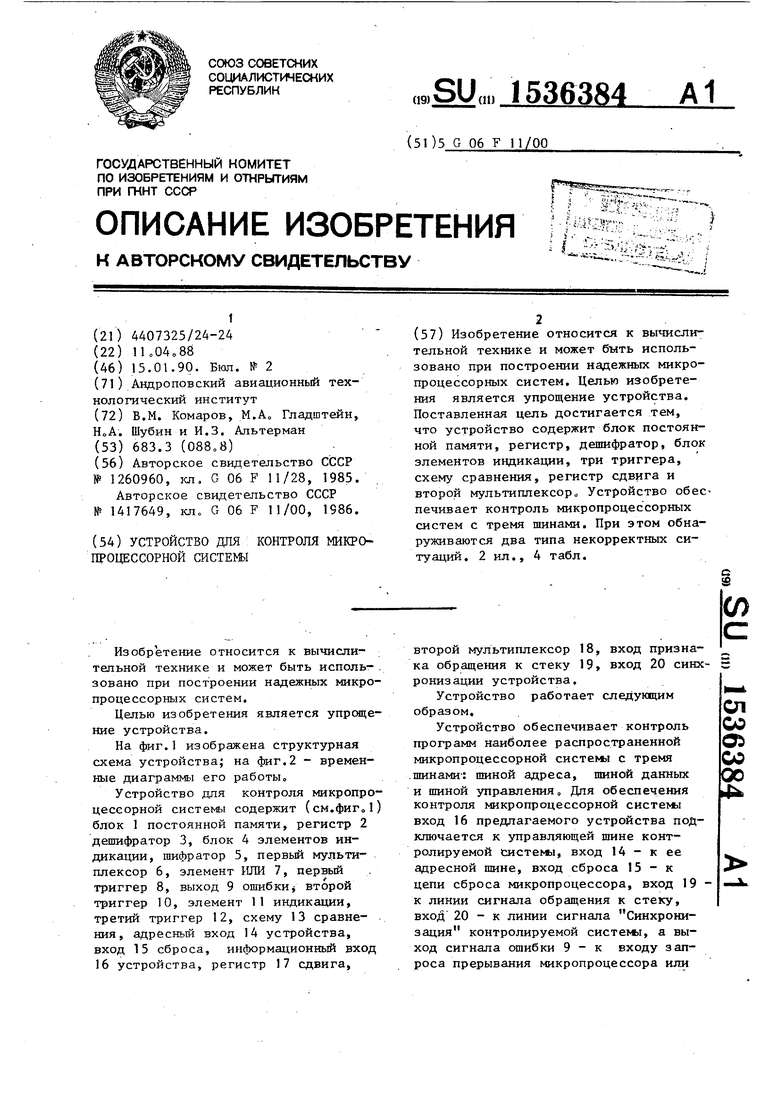

Устройство для контроля микропроцессорной системы содержит (см.фиГо) блок 1 постоянной памяти, регистр 2 дешифратор 3, блок 4 элементов индикации, шифратор 5, первьй мультиплексор 6, элемент ИЛИ 7, первый триггер 8, выход 9 ошибки $ второй триггер 10, элемент 11 индикации, третий триггер 12, схему 13 сравнения, адресный вход 14 устройства, вход 15 сброса, информационный вход 16 устройства, регистр 17 сдвига,

второй мультиплексор 18, вход признака обращения к стеку 19, вход 20 синхронизации устройства.

Устройство работает следующим образом.

Устройство обеспечивает контроль программ наиболее распространенной микропроцессорной системы с тремя шинами-: шиной адреса, шиной данных и шиной управления. Для обеспечения контроля микропроцессорной системы вход 16 предлагаемого устройства подключается к управляющей шине контролируемой системы, вход 14 - к ее адресной шине, вход сброса 15 - к цепи сброса микропроцессора, вход 19 - к линии сигнала обращения к стеку, вхоД 20 - к линии сигнала Синхронизация контролируемой системы, а выход сигнала ошибки 9 - к входу запроса прерывания микропроцессора или

СП

со с&

00

оо

Јъ

может быть использован другим образом.

В общем случае контролируемая микропроцессорная система содержит постоянную память (ПЗУ), оперативную память (ОЗУ), в которой организуется стек, и устройства ввода-вывода (УВВ). На стадии программирования программист должен распределить зону JQ адресного пространства микропроцессора и закрепить за каждым из устройств системы определенную адресную зону При этом, как правило, часть адресного пространства остается неисполь- 15 зованной.

Для обращения к конкретному устройству) микропроцессор формирует на шине адреса соответствующий код, обеспечивающий активацию выбранного уст- 20 ройства. Для упрощения селекции выбираемого устройства распределение адресов осуществляется таким образом, чтобы по старшим разрядам можно было бы определить устройство, к которому 25 осуществляется обращение. Количество используемых для этого старших разрядов определяется минимальным объемом адресного пространства, закрепляемого за каким-либо устройством микропро зо цессорной системы.

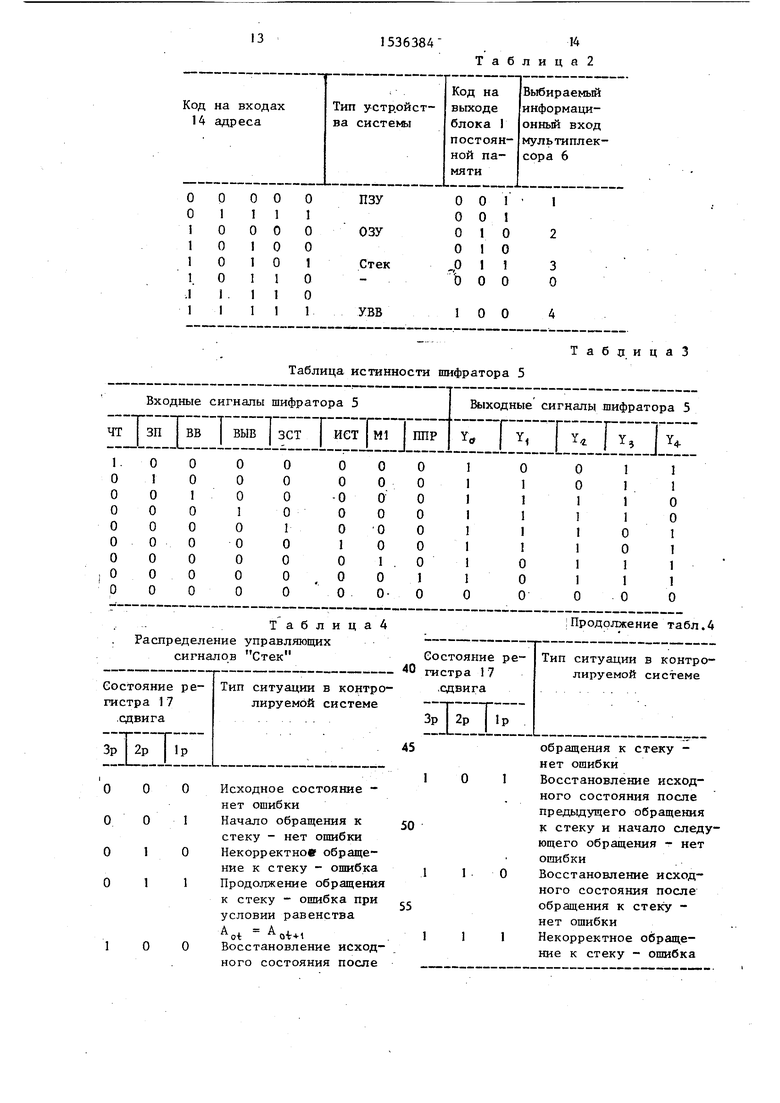

Например, для идентификации выбираемого устройства системы использовано 5 разрядов: А(5 , А и, А,3 ,А1й А 1( адресной шины и зоны адресного пространства распределены в соответствии с табл „ 1.

При таком составе контролируемой микропроцессорной системы устройство, к которому осуществляется обраще- ние, может быть указано трехразрядным кодом. Перекодирование входного кода на старших разрядах шины 14 адреса в код, указывающий тип выбираемого устройства, осуществляется бло- ., ком 1 постоянной памяти. Для этого в нем по соответствующим адресам хранятся коды устройств микропроцессорной системы. Пусть код ПЗУ - 001, код ОЗУ - 010, код стека - 011, код УВВ - 100, а код неиспользованной зоны - 000. Тогда в блоке 1 постоянной памяти должны храниться коды в соответствии с табл.2,

35

50

Таким образом, при обращении мик ропроцессора к какому-либо конкретному ус-тройству системы на выходах бло-) ка 1 постоянной памяти формируется

JQ15

2025 зо

., 35

50

)

55

соответствующий код, и мультиплексор 6 выбирает соответствующий информационный вход, подключенный к одному 4i3 выходов шифратора 5, вход которого через информационный вход 16 подключен к управляющей шине контролирую емой системы. В состав шины управления типовой микропроцессорной системы входят следующие сигналы: Чтение памяти - ЧТ; Запись в память - ЗП; Вв.од - ВВ; Вывод - ВЫВ; Загрузка в стек - ЗСТ; Извлечение из стека - ИСТ; Чтение первого байта команды - Ml; Подтверждение прерывания - imp.

При этом предполагается, что все сигналы стробированы соответствующими строб-сигналами микропроцессора Прием1.1 (DBIN) или Запись (WR). Для указания обращений к стеку в микропроцессорных системах используется дополнительный управляющий сигнал Стек. При этом ЗСТ-СтекЗапись, ИСТ-Стек-Прием.

Очевидно, что при нормальном функционировании системы микропроцессор генерирует управляющие сигналы в строгом соответствии с устройством, к которому обращается. Нарушение этого соответствия свидетельствует от отказе или сбое в системе и является синтаксической некорректной ситуацией Шифратор 5 обеспечивает кодирование этих ситуаций в соответствии с допустимыми комбинациями управляющих сигналов. Функционирование шифратора 5 описывается табл.3, в

Каждый разряд выходного --кода шифратора 5 соответствует устройству контролируемой микропроцессорной системы (Y0 - неиспользуемая зона адресного пространства; Y1 - ПЗУ; У - ОЗУ, Y - стек, Y4 - устройства ввода-вывода. Единицы в правой части табло 3 соответствуют некорректным, а нули - корректным синтаксическим ситуациям. Например, для ПЗУ некорректными входными сигналами являются ЗП, ВВ, ВЫВ, ЗСТ ИСТо Для неиспользуемой зоны адресного пространства любой управляющий сигнал будет некорректным.

Для обнаружения синтаксически не- корректных ситуаций в контролируемой системр необходимо значения выходного кода шифратора 5 сопоставить с устройством, к которому осуществляется обращение по адресной шине 14

в текущий момент. Это осуществляется мультиплексором 6. При нормальной работе микропроцессорной системы исполняемые команды синтаксически i корректны, поэтому на соответствующем выходе шифратора 5 и на выходе мультиплексора 6 будет постоянный уровень логического нуля. Это связано с тем, что на управляющих входах мультиплексора 6 блок 1 постоянной памяти устанавливает код устройства, к которому идет обращение, и выбирается соответствующий информационный вход мультиплексора 6. Последний подключен к соответствующему выходу шифратора 5 (см. табл.2), где единицами закодированы только некорректные обращения (см.табл.3)„ Поскольку на выход мультиплексора б сигнал не поступает, регистр 2 остается в обнуленном состоянии, которое было установлено при сбросе микропроцес- -1 сорной системы через вход 15 сброса устройства. Нулевой код с выхода регистра 2 поступает на вход дешифратора 3, в результате чего на его выходе 0 устанавливается активный потенциал. Это приводит к засветке соответствующего элемента индикации блока 4 элементов индикации, свидетельствующего о синтаксически правильной работе процессора (например, зеленого цвета).

При исполнении процессором микро процессорной системы программы в результате сбоя или отказа его элементов возможно возникновение некорректной синтаксической ситуации при обращении к какому-либо устройству сиетемы „ К таким ситуациям относятся попытка извлечения команды из зоны оперативной памяти в результате сбоя программного счетчика процессора, попытка записи числа в зону ПЗУ в результате сбоя косвенного адреса или отказа одной из линий адресной шины и т.д„ Некорректным является также любое обращение к неиспользованной зоне адресного пространства При возникновении подобной некорректной синтаксической ситуации работа устройства описывается следующей последовательностью событий. Блок 1 постоянной памяти устанавливает на управXQ нии команды, пройдет на выход шифратора Y и через мультиплексор 6 пост пит на установочный вход триггера 8, что приведет к установке его в состояние логической единицы и выдаче актив- ного сигнала на выход 9 ошибки устройст ва. Этот же сигнале выхода мультиплекс ра 6 запишет в регистр 2 код 010 и дешифратор 3 выберет и засветит третий сверху элемент индикации блока элементов индикации„ Этот элемент можно назвать Синтаксическая ошибка при обращении к ОЗУ. Эта информация может использоваться при ремонте кон ролируемой системы, В рассмотренном типе некорректных синтаксических сит

ляющих входах мультиплексора 6 код ,-с

устройства микропроцессорной системы,, аций, комбинация управляющих сигналов к которому должно производиться обращение,, Благодаря этому среди информационных входов мультиплексора 6

на шине 16 управления является корректной, а некорректно ее сочетание с адресом на адресной шине 14 систе выбирается тот, который связан с соответствующим выходом шифратора 5, При некорректной ситуации код адрес-t ной зоны выбираемого устройства не соответствует комбинации управляющих сигналов на шине 16 управления0 Поэтому на выбранном информационном входе мультиплексора 6 всегда будет присутствовать логическая единица (см„табл. 3), и на его выходе появится сигнал, свидетельствующий об ошибке. Этот сигнал через элемент ИЛИ 7 поступит на установочный вход триггера 8, пере5 водя его в единичное состояние„ В результате этого на выходе 9 ошибки устройства появится активный уровень, свидетельствующий об ошибке. Одновременно импульс с выхода мультиплексо0 ра 6 поступит на вход синхронизации регистра 2. Благодаря этому, в него будет записан код устройства контролируемой микропроцессорной системы, к которому производится конкретное

5 обращение. Этот код будет декодирован дешифратором 3 и в блоке 4 элементов индикации будет высвечен.соответствующий элемент, свидетельсвующий о том, что произошла синтаксическая

0 ошибка определенного типа (например, красного цвета). Например, при попытке извлечения команды из зоны ОЗУ на выходе блока 1 постоянной памяти будет согласно табл.2 установлен код

010г, и соответственно, будет выбран вход мультиплексора 6, связанный с выходом Yg шифратора 5 ( 210 -01Ог).. Согласно табл.З сигнал Ml, поступивший на вход шифратора 5 при извлечеQ нии команды, пройдет на выход шифратора Y и через мультиплексор 6 поступит на установочный вход триггера 8, что приведет к установке его в состояние логической единицы и выдаче актив-Ч ного сигнала на выход 9 ошибки устройства. Этот же сигнале выхода мультиплексора 6 запишет в регистр 2 код 010 и дешифратор 3 выберет и засветит третий сверху элемент индикации блока 4 элементов индикации„ Этот элемент можно назвать Синтаксическая ошибка при обращении к ОЗУ. Эта информация может использоваться при ремонте контролируемой системы, В рассмотренном типе некорректных синтаксических ситуГ.

5

0

с

аций, комбинация управляющих сигналов

на шине 16 управления является корректной, а некорректно ее сочетание с адресом на адресной шине 14 систе 7153

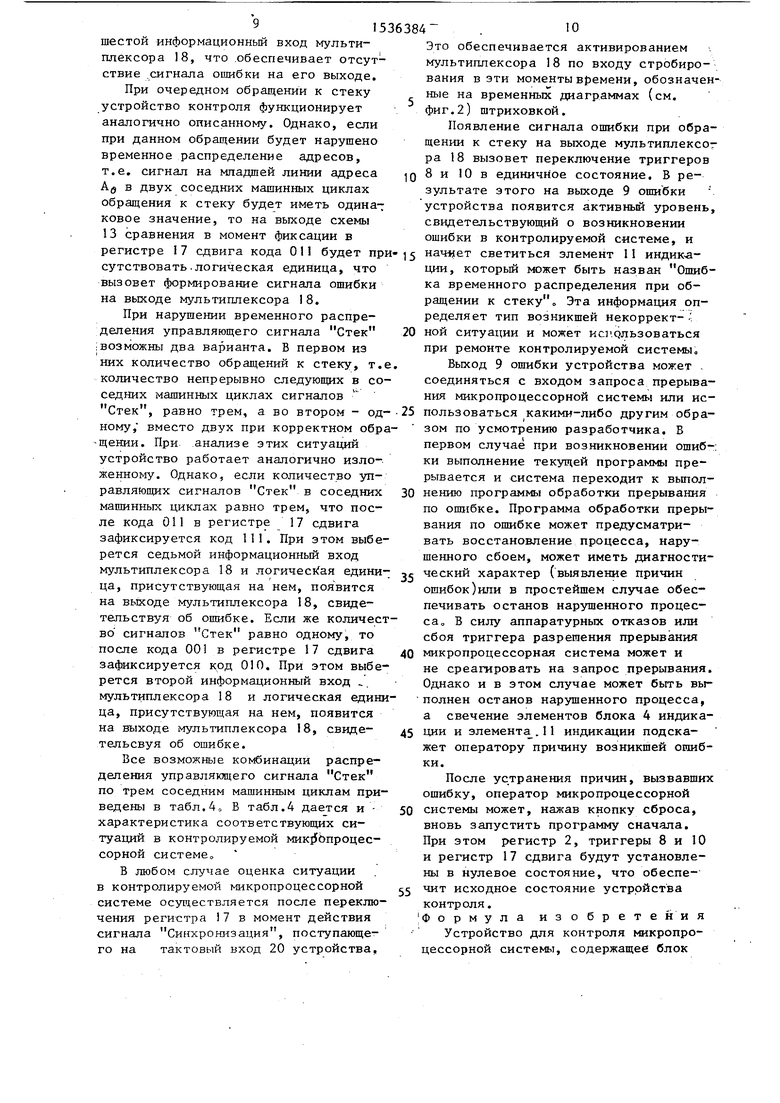

мы. Однако, кроме подобных некорректных ситуаций, часто в результате отказов или сбоев возникают некорректные синтаксические ситуации, связанные с нарушением временного распределения управляющих сигналов и адресов при обращении к стеку, что нарушает нормальное функционирование микропроцессорной системы При нормаль- ном функционировании в микропроцессорных системах (например, на базе микропроцессора КР580ИК80А) обращение к стеку всегда осуществляется в двух соседних машинных циклах работы процессора, в каждом из которых часть необходимой информации записывается (считывается) в (из) соседние ячейки стека,, Следовательно, управляющий сигнал Стек, указывающий на обра- щение к стеку в текущем цикле, должен следоватеь в двух соседних машинных циклах, а адрес на адресной шине в этих циклах не должен отличаться более чем на 1, т.е„ быть четным в одном цикле и нечетным в другом или наоборот. Нарушение этого распределения (сигнала Стек или адресов) приведет к тому, что в стек будет записана (считана) лишь часть необходимой информации либо записана (считана) вся информация, но по неправильным адресам. В результате нормальное функционирование микропроцессорной системы будет нарушено, Последствия этого нарушения могут быть очень значительны, так как в стеке чаще всего хранится управляющая информация (адреса возвратов) и неправильное обращение к стеку вызовет непредсказуе- мое исполнение программы

Для обнаружения подобных некорректных ситуаций текущее значение сигнала Стек, поступающего на вход 19, в начале каждого машинного цикла рабо ты процессора фиксируется в регистре 17 сдвига Запись- этого сигнала в регистр 17 осуществляется сигналом Синхронизация, поступающим на вход 20 устройства и обозначающим начало каждого машинного цикла. Например, в микропроцессорной системе на базе микропроцессора КР580ИК80А управляющий сигнал Стек в режиме временного мультиплексирования устанавливает- ся на шине данных, а сигнал Синхро- низация формируется генератором тактовых импульсов КР580ГФ24. При следовании нулевых значений сигнала

8

Стек регистр 17 сдвига находится в исходном нулевом состоянии, уста- новленном при сбросе микропроцессорной системы через вход 15 сброса устройства, В результате этого среди информационных входов мультиплексора 18 выбирается нулевой вход и обеспечивается нулевой уровень сигнала на выходе мультиплексора 18, что свидетельствует об отсутствии ошибки при обращении к стеку.

В этом состоянии устройство находится до появления первого единичного значения сигнала Стек, т.е. до начала обращения к стеку. При появлении первого единичного значения сигнала Стек первый разряд регистра 17 сдвига переходит в единичное состояние и по фронту его выходного сигнала в триггере 12 запоминается текущее значение младшей линии А0 адресной шины контролируемой системы. При этом в регистре 17 сдвига фиксируется код 001 и выбирается первый информационный вход мультиплексора 18, что обеспечивает отсутствие сигнала ошибки на его выходе.

При нормальном функционировании контролируемой микропроцессорной системы в следующем машинном цикле вновь должен появиться- сигнал Стек, а адрес должен измениться с четного на нечетный или наоборот. Поэтому при переходе к очередному циклу в момент смены адреса значение сигнала на линии Ав изменяется, и схема 13 сравнения формирует на своем выходе, нулевое значение сигнала, свидетельствующее о несовпадении состояния триггера 12, т.е. адреса в предыдущем машинном цикле, с адресом в текущем цикле. При этом в регистре 17 сдвига фиксируется код 011 и выбирается третий информационный вход мультиплексора 18. При нулевом значении сигнала на выходе схемы 13 сравнения сиг-s нал ошибки на выходе мультиплексора 18 не формируется. Далее проверяется условие нормального функционирования контролируемой системы в третьем от начала обращения к стеку машинном цикле. При корректном обращении к стеку значение сигнала Стек в этом цикле должно быть равно нулю. Если это условие выполняется, то в регистре 17 сдвига в третьем от начала обращения к стеку машинном цикле фиксируется код 110. При этом выбирается

шестой информационный вход мультиплексора 18, что обеспечивает отсутствие сигнала ошибки на его выходе. При очередном обращении к стеку устройство контроля функционирует аналогично описанному. Однако, если при данном обращении будет нарушено временное распределение адресов, т.е. сигнал на младшей линии адреса А0 в двух соседних машинных циклах обращения к стеку будет иметь одинаковое значение, то на выходе схемы 13 сравнения в момент фиксации в

20

30

35

регистре 17 сдвига кода 011 будет нач«ет светиться элемент 11 индика- сутствовать логическая единица, что вызовет формирование сигнала ошибки на выходе мультиплексора 18.

При нарушении временного распределения управляющего сигнала Стек возможны два варианта. В первом из них количество обращений к стеку, т.е. количество непрерывно следующих в соседних машинных циклах сигналов Стек, равно трем, а во втором - одному; вместо двух при корректном обращении. При анализе этих ситуаций устройство работает аналогично изложенному. Однако, если количество управляющих сигналов Стек в соседних машинных циклах равно трем, что после кода 011 в регистре 17 сдвига зафиксируется код 111. При этом выберется седьмой информационный вход мультиплексора 18 и логическая единица, присутствующая на нем, появится на выходе мультиплексора 18, свидетельствуя об ошибке. Если же количество сигналов Стек равно одному, то после кода 001 в регистре 17 сдвига до зафиксируется код 010. При этом выберется второй информационный вход .. мультиплексора 18 и логическая единица, присутствующая на нем, появится на выходе мультиплексора 18, свиде- тельсвуя об ошибке.

Все возможные комбинации распределения управляющего сигнала Стек по трем соседним машинным циклам приведены в табл.4о В табл.4 дается и характеристика соответствующих ситуаций в контролируемой микропроцессорной системе

В любом случае оценка ситуации в контролируемой микропроцессорной системе осуществляется после переключения регистра 17 в момент действия сигнала Синхронизация, поступающего на тактовый вход 20 устройства.

ции, который может быть назван Ошиб ка временного распределения при обращении к стеку. Эта информация определяет тип возникшей некорректной ситуации и может использоваться при ремонте контролируемой системы. Выход 9 ошибки устройства может соединяться с входом запроса прерыва ния микропроцессорной системы или ис

25 пользоваться какими-либо другим обра зом по усмотрению разработчика. В первом случае при возникновении ошиб ки выполнение текущей программы прерывается и система переходит к выпол нению программы обработки прерывания по ошибке. Программа обработки преры вания по ошибке может предусматривать восстановление процесса, нарушенного сбоем, может иметь диагности ческий характер (выявление причин ошибок)или в простейшем случае обеспечивать останов нарушенного процесса, В силу аппаратурных отказов или сбоя триггера разрешения прерывания микропроцессорная система может и не среагировать на запрос прерывания Однако и в этом случае может быть вы полнен останов нарушенного процесса, а свечение элементов блока 4 индика ции и элемента. 11 индикации подскажет оператору причину возникшей ошиб ки.

После устранения причин, вызвавши ошибку, оператор микропроцессорной системы может, нажав кнопку сброса, вновь запустить программу сначала. При этом регистр 2, триггеры 8 и 10 и регистр 17 сдвига будут установлены в нулевое состояние, что обеспе55 чит исходное состояние устройства контроля. Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее блок

45

50

10

10

Это обеспечивается активированием мультиплексора 18 по входу стробиро- вания в эти моменты времени, обозначенные на временных диаграммах (см. фиг.2) штриховкой.

Появление сигнала ошибки при обращении к стеку на выходе мультиплексора 18 вызовет переключение триггеров 8 и 10 в единичное состояние. В результате этого на выходе 9 ошибки устройства появится активный уровень, свидетельствующий о возникновении ошибки в контролируемой системе, и

0

0

5

5 нач«ет светиться элемент 11 индика-

о

ции, который может быть назван Ошибка временного распределения при обращении к стеку. Эта информация определяет тип возникшей некорректной ситуации и может использоваться при ремонте контролируемой системы. Выход 9 ошибки устройства может соединяться с входом запроса прерывания микропроцессорной системы или ис5 пользоваться какими-либо другим образом по усмотрению разработчика. В первом случае при возникновении ошибки выполнение текущей программы прерывается и система переходит к выполнению программы обработки прерывания по ошибке. Программа обработки прерывания по ошибке может предусматривать восстановление процесса, нарушенного сбоем, может иметь диагностический характер (выявление причин ошибок)или в простейшем случае обеспечивать останов нарушенного процесса, В силу аппаратурных отказов или сбоя триггера разрешения прерывания микропроцессорная система может и не среагировать на запрос прерывания. Однако и в этом случае может быть выполнен останов нарушенного процесса, а свечение элементов блока 4 индикации и элемента. 11 индикации подскажет оператору причину возникшей ошибки.

После устранения причин, вызвавших ошибку, оператор микропроцессорной системы может, нажав кнопку сброса, вновь запустить программу сначала. При этом регистр 2, триггеры 8 и 10 и регистр 17 сдвига будут установлены в нулевое состояние, что обеспе5 чит исходное состояние устройства контроля. Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее блок

5

0

Постоянной памяти, регистр, дешифра- тор, блок элементов индикации, шифратор, первый мультиплексор, элемент ИЛИ, элемент индикации, три триггера, схему сравнения, причем адресный вход блока постоянной памяти является адресным входом устройства для подключения к шине адреса контролируемой Микропроцессорной системы, информа- ионный вход шифратора является информационным входом устройства для подключения к шине управления контролируемой микропроцессорной системы, рходы сброса регистра, первого и второго триггеров объединены и подключен $ш к входу сброса устройства, выход ервого триггера является выходом Ошибки устройства, группа выходов шифратора соединена с группой информационных входов первого мультиплексора, группа управляющих входов которо- |го и группа информационных входов регистра соединены с группой выходов

го триггера, информационный вход -которого объединен с вторым входом схемы сравнения и является младшим разрядом адресного входа устройства, о т- личающееся тем, что, с целью упрощения, устройство содержит регистр сдвига и второй мультиплексор, причем вход сброса регистра

сдвига подключен к входу сброса устройства, информационный вход регистра сдвига является входом Обращение к стеку устройства, вход стробирова- ния второго мультиплексора и вход

синхронизации регистра объединены и подключены к входу синхронизации устройства, группа управляющих входов второго мультиплексора соединена с группой выходов регистра сдвига, первый выход группы выходов которого соединен с входом синхронизации третьего триггера, нулевой и первый информационные входы второго мультиплексора подключены к входу логического

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1566332A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1559347A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что устройство содержит блок постоянной памяти, регистр, дешифратор, блок элементов индикации, три триггера, схему сравнения, регистр сдвига и второй мультиплексор. Устройство обеспечивает контроль микропроцессорных систем с тремя шинами. При этом обнаруживаются два типа некорректных ситуаций. 2 ил., 4 табл.

30

блока постоянной памяти, выход перво- 25 нуля устройства, второй информацион- Го мультиплексора соединен с первым Ьходом элемента ИЛИ и входом синхрони- &ации регистра, группа информацией- Йых выходов которого соединена с Группой информационных входов дешифратора, выходы которого с первого по i соединены с первым по т-м ходами блок-а индикации, единичный вход второго триггера объединен с вторым входом элемента ИЛИ, выход которого соединен с единичным входом первого триггера, первый вход схемы сравнения соединен с выходом третье35

ный вход второго мультиплексора подключен к входу логической единицы устройства, выход схемы сравнения соединен с третьим входом второго мультиплексора, четвертый, пятый и шестой информационные входы которого подключены к входу логического нуля устройства, седьмой информационный вход второго мультиплексора подключен к входу логической единицы устройства, выход второго мультиплексора соединен с вторым входом элемента ИЛИ.

Адресный массив

Устройства микропроцессорной системы

А,5 АНА,3 А12.А„

1 I 1

нуля устройства, второй информацион-

ный вход второго мультиплексора подключен к входу логической единицы устройства, выход схемы сравнения соединен с третьим входом второго мультиплексора, четвертый, пятый и шестой информационные входы которого подключены к входу логического нуля устройства, седьмой информационный вход второго мультиплексора подключен к входу логической единицы устройства, выход второго мультиплексора соединен с вторым входом элемента ИЛИ.

Таблица 1

ПЗУ

ОЗУ

Стек

Не использовано УВВ

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1417649, кло G 06 F 11/00, 1986. | |||

Авторы

Даты

1990-01-15—Публикация

1988-04-11—Подача