1

Изобретение относится к вычислительным моделирующим устройствам и может быть использовано в информационно-измерительных системах и моделирующих комплексах, например, при полунатурном моделировании систем воздзтпных сигналов (СВС), а также в авиационных тренажерах.

Цель изобретения - повьппение точности и расширение функциональных возможностей преобразователя за счет реализации воспроизведения выходных временных интервалов с заданным законом распределения.

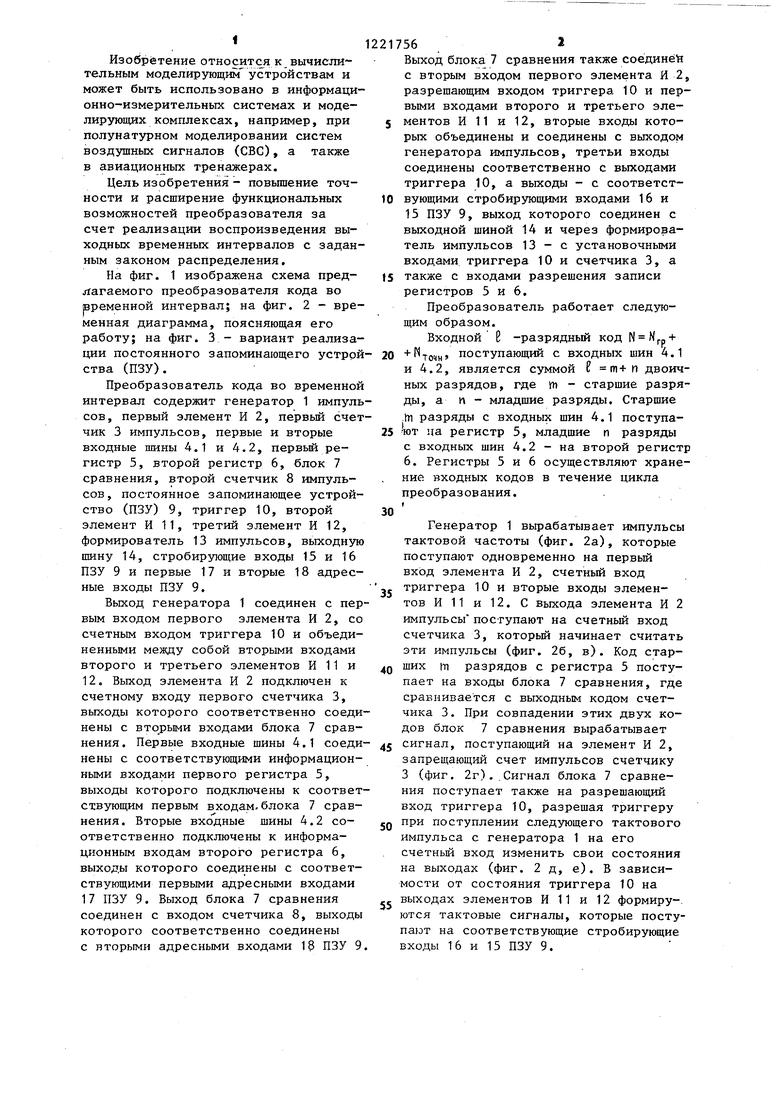

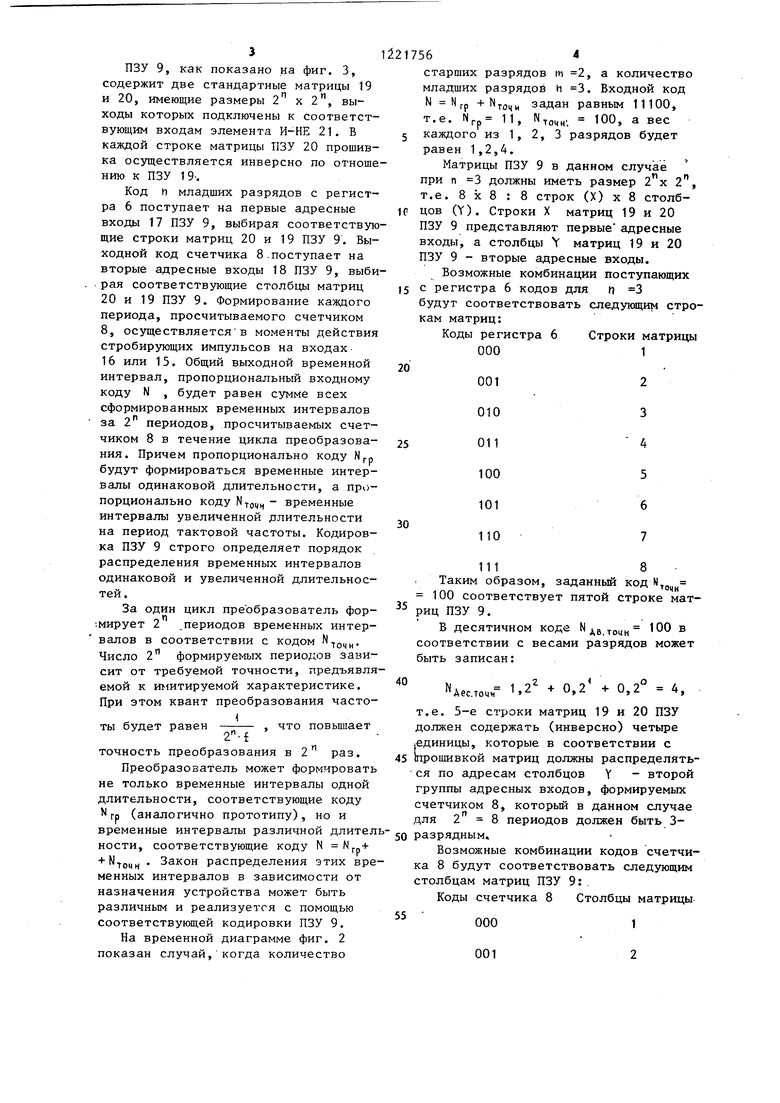

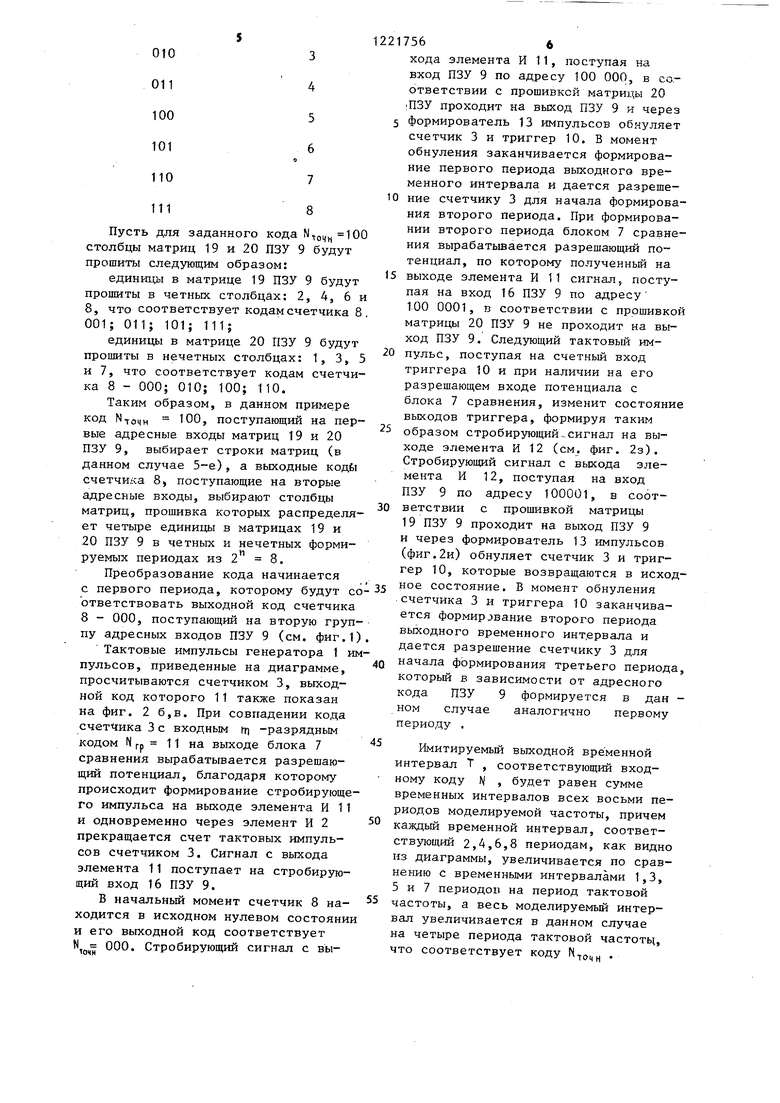

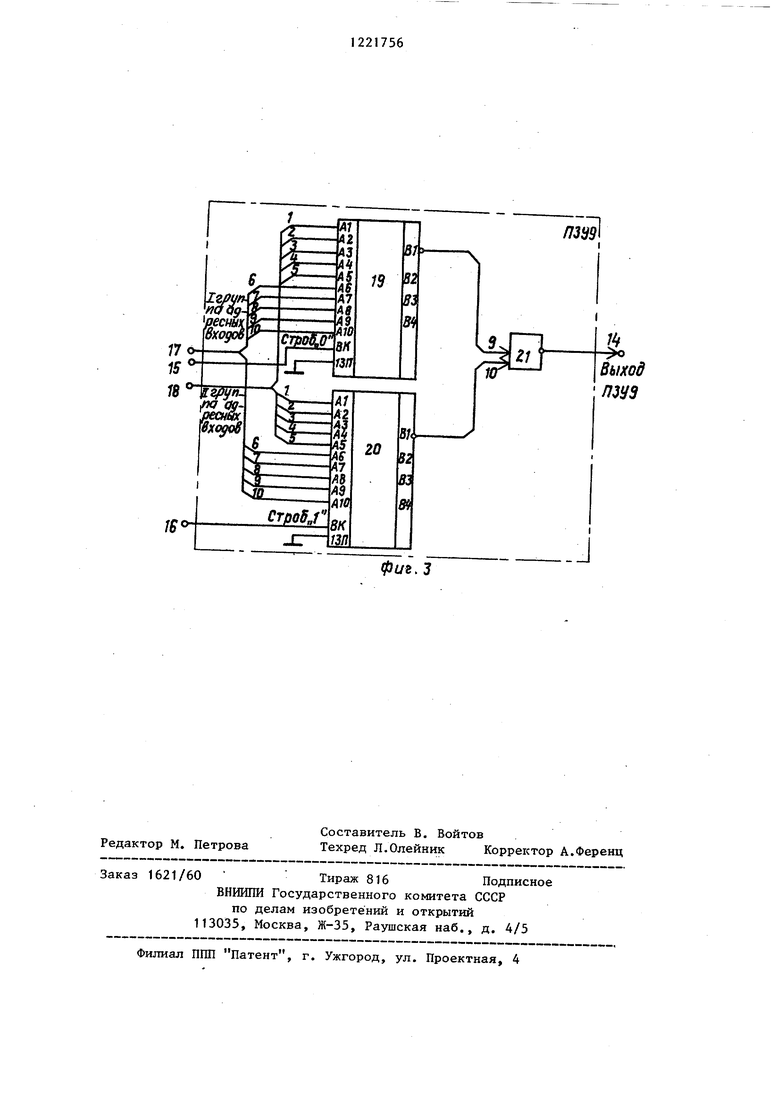

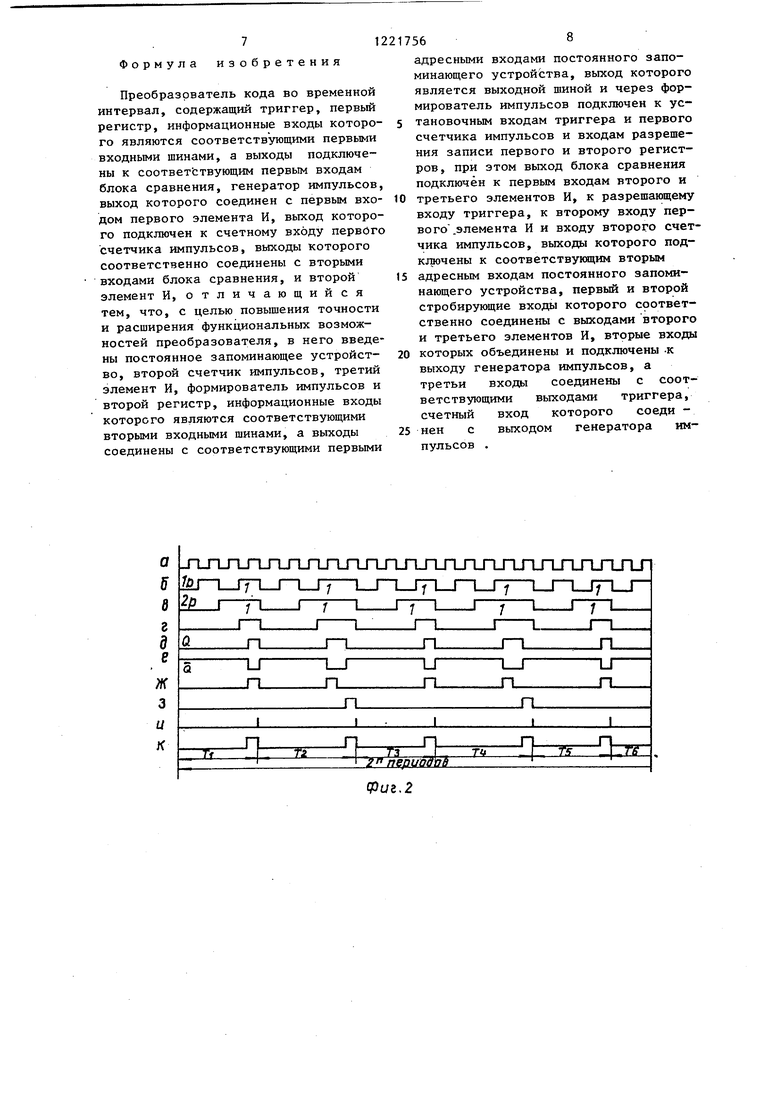

На фиг. 1 изображена схема пред- лагаемого преобразователя кода во временной интервал; на фиг. 2 - временная диаграмма, поясняющая его работу; на фиг. 3 - вариант реализации постоянного запоминающего устрой- ства (ПЗУ).

Преобразователь кода во временной интервал содержит генератор 1 импульсов, первый элемент И 2, первьй счетчик 3 импульсов, первые и вторые входные шины 4.1 и 4.2, первый регистр 5, второй регистр 6, блок 7 сравнения, второй счетчик 8 импульсов, постоянное запоминающее устройство (ПЗУ) 9, триггер 10, второй элемент И 11, третий элемент И 12, формирователь 13 импульсов, выходную шину 14, стробирующие входы 15 и 16 ПЗУ 9 и первые 17 и вторые 18 адресные входы ПЗУ 9.

Выход генератора 1 соединен с первым входом первого элемента И 2, со счетным входом триггера 10 и объединенными между собой вторыми входами второго и третьего элементов И 11 и 12. Выход элемента И 2 подключен к счетному входу первого счетчика 3, выходы которого соответственно соединены с вторыми входами блока 7 сравнения. Первые входные шины 4.1 соеди- нены с соответствующими информационными входами первого регистра 5, выходы которого подключены к соответствующим первым входам,блока 7 сравнения. Вторые вхбдные шины 4.2 со- ответственно подключены к информационным входам второго регистра 6, выходы которого Соединены с соответствующими первыми адресными входами 17 ПЗУ 9. Выход блока 7 сравнения соединен с входом счетчика 8, выходы которого соответственно соединены с вторыми адресными входами 18 ПЗУ 9.

56

Выход блока 7 сравнения также соединёй с вторым входом первого элемента И 2, разрешающим входом триггера 10 и первыми входами второго и третьего элементов И 11 и 12, вторые входы которых объединены и соединены с выходом генератора импульсов, третьи входы соединены соответственно с выходами триггера 10, а выходы - с соответствующими стробирующими входами 16 и 15 ПЗУ 9, выход которого соединен с выходной шиной 14 и через формирователь импульсов 13 - с установочными входами триггера 10 и счетчика 3, а также с входами разрешения записи регистров 5 и 6.

Преобразователь работает следующим образом.

Входной В -разрядный код N Nrp + + Р(-Г,„, поступающий с входных шин 4.1 и 4.2, является суммой В m+n двоичных разрядов, где m - старшие разряды, а п - младшие разряды. Старшие ,щ разряды с входных шин 4.1 поступа- ют ца регистр 5, младшие п разряды с входных шин 4.2 - на второй регистр 6. Регистры 5 и 6 осуществляют хранение входных кодов в течение цикла

преобразования, f

Генератор 1 вырабатывает импульсы тактовой частоты (фиг. 2а), которые поступают одновременно на первый вход элемента И 2, счетный вход триггера 10 и вторые входы элементов И 11 и 12. С выхода элемента И 2 импульсы поступают на счетньй вход счетчика 3, которьй начинает считать эти импульсы (фиг. 26, в). Код старших m разрядов с регистра 5 поступает на входы блока 7 сравнения, где сравнивается с выходным кодом счетчика 3. При совпадении этих двух кодов блок 7 сравнения вырабатывает сигнал, поступающий на элемент И 2, запрещающий счет импульсов счетчику 3 (фиг. 2г)..Сигнал блока 7 сравнения поступает также на разрешающий вход триггера 10, разрешая триггеру при поступлении следующего тактового импульса с генератора 1 на его счетньй вход изменить свои состояния на выходах (фиг. 2 д, е). В зависиости от состояния триггера 10 на выходах элементов И 11 и 12 формиру-. тся тактовые сигналы, которые постуают на соответствующие стробирующие ходы 16 и 15 ПЗУ 9.

ПЗУ 9, как показано на фиг. 3, содержит две стандартные матрицы 19 и 20, имеющие размеры 2 х 2, выходы которых подключены к соответствующим входам элемента И-НЕ 21, В каждой строке матрицы ПЗУ 20 прошивка осуществляется инверсно по отношению к ПЗУ 19-.

Код и младших разрядов с регистра 6 поступает на первые адресные входы 17 ПЗУ 9, выбирая соответствующие строки матриц 20 и 19 ПЗУ 9. Выходной код счетчика 8.поступает на вторые адресные входы 18 ПЗУ 9, выбирая соответствующие столбцы матриц 20 и 19 ПЗУ 9. Формирование каждого периода, просчитываемого счетчиком 8, осуществляется в моменты действия стробирующих импульсов на входах 16 или 15. Общий выходной временной интервал, пропорциональный входному коду N , будет равен сумме всех сформированных временных интервалов за 2 периодов, просчитываемых счетчиком 8 в течение цикла преобразования. Причем пропорционально коду N|.p будут формироваться временные интервалы одинаковой длительности, а пропорционально коду NrogH временные интервалы увеличенной длительности на период тактовой частоты. Кодировка ПЗУ 9 строго определяет порядок распределения временных интервалов одинаковой и увеличенной длительностей.

За один цикл преобразователь фор- 1мирует 2 периодов временных интервалов в соответствии с кодом (TOMH Число 2 формируемых периодов зависит от требуемой точности, предъявляемой к имитируемой характеристике. При этом квант преобразования частоты будет равен , что повышает

точность преобразования в 2 раз.

Преобразователь может формировать не только временные интервалы одной длительности, соответствующие коду N гр (аналогично прототипу), но и

старших разрядов m 2, а количество младших разрядов И 3. Входной код N N гр + Мтоцн задан равным 11100, т.е. Nrp 11, 100, а вес 5 каждого из 1, 2, 3 разрядов будет равен 1,2,4.

Матрицы ПЗУ 9 в данном случае при п 3 должны иметь размер 2 х 2, т.е. 8x8:8 строк (X) х 8 столб- IP цов (Y). Строки X матриц 19 и 20 ПЗУ 9 представляют первые адресные входы, а столбцы Y матриц 19 и 20 ПЗУ 9 - вторые адресные входы.

Возможные комбинации поступающих 15 с регистра 6 кодов для Ц 3

будут соответствовать следующим строкам матриц:

Коды регистра 6 Строки матрицы

1

20

25

30

000 001 010 011 100 101 110 111

2 3

4

8

Таким образом, заданный кодЯ 100 соответствует пятой строке мат- риц ПЗУ 9.

В десятичном коде N д очн 00 в соответствии с весами разрядов может быть записан:

40

N,

1,2 + 0,2 + 0,2°

4,

Аес.томн

т.е. 5-е строки матриц 19 и 20 ПЗУ должен содержать (инверсно) четьфе .единицы, которые в соответствии с 45 (прошивкой матриц должны распределяться по адресам столбцов Y - второй группы адресных входов, формируемых счетчиком 8, который в данном случае для 2 8 периодов должен быть 3- временные интервалы различной длитель-JQ разрядным.

Возможные комбинации кодов счетчиности, соответствующие коду N

+ N,

Закон распределения этих вре точнменных интервалов в зависимости от

назначения устройства может быть различным и реализуется с помощью соответствующей кодировки ПЗУ 9. На временной диаграмме фиг. 2 показан случай, когда количество

ка 8 будут соответствовать следующим столбцам матриц ПЗУ 9:.

Коды счетчика 8 Столбцы матрицы55

000

001

1

217564

старших разрядов m 2, а количество младших разрядов И 3. Входной код N N гр + Мтоцн задан равным 11100, т.е. Nrp 11, 100, а вес 5 каждого из 1, 2, 3 разрядов будет равен 1,2,4.

Матрицы ПЗУ 9 в данном случае при п 3 должны иметь размер 2 х 2, т.е. 8x8:8 строк (X) х 8 столб- IP цов (Y). Строки X матриц 19 и 20 ПЗУ 9 представляют первые адресные входы, а столбцы Y матриц 19 и 20 ПЗУ 9 - вторые адресные входы.

Возможные комбинации поступающих 15 с регистра 6 кодов для Ц 3

будут соответствовать следующим строкам матриц:

Коды регистра 6 Строки матрицы

1

20

25

30

000 001 010 011 100 101 110 111

2 3

4

8

Таким образом, заданный кодЯ 100 соответствует пятой строке мат- риц ПЗУ 9.

В десятичном коде N д очн 00 в соответствии с весами разрядов может быть записан:

N,

1,2 + 0,2 + 0,2°

4,

Аес.томн

ка 8 будут соответствовать следующим столбцам матриц ПЗУ 9:.

Коды счетчика 8 Столбцы матрицы55

000

001

3 4 5 6 7

Пусть для заданного кода N,o 100 столбцы матриц 19 и 20 ПЗУ 9 будут прошиты следзпощим образом:

единицы в матрице 19 ПЗУ 9 будут прошиты в четных столбцах: 2, 4, 6 и 8, что соответствует кодам счетчика 8 001; 011; 101; 111;

единицы в матрице 20 ПЗУ 9 будут прошиты в нечетных столбцах: 1, 3, 5 и 7, что соответствует кодам счетчика 8 - 000; 010; 100; 110.

Таким образом, в данном примере код N-гочн 100 поступающий на первые адресные входы матриц 19 и 20 ПЗУ 9, выбирает строки матриц (в данном случае 5-е) , а выходные кодб1 счетчика 8 поступающие на вторые адресные входы, выбирают столбцы матриц, прошивка которых распределяет четыре единицы в матрицах 19 и 20 ПЗУ 9 в четных и нечетных формируемых периодах из 2 8,

Преобразование кода начинается с первого периода, которому будут со ответствовать выходной код счетчика 8 - 000, поступающий на вторую группу адресных входов ПЗУ 9 (см, фиг,1)

Тактовые импульсы генератора 1 им пульсов, приведенные на диаграмме, просчитываются счетчиком 3, выходной код которого 11 также показан на фиг. 2 б,в. При совпадении кода счетчика 3 с входным ITI -разрядным кодом N гр 11 на выходе блока 7 сравнения вырабатывается разрешающий потенциал, благодаря которому происходит формирование стробирующе- го импульса на выходе элемента И 11 и одновременно через элемент И 2 прекращается счет тактовых импульсов счетчиком 3. Сигнал с выхода элемента 11 поступает на стробирую- щий вход 16 ПЗУ 9.

В начальный момент счетчик 8 находится в исходном нулевом состоянии и его выходной код соответствует N 000. Стробирующий сигнал с вы

2217566

хода элемента И 11, поступая на вход ПЗУ 9 по адресу 100 000, в соответствии с прошивкой матрицы 20 ПЗУ проходит на выход ПЗУ 9 и через 5 формирователь 13 импульсов обнуляет счетчик 3 и триггер 10. В момент обнуления заканчивается формирование первого периода выходного временного интервала и дается разреше- 10 ние счетчику 3 для начала формирования второго периода. При формировании второго периода блоком 7 сравнения вырабатьшается разрешающий потенциал, по которому полученный на 15 выходе элемента И 11 сигнал, поступая на вход 16 ПЗУ 9 по адресу 100 0001, в соответствии с прошивкой матрицы 20 ПЗУ 9 не проходит на выход ПЗУ 9. Следующий тактовый им- 20 пульс, поступая на счетный вход триггера 10 и при наличии на его разрешающем входе потенциала с блока 7 сравнения, изменит состояние выходов триггера, формируя таким 25 образом Стробирующий--сигнал на выходе элемента И 12 (см. фиг. 2з). Стробирующий сигнал с выхода элемента И 12, поступая на вход ПЗУ 9 по адресу 100001, в соот- 30 ветствии с прошивкой матрицы 19 ПЗУ 9 проходит на выход ПЗУ 9 и через формирователь 13 импульсов (фиг.2и) обнуляет счетчик 3 и триггер 10, которые возвращаются в исход35 и° состояние. В момент обнуления

счетчика 3 и триггера 10 заканчивается формирование второго периода выходного временного интервала и дается разрешение счетчику 3 для 40 начала формирования третьего периода, который в зависимости от адресного кода ПЗУ 9 формируется в дан - ном случае аналогично первому периоду ,

Имитируемый выходной временной интервал Т , соответствующий входному коду М , будет равен сумме временных интервалов всех восьми периодов моделируемой частоты, причем каждый временной интервал, соответствующий 2,4,6,8 периодам, как видно из диаграммы, увеличивается по сравнению с временными интервалами 1,3, 5 и 7 периодов на период тактовой частоты, а весь моделируемый интервал увеличивается в данном случае на четыре периода тактовой частоту, что соответствует коду

Формула изобретения

Преобразователь кода во временной интервал, содержащий триггер, первый регистр, информационные входы которого являются соответствующими первыми входными шинами, а выходы подключены к соответ ствующим первым входам блока сравнения, генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого подключен к счетному входу первого счетчика импульсов, выходы которого соответственно соединены с вторыми входами блока сравнения, и второй элемент И, отличающийся тем, что, с целью повышения точности и расширения функциональных возможностей преобразователя, в него введены постоянное запоминающее устройство, второй счетчик импульсов, третий элемент И, формирователь импульсов и второй регистр, информационные входы которого являются соответствующими вторыми входными шинами, а выходы соединены с соответствующими первыми

адресными входами постоянного запоминающего устройства, выход которого является выходной шиной и через формирователь импульсов подключен к установочным входам триггера и первого счетчика импульсов и входам разрешения записи первого и второго регистров, при этом выход блока сравнения подключён к первым входам второго и третьего элементов И, к разрешающему входу триггера, к второму входу первого.элемента И и входу второго счетчика импульсов, выходы которого под- кхрочены к соответствукяцим вторым адресным входам постоянного запоминающего устройства, первый и второй стробирующие входы которого срответ- ственно соединены с выходами второго и третьего элементов И, вторые входы которых объединены и подключены -к выходу генератора импульсов, а третьи входы соединены с соответствующими выходами триггера, счетный вход которого соеди - нен с выходом генератора импульсов .

(рае.2

Редактор М. Петрова

Составитель В, Войтов

Техред Л.Олейник Корректор А.Ференц

Заказ 1621/60 - Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

фиг. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1585790A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для решения транспортных задач линейного программирования | 1991 |

|

SU1814082A1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для ввода информации | 1982 |

|

SU1048465A1 |

Изобретение относится к вычислительным моделирующим устройством и может быть использовано в информационно-измерительных системах и моделирующих комплексах. Изобретение позволяет повысить точность и расширить функциональные возможности преобразователя за счет реализации Входные „ шины воспроизведения выходных временных интервалов с заданным законом распределения путем введения в устройство, содержащее триггер 10, первьй регистр 5, блок 7 сравнения, генератор 1 импульсов, первый 2 и второй 11 элементы И, первый 3 счетчик импульсов, постоянного запоминающего устройства 9, второго счетчика 8 импульсов, третьего элемента И 12, формирователя 13 импульсов, второго регистра 6. Преобразователь может формировать не только временные интервалы одной длительности, соответствующие коду N , но и временные интервалы различной длительности, соответствующие коду N гр точн Закон распределения этих временных интервалов в зависимости от назначения устройства может быть различным и реализуется с помощью соответствующей кодировки постоянного запоминающего устройства 9. 3 ил. (Л С Izpunna адресных Выходная

| Мартяшин К.И | |||

| и др | |||

| Преобразователи электрических параметров для систем контроля и измерения | |||

| М., 1976, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Гбрелик А.Л | |||

| идр | |||

| Бортовые цифровые вычислительные машины | |||

| М., 1975, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-10—Подача