1129

Изобретение относится к вычислительной технике, предназначено для сдвига информации и может использоваться в процессорах малых и средних ЭВМ, вычислительных уст- ройствах и приборах цифровой автоматики.

Целью изобретения является повышение быстродействия.

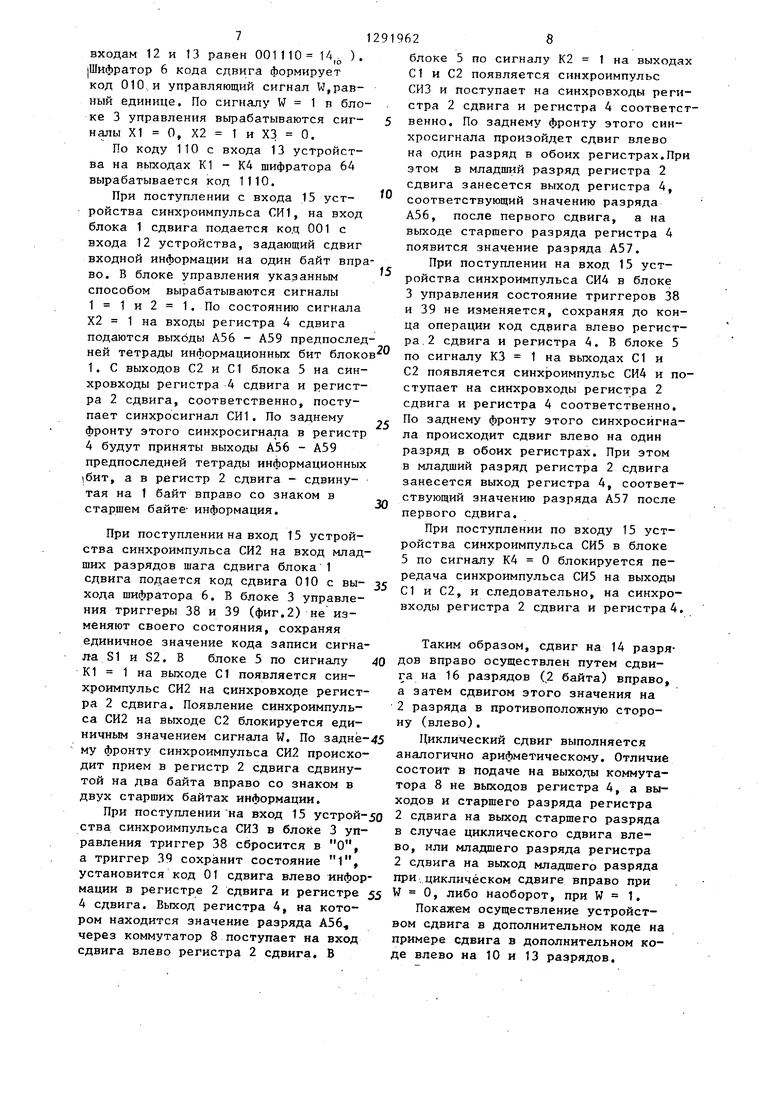

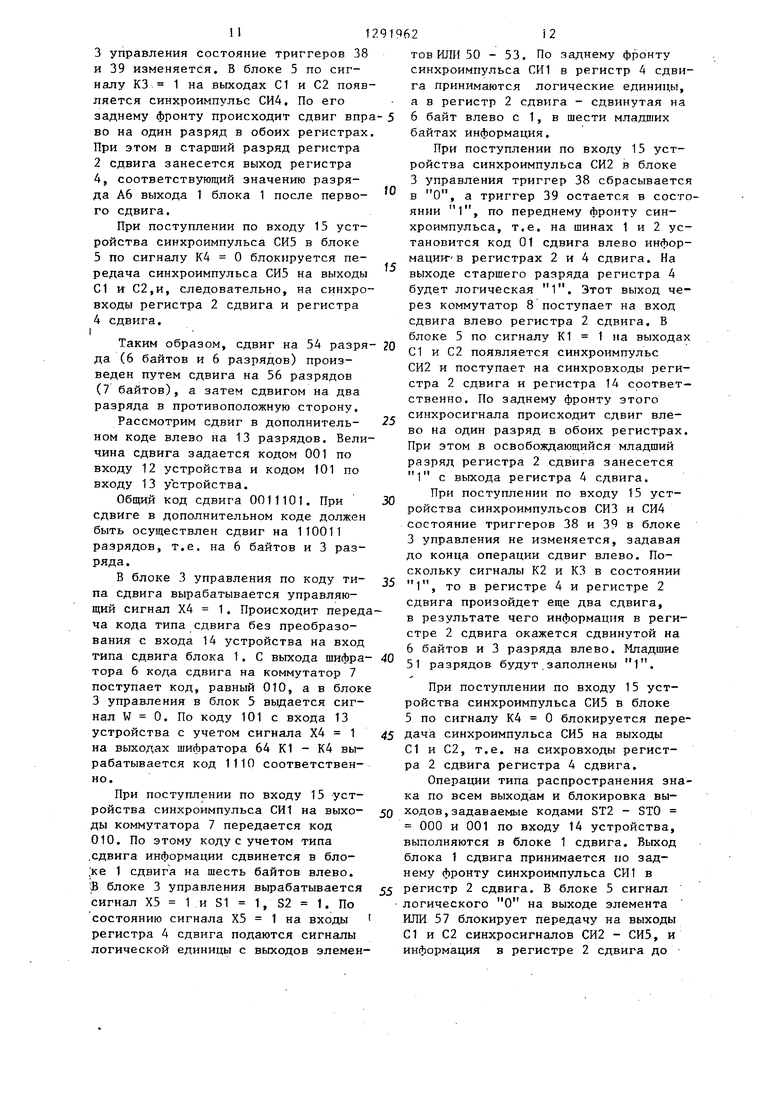

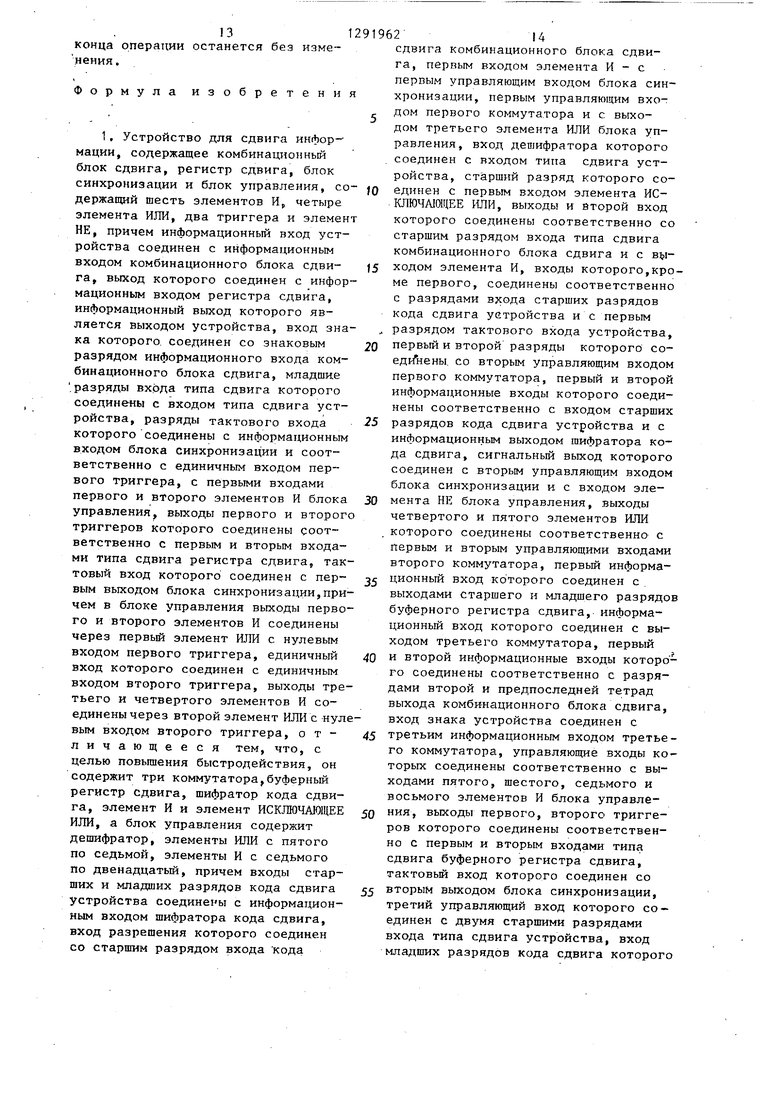

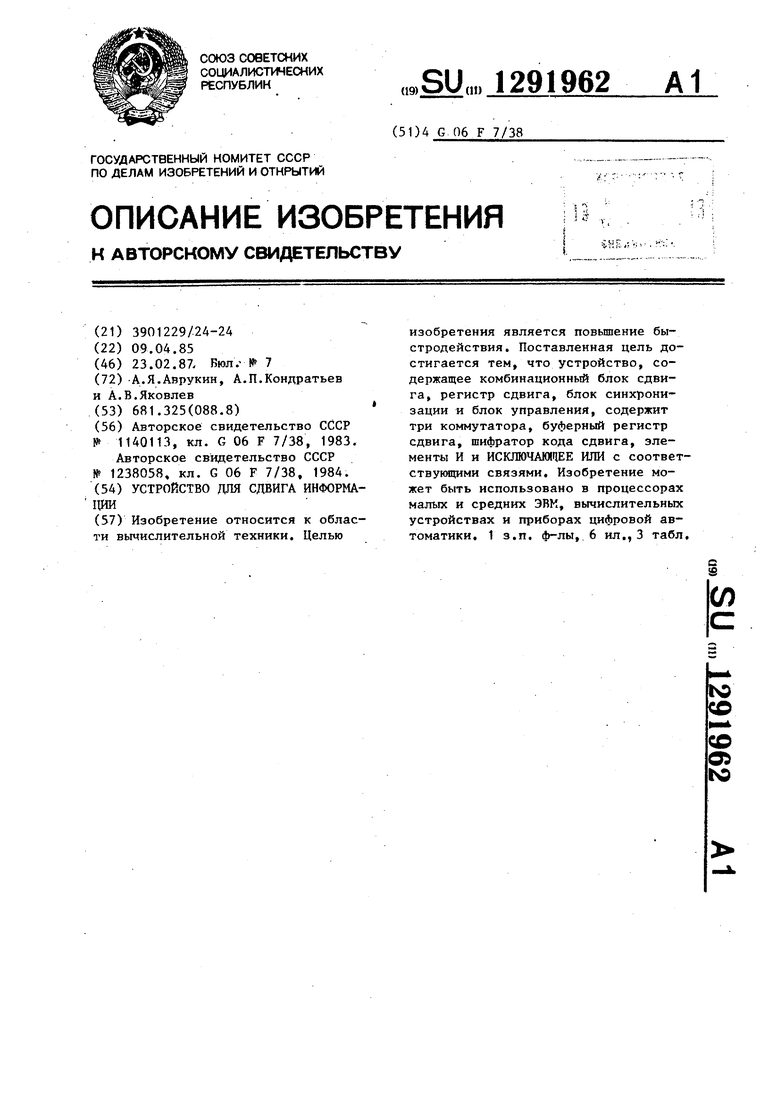

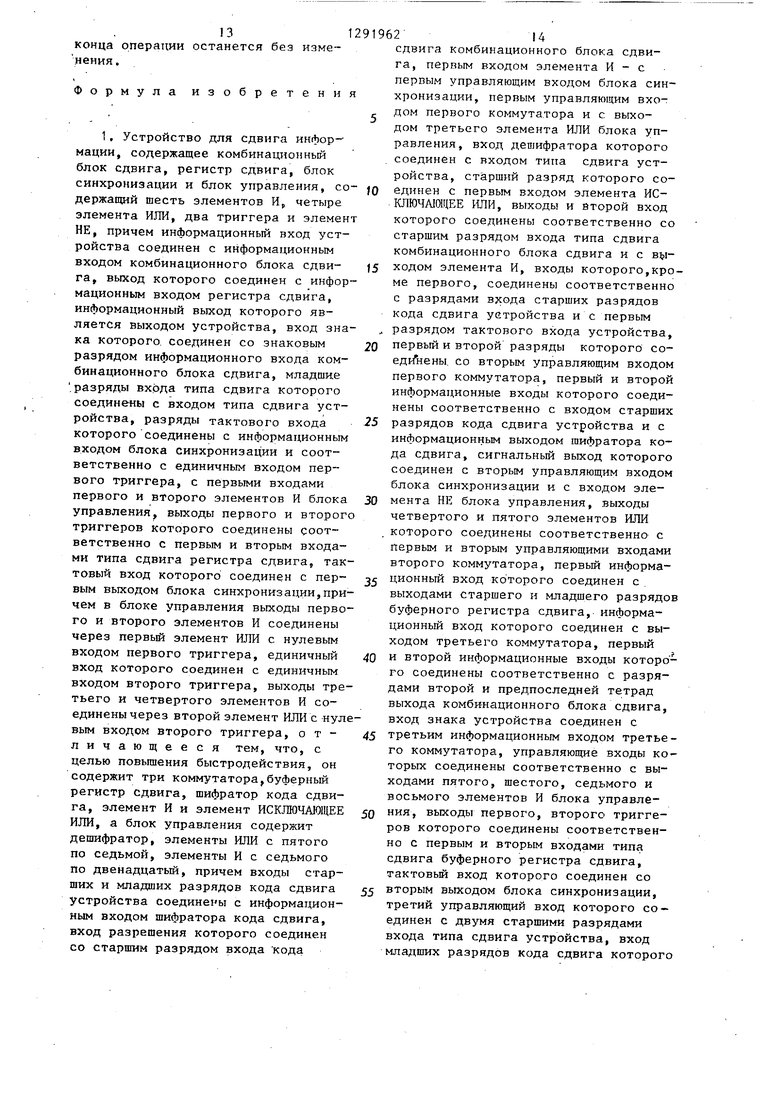

На фиг.1 представлена схема уст- ройства для сдвига информации; на фиг.2 - схема блока управления; на фиг.З - схема третьего коммутатора; на фиг.4 - схема блока синхронизации; на фиг.З - схема разряда первого коммутатора; на фиг.6 - временная диаграмма работы устройства.

Блоки устройства представлены для шестидесятичетырехразрядного устройства.

Устройство для сдвига информации (фИг.1) содержит комбинационный блок 1 сдвига, регистр 2 сдвига, блок 3 управления, буферный регистр 4 сдвига, блок 5 синхронизации, шифратор 6 кода сдвига, коммутаторы 7-9, злемент И 10, элемент ИСК.ШОЧАЮ1ДЕЕ ИЛИ 11, входы 12 и 13 старших и младших разрядов кода сдвига устройства, вход 14 типа сдвига устройства, тактовый вход 15 устройства, выход 16 устройства, вход 17 знака устройства, информационный вход 18 устройства.

Блок 3 управления (фиг.2) содержит элемент НЕ 19, элементы ИЛИ 20- 26, элементы И 27 - 37, триггеры 38 и 39, элемент И 40 и дешифратор 41.

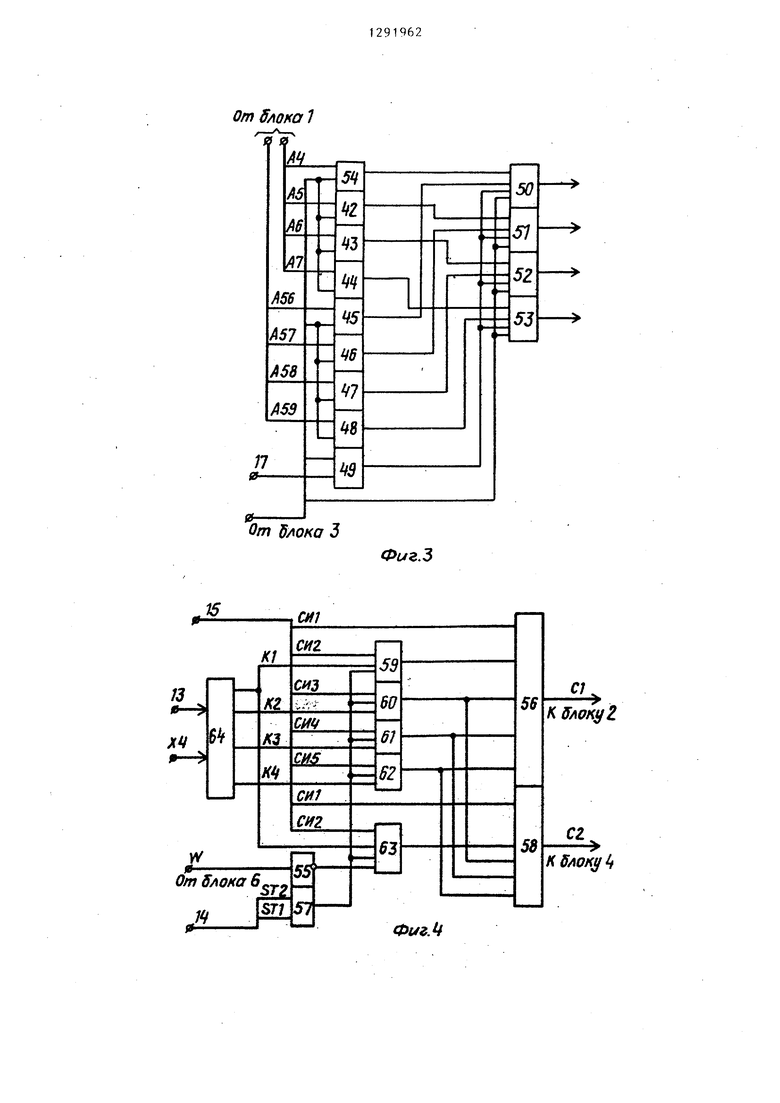

Третий коммутатор 9 (фиг.З) содержит элементы И 42 - 49, элементы ИЛИ 50 - 53, элементы И 54.

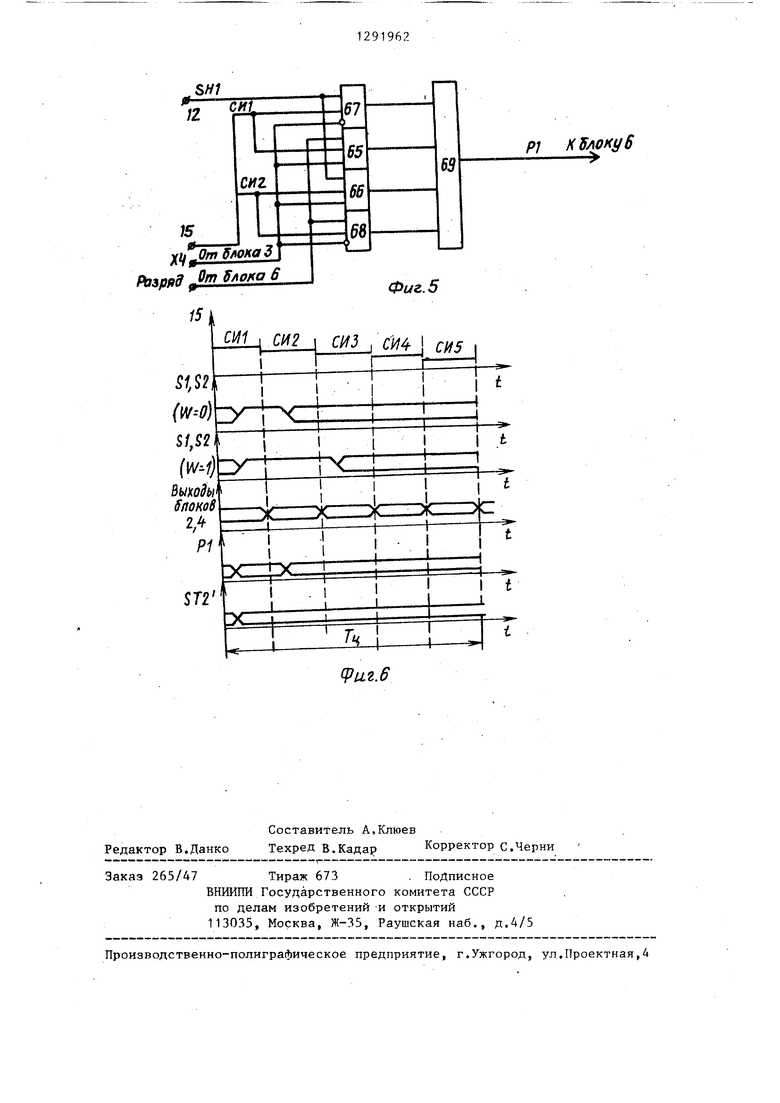

Блок 5 синхронизации (фиг.4) содержит элемент НЕ 5, элементы ИЛИ 56 - 58, элементы НЕ 59 - 63, шифратор 64.

Разряд первого коммутатора 7 (фиг.5) содержит элементы И 65 и 66 элементы 67 и 68 запрета и злемент ИЛИ 69.

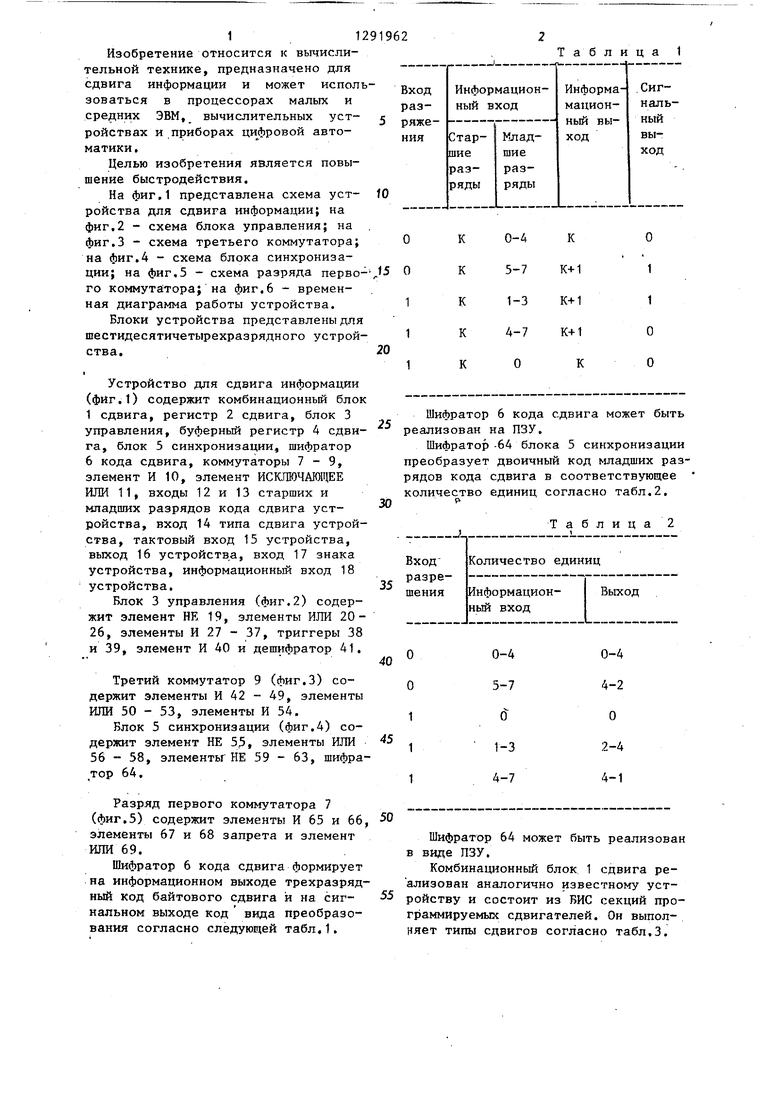

Шифратор 6 кода сдвига формирует на информационном выходе трехразрядный код байтового сдвига и на сигнальном выходе код вида преобразования согласно следующей табл,1.

Таблица 1

Шифратор 6 кода сдвига может быть реализован на ПЗУ.

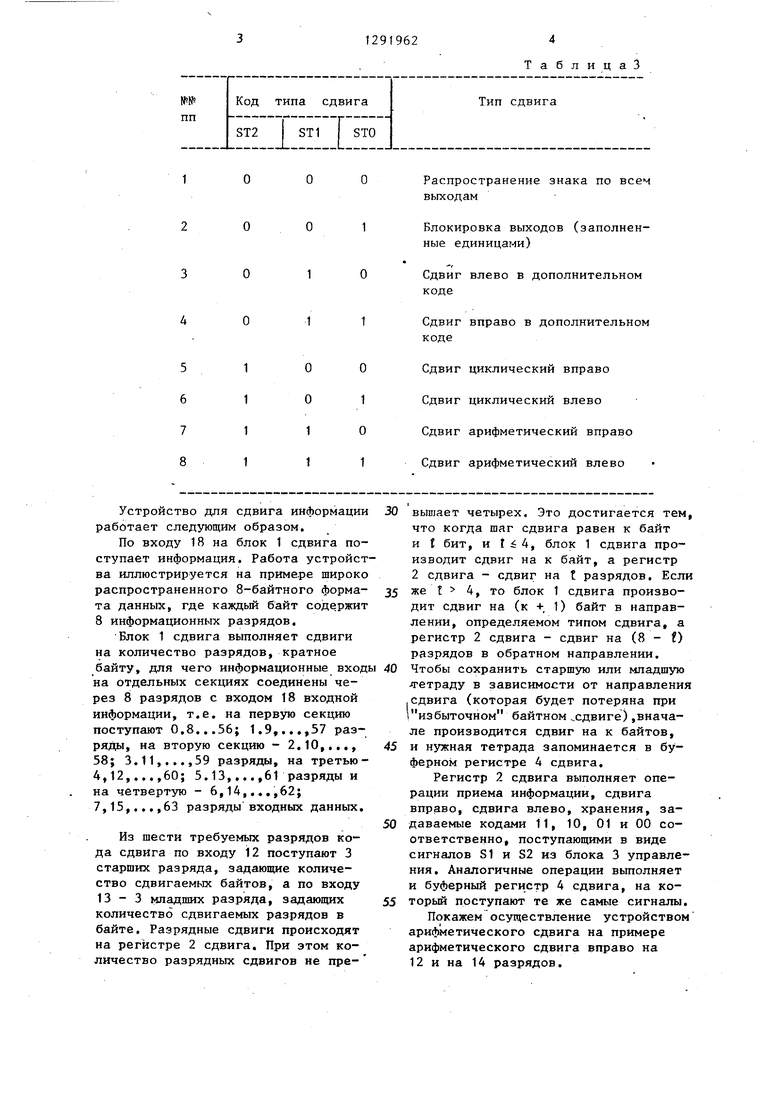

Шифратор -64 блока 5 синхронизации преобразует двоичный код младших разрядов кода сдвига в соответствующее

количество единиц согласно табл.2. f

Таблица 2

Шифратор 64 может быть реализован в виде ЛЗУ.

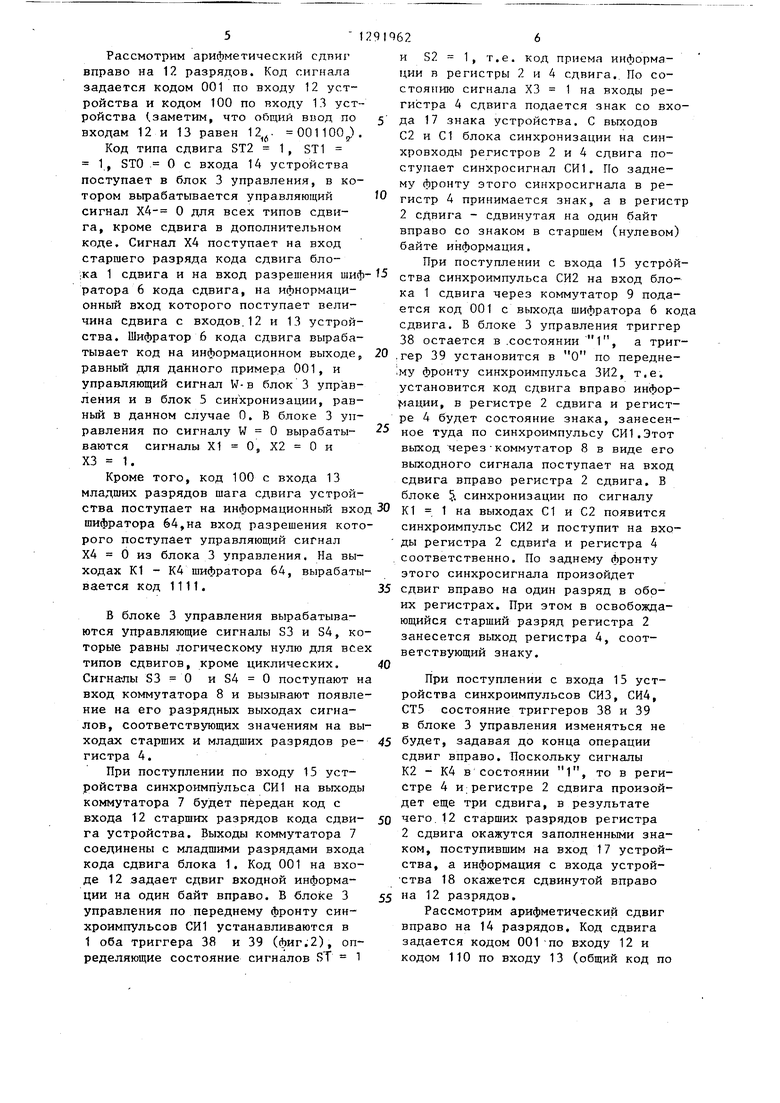

Комбинац11онный блок 1 сдвига ре- ализован ангшогично известному устройству и состоит из БИС секций программируемых сдвигателей. Он выполняет типы сдвигов согласно табл.3.

Устройство для сдвига информации работает следующим образом.

По входу 18 на блок 1 сдвига поступает информация. Работа устройства иллюстрируется на примере широко распространенного 8-байтного форма- та данных, где каждьй байт содержит 8 информационных разрядов.

Блок 1 сдвига выполняет сдвиги на количество разрядов, кратное байту, для чего информационные вход на отдельных секциях соединены через 8 разрядов с входом 18 входной информации, т.е. на первую секцию поступают О.8...56; 1.9,..,,57 разряды, на вторую секцию - 2.10,.,,, 58; 3.11,...,59 разряды, на третью- 4,12,...,60; 5.13,...,6Гразряды и на четвертую - 6,14,,,,,62; 7,15,...,63 разряды входных данных.

Из шести требуемых разрядов кода сдвига по входу 12 поступают 3 старших разряда, задающие количество сдвигаемых байтов, а по входу 13-3 младших разряда, задающих количество сдвигаемых разрядов в байте. Разрядные сдвиги происходят на регистре 2 сдвига. При этом количество разрядных сдвигов не пре0

5

0 5

0

5

вышает четырех. Это достигается тем, что когда шаг сдвига равен к байт и t бит, и I i 4, блок 1 сдвига производит сдвиг на к байт, а регистр 2 сдвига - сдвиг на t разрядов. Если же I 4, то блок 1 сдвига производит сдвиг на (к + 1) байт в направлении, определяемом типом сдвига, а регистр 2 сдвига - сдвиг на (8 - f) разрядов в обратном направлении. Чтобы сохранить старшую или младшую л-етраду в зависимости от направления .сдвига (которая будет потеряна при избыточном байтном „сдвиге),вначале производится сдвиг на к байтов, и нужная тетрада запоминается в буферном регистре 4 сдвига.

Регистр 2 сдвига выполняет операции приема информации, сдвига вправо, сдвига влево, хранения, задаваемые кодами 11, 10, 01 и 00 соответственно, поступающими в виде сигналов S1 и S2 из блока 3 управления. Аналогичные операции выполняет и буферный регистр 4 сдвига, на который поступают те же самые сигналы. Покажем осуществление устройством арифметического сдвига на примере арифметического сдвига вправо на 12 и на 14 разрядов.

Рассмотрим арифметический сдвиг вправо на 12 разрядов. Код сигнала задается кодом 001 по входу 12 устройства и кодом 100 по входу 13 устройства (.заметим, что общий ввод по входам 12 и 13 равен 12. 001100,;).

Код типа сдвига ST2 1 , ST1 1, STO О с входа 14 устройства поступает в блок 3 управления, в котором вырабатывается управляющий сигнал Х4- О для всех типов сдвига, кроме сдвига в дополнительном коде. Сигнал Х4 поступает на вход старшего разряда кода сдвига блоПри поступлении с входа 15 устрбй:.ка 1 сдвига и на вход разрешения шиф- t5 тва синхроимпульса СИ2 на вход блоратора 6 кода сдвига, на ифнормаци- онный вход которого поступает величина сдвига с входов.12 и 13 устройства. Шифратор 6 кода сдвига вырабатывает код на информационном выходе, равный для данного примера 001, и управляющий сигнал W-в блок 3 управления и в блок 5 синхронизации, равный в данном случае 0. В блоке 3 управления по сигналу W О вырабатываются сигналы Х1 О, Х2 О и ХЗ 1.

Кроме того, код 100 с входа 13 младших разрядов шага сдвига устрой20

25

ка 1 сдвига через коммутатор 9 подается код 001 с выхода шифратора 6 код сдвига. В блоке 3 управления триггер 38 остается в .состоянии 1, а триг- .гер 39 установится в О по передне- ;му фронту синхроимпульса ЗИ2, т.е. установится код сдвига вправо инфор- , в регистре 2 сдвига и регистре 4 будет состояние знака, занесенное туда по синхроимпульсу СИ1.Этот выход черезкоммутатор 8 в виде его выходного сигнала поступает на вход сдвига вправо регистра 2 сдвига. В блоке 5. синхронизации по сигналу

ства поступает на информационный вход 30 К1 1 на выходах С1 и С2 появится шифратора 64,на вход разрешения которого поступает управляющий сигнал Х4 О из блока 3 управления. На выходах К1 - К4 шифратора 64, вырабатывается код 1111.

синхроимпульс СИ2 и поступит на вхо- ды регистра 2 сдвиг а и регистра 4 соответственно. По заднему фронту этого синхросигнала произойдет 35 сдвиг вправо на один разряд в обоих регистрах. При этом в освобождающийся старший разряд регистра 2 занесется выход регистра 4, соответствующий знаку.

В блоке 3 управления вырабатываются управляющие сигналы S3 и S4, которые равны логическому нулю для всех типов сдвигов, кроме циклических. Сигна-лы S3 О и S4 О поступают на вход коммутатора 8 и вызывают появление на его разрядных выходах сигналов, соответствующих значениям на выходах старших и младших разрядов регистра 4.

При поступлении по входу 15 устройства синхроимпульса СИ1 на выходы коммутатора 7 будет передан код с входа 12 старших разрядов кода сдвига устройства. Выходы коммутатора 7 соединены с младшими разрядами входа кода сдвига блока 1. Код 001 на входе 12 задает сдвиг входной информации на один байт вправо. В блоке 3 управления по переднему фронту синхроимпульсов СИ1 устанавливаются в 1 оба триггера 38 и 39 (фиг.2), определяющие состояние сигналов ST 1

и S2 1, т.е. код приема информации в регистры 2 и 4 сдвига.. По состоянию сигнала ХЗ 1 на входы регистра 4 сдвига подается знак со входа 17 знака устройства. С выходов С2 и С1 блока синхронизации на син- хровходы регистров 2 и 4 сдвига поступает синхросигнал СИ1. По заднему фронту этого синхросигнала в регистр 4 принимается знак, а в регистр 2 сдвига - сдвинутая на один байт вправо со знаком в старшем (нулевом) байте информация.

При поступлении с входа 15 устрбй тва синхроимпульса СИ2 на вход бло0

5

ка 1 сдвига через коммутатор 9 подается код 001 с выхода шифратора 6 кода сдвига. В блоке 3 управления триггер 38 остается в .состоянии 1, а триг- .гер 39 установится в О по передне- ;му фронту синхроимпульса ЗИ2, т.е. установится код сдвига вправо инфор- , в регистре 2 сдвига и регистре 4 будет состояние знака, занесенное туда по синхроимпульсу СИ1.Этот выход черезкоммутатор 8 в виде его выходного сигнала поступает на вход сдвига вправо регистра 2 сдвига. В блоке 5. синхронизации по сигналу

К1 1 на выходах С1 и С2 появится

синхроимпульс СИ2 и поступит на вхо- ды регистра 2 сдвиг а и регистра 4 соответственно. По заднему фронту этого синхросигнала произойдет сдвиг вправо на один разряд в обоих регистрах. При этом в освобождающийся старший разряд регистра 2 занесется выход регистра 4, соответствующий знаку.

При поступлении с входа 15 устройства синхроимпульсов СИЗ, СИ4, СТ5 состояние триггеров 38 и 39 в блоке 3 управления изменяться не

будет, задавая до конца операции сдвиг вправо. Поскольку сигналы К2 - К4 в состоянии 1, то в регистре 4 и регистре 2 сдвига произойдет еще три сдвига, в результате

чего.12 старших разрядов регистра 2 сдвига окажутся заполненными знаком, поступившим на вход 17 устройства, а информация с входа устрой- ства 18 окажется сдвинутой вправо

ча 12 разрядов.

Рассмотрим арифметический сдвиг вправо на 14 разрядов. Код сдвига задается кодом 001 по входу 12 и кодом 110 по входу 13 (общий код по

входам 12 и 13 равен 001110 14, ). |Шифратор 6 кода сдвига формирует код 010.и управляющий сигнал W,равный единице. По сигналу W 1 в бло- ке 3 управления вырабатываются сиг- налы XI О, Х2 1 и ХЗ 0.

По коду 110 с входа 13 устройства на выходах К1 - К4 шифратора 64 вырабатывается код 1110.

При поступлении с входа 15 уст- ройства синхроимпульса СИ1, на вход блока 1 сдвига подается код 001 с входа 12 устройства, задающий сдвиг входной информации на один байт вправо. В блоке управления указанным способом вырабатываются сигналы 1 1 и 2 1. По состоянию сигнала Х2 1 на входы регистра 4 сдвига подаются выходы А56 - А59 предпоследней тетрады информационных бит блоко 1. С выходов С2 и С1 блока 5 на син- хровходы регистра 4 сдвига и регистра 2 сдвига, соответственно, поступает синхросигнал СИ1. По заднему фронту этого синхросигнала в регистр А будут приняты выходы А56 - А59 предпоследней тетрады информационных (бит, а в регистр 2 сдвига - сдвинутая на 1 байт вправо со знаком в старшем байте- информация.

При поступлении на вход 15 устройства синхроимпульса СИ2 на вход младших разрядов шага сдвига блока 1 сдвига подается код сдвига 010 с вы- 35 хода шифратора 6. В блоке 3 управления триггеры 38 и 39 (фиг,2) не изменяют своего состояния, сохраняя единичное значение кода записи сигнала S1 и S2. В блоке 5 по сигналу 40 К1 1 на выходе С1 появляется синхроимпульс СИ2 на синхровходе регистра 2 сдвига. Появление синхроимпульса СИ2 на выходе С2 блокируется единичным значением сигнала W. По заднё-45 му фронту синхроимпульса СИ2 происходит прием в регистр 2 сдвига сдвинутой на два байта вправо со знаком в двух старших байтах информации.

При поступлении на вход 15 устрой-50 ства синхроимпульса СИЗ в блоке 3 управления триггер 38 сбросится в О, а триггер 39 сохранит состояние 1, установится код 01 сдвига влево информации в регистре 2 сдвига и регистре 55 4 сдвига. Выход регистра 4, на котором находится значение разряда А56, через коммутатор 8 поступает на вход сдвига влево регистра 2 сдвига. В

5

. 5

5

0

5 0 5

0

блоке 5 по сигналу К2 1 на выходах С1 и С2 появляется синхроимпульс СИЗ и поступает на синхровходы регистра 2 сдвига и регистра 4 соответственно. По заднему фронту этого синхросигнала произойдет сдвиг влево на один разряд в обоих регистрах.При этом в младш11й разряд регистра 2 сдвига занесется выход регистра 4, соответствующий значению разряда А56, после первого сдвига, а на выходе старшего разряда регистра 4 появится значение разряда А57.

При поступлении на вход 15 устройства синхроимпульса СИ4 в блоке 3 управления состояние триггеров 38 и 39 не изменяется, сохраняя до конца операции код сдрига влево регистра , 2 сдвига и регистра 4. В блоке 5 по сигналу КЗ 1 на выходах С1 и С2 появляется синхроимпульс СИА и поступает на синхровходы регистра 2 сдвига и регистра 4 соответственно. По заднему фронту этого синхросигнала происходит сдвиг влево на один разряд в обоих регистрах. При этом в младший разряд регистра 2 сдвига занесется выход регистра 4, соответствующий значению разряда А57 после первого сдвига.

При поступлении по входу 15 устройства синхроимпульса СИ5 в блоке 5 по сигналу К4 О блокируется передача синхроимпульса СИ5 на выходы С1 и С2, и следовательно, на синхро- входы регистра 2 сдвига и регистра 4.

Таким образом, сдвиг на 14 разрядов вправо осуществлен путем сдвига на 16 разрядов (2 байта) вправо, а затем сдвигом этого значения на 2 разряда в противоположную сторону (влево).

Циклический сдвиг выполняется аналогично арифметическому. Отличие состоит в подаче на выходы коммутатора 8 не выходов регистра 4, а выходов и старшего разряда регистра 2 сдвига на выход старшего разряда в случае циклического сдвига влево, или младшего разряда регистра 2 сдвига на выход младшего разряда при.циклическом сдвиге вправо при W О, либо наоборот, при W 1.

Покажем осуществление устройством сдвига в дополнительном коде на примере сдвига в дополнительном коде влево на 10 и 13 разрядов.

Рассмотрим сдвиг в дополнительном коде влево на 10 разрядов. Код сдвига задается кодом 001 по входу

12устройства и кодом 010 по входу

13устройства. Общий код сдвига 0010102, При сдвиге в дополнительном коде должен быть осуществлен сдвиг на 110110 разрядов, т.е. на 6 байтов и 6 разрядов,

I

Код типа сдвига с входа 14 устройства поступает в блок 3 управления, в котором вырабатывается управляющий сигнал Х4 - 1. Сигнал Х4 поступает на элемент И 10 (если бы старщие разряды кода сдвига были все равны логической единице, то по СИ1 на блоке 1 сдвига сдвиг в дополнительном коде, задаваемый кодом, в котором ST2 О, заменился бы сдвигом арифметическим при единичном выходе ST2 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11. Это связано с тем,что при подаче на вход кода сдвига блока 1 сдвига всех единиц при сдвиге в дополнительном коде на его выходе будут все единицы, и окажется потерянной информация о старшем или младшем байтах сдвигаемой информаци При замене при первом сдвиге типа сдвига в дополнительном коде на тип сдвига арифметический эта информация сохраняется указанным способом. Поскольку код на входе 12 старших разрядов кода сдвига устройства не равен 111, то происходит передача кода типа сдвига без преобразования с входа 14 устройства на вход типа сдвига блока 1 сдвига.

Шифратор 6 кода сдвига, с учетом значения Х4 1, вырабатывает код на коммутатор 7, равный для данного примера 0,10, и управляющий сигнал, равный единице. По сигналу с учетом типа сдвига влево в блоке 3 управления вырабатываются сигнлы XI 1, Х2 О и ХЗ 0. На выходах S4 и S3 блока 3 управления вырбатываются нулевые сигналы.

По коду 010 с входа 13 устройства с учетом сигнала Х4 1 на выходах К1 - К4 шифратора 64 вырабатывается код 1100 соответственно.

При поступлении по входу 15 устройства синхроимпульса СИ1 на выходы 55первого сдвига на нем, а на выходе коммутатора 7 будет передан код с вы-младшего разряда регистра 4 появит- хода шифратора 6, которьй таким об-ся значение разряда А6. разом поступает на входы младших раз- При поступлении по входу 15 уст- рядов кода сдвига блока 1 сдвига.ройства синхроимпульса СИ4 в блок

и ,

9196210

Код 010 задает в дополнительном коде сдвиг входной информации с учетом типа сдвига влево н.а 6 байтов. В блоке 3 управления указанным способом 5 вырабатываются сигналы S1 1 и S2 1. По состоянию сигнала XI 1 на входы регистра 4 сдвига подаются выходы А4 - А7 второй тетрады информационных бит. По заднему фронту син- хросигнала СИ1 в регистр 4 сдвига будут приняты выходы А4 - А7 второй тетрады информационных бит блока 1, а в регистр 2 сдвига - сдвинутая на 6 байтов влево с 1 в шести младших байтах информация.

При поступлении по входу 15 уст- ;ройства синхроимпульса СИ2 на вход ;младших разрядов кода сдвига блока 1 сдвига подается код сдвига 001 с входа 12 устройства- через коммутатор 7. В блоке 3 управления по W 1 сохраняется значение сигналов S1 1 и. S2 1. В блоке 5 по коду К1 1 на выходе С1 появляется синхросигнал СИ2, а на выходе С2 - нет.

По заднему фронту синхроимпульса СИ2 происходит прием в регистр 2 сдвига сдвинутой на 7 байтов влево с 1 младших байтах информации .

15

20

25

30

При постугшении по входу 15 устройства синхроимпульса СИЗ в блоке 3 управления триггер 38 сохранит

свое состояние 1, а триггер 39 сбросится в О, т.е. установится код 10 сдвига вправо информации в регистре 2 сдвига и регистре 4 сдвига. Выход младшего разряда регистра

) на котором находится значение разряда А7 выхода блока 1 сдвига, через коммутатор 8 поступает на вход сдвига вправо регистра 2 сдвига. В блоке 5 по сигналу К2 1

на выходах С1 и С2 появляется синхроимпульс СИЗ и поступает на синхро- входы регистра 2 сдвига и регистра Д. ;По заднему фронту СИЗ произойдет 1СДВИГ вправо на один разряд в обоих

регистрах. При этом в старший разряд регистра 2 сдвига занесется младший разряд выхода сдвигающего регистра 4, соответствующий значению разряда А7 выхода блока 1 после

3управления состояние триггеров 38 и 39 изменяется, В блоке 5 по сигналу КЗ 1 на выходах С1 и С2 появляется синхроимпульс СИ4. По его заднему фронту происходит сдвиг впр во на один разряд в обоих регистрах При этом в старший разряд регистра

2сдвига занесется выход регистра 4, соответствующий значению разряда А6 выхода 1 блока 1 после первого сдвига.

При поступлении по входу 15 устройства синхроимпульса СИЗ в блоке 5 по сигналу К4 О блокируется передача синхроимпульса СИ5 на выходы С1 к С2,и, следовательно, на синхро входы регистра 2 сдвига и регистра

4сдвига. I

Таким образом, сдвиг на 54 разря да (6 байтов и 6 разрядов) произведен путем сдвига на 56 разрядов (7 байтов), а затем сдвигом на два разряда в противоположную сторону.

Рассмотрим сдвиг в дополнитель- ном коде влево на 13 разрядов. Величина сдвига задается кодом 001 по входу 12 устройства и кодом 101 по входу 13 устройства.

Общий код сдвига 0011101. При сдвиге в дополнительном коде должен быть осуществлен сдвиг на 110011 разрядов, т.е. на 6 байтов и 3 разряда .

В блоке 3 управления по коду ти- па сдвига вырабатывается управляющий сигнал Х4 1. Происходит перед ча кода типа сдвига без преобразования с входа 14 устройства на вход типа сдвига блока 1, С выхода шифра тора 6 кода сдвига на коммутатор 7 поступает код, равный 010, а в блок

3управления в блок 5 вьщается сигнал W О, По коду 101 с входа 13 устройства с учетом сигнала Х4 1 на выходах шифратора 64 К1 - К4 вырабатывается код 1110 соответственно.

При поступлении по входу 15 устройства синхроимпульса СИ1 на выходы коммутатора 7 передается код 010. По этому коду с учетом типа .сдвига информации сдвинется в бло- , ке 1 сдвига на шесть байтов влево, р блоке 3 управления вырабатывается сигнал Х5 1 и S1 1,52 1. По состоянию сигнала Х5 1 на входы регистра 4 сдвига подаются сигналы логической единицы с выходов элемен

O

5

0

5

0

5 0

тов ИЛИ 50 - 53, По заднему фронту синхроимпульса СИ1 в регистр 4 сдвига принимаются логические единицы, а в регистр 2 сдвига - сдвинутая на 6 байт влево с 1, в шести младших байтах информация.

При поступлении по входу 15 устройства синхроимпульса СИ2 в блоке 3 управления триггер 38 сбрасывается в О, а триггер 39 остается в состоянии 1, по переднему фронту синхроимпульса, т.е. на шинах 1 и 2 установится код 01 сдвига влево информации- в регистрах 2 и 4 сдвига. На выходе старшего разряда регистра 4 будет логическая 1, Этот выход через коммутатор 8 поступает на вход сдвига влево регистра 2 сдвига. В блоке 5 по сигналу К1 1 на выходах С1 и С2 появляется синхроимпульс СИ2 и поступает на синхровходы регистра 2 сдвига и регистра 14 соответственно. По заднему фронту этого синхросигнала происходит сдвиг влево на один разряд в обоих регистрах. При этом в освобождающийся младший разряд регистра 2 сдвига занесется 1 с выхода регистра 4 сдвига.

При поступлении по входу 15 устройства синхроимпульсов СИЗ и СИ4 состояние триггеров 38 и 39 в блоке 3 управления не изменяется, задавая до конца операции сдвиг влево. Поскольку сигналы К2 и КЗ в состоянии 1, то в регистре 4 и регистре 2 сдвига произойдет еще два сдвига, в результате чего информация в регистре 2 сдвига окажется сдвинутой на 6 байтов и 3 разряда влево. Младшие 51 разрядов будут заполнены 1.

При поступлении по входу 15 устройства синхроимпульса СИ5 в блоке 5 по сигналу К4 О блокируется пере- 5 дача синхроимпульса СИ5 на выходы С1 и С2, т,а, на сихровходы регистра 2 сдвига регистра 4 сдвига.

Операции типа распространения знака по всем выходам и блокировка выходов, задаваемые кодами ST2 - STO 000 и 001 по входу 14 устройства, выполняются в блоке 1 сдвига. Выход блока 1 сдвига принимается по заднему фронту синхроимпульса СИ1 в регистр 2 сдвига, В блоке 5 сигнал логического О на выходе элемента ИЛИ 57 блокирует передачу на выходы С1 и С2 синхросигналов СИ2 - СИЗ, и информация в регистре 2 сдвига до

0

5

131291962

онца операции останется без изме- ения.

сд га пе хр до до ра со ро ед к с к х м с к п е п и н и с м ч к в

Формула изобретения

1. Устройство для сдвига информации, содержащее комбинационный блок сдвига, регистр сдвига, блок синхронизации и блок управления, со- держащий шесть элементов И, четыре элемента ИЛИ, два триггера и элемент НЕ, причем информационный вход устройства соединен с информационным входом комбинационного блока сдви- га, выход которого соединен с информационным входом регистра сдвига, информационный выход которого является выходом устройства, вход знака которого, соединен со знаковым разрядом информационного входа комбинационного блока сдвига, младшие .разряды входа типа сдвига которого соедине«ы с входом типа сдвига устройства, разряды тактового входа которого соединены с информационным входом блока синхронизации и соответственно с единичным входом первого триггера, с первыми входами первого и второго элементов И блока управления, выходы первого и второг триггеров которого соединены соответственно с первым и вторым входами типа сдвига регистра сдвига, тактовый вход которого соединен с пер- вым выходом блока синхронизации,причем в блоке управления выходы первого и второго элементов И соединены через первый элемент ИЛИ с нулевым входом первого триггера, единичный вход которого соединен с единичным входом второго триггера, выходы третьего и четвертого элементов И соединены через второй элемент ИЛ1 с нулвым входом второго триггера, о т - личающееся тем, что, с целью повьш1ения быстродействия, он содержит три коммутатора,буферный регистр сдвига, шифратор кода сдвига, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а блок управления содержит дешифратор, элементы ИЛИ с пятого по седьмой, элементы И с седьмого по двенадцатый, причем входы старших и младших разрядов кода сдвига устройства соединены с информационным входом шифратора кода сдвига, вход разрешения которого соединен со старшим разрядом входа кода

14

сдвига комбинационного блока сдвига, первым входом элемента И - с перпым управляющим входом блока синхронизации, первым управляющим входом первого коммутатора и с выходом третьего элемента ИЛИ блока управления, вход дешифратора которого соединен с входом типа сдвига устройства, старший разряд которого соединен с первым входом элемента ИС- КЛЮЧМйЦЕЕ ИЛИ, выходы и второй вход которого соединены соответственно со старшим разрядом входа типа сдвига комбинационного блока сдвига и с ву- ходом элемента И, входы которого,кроме первого, соединены соответственно с разрядами входа старших разрядов кода сдвига устройства и с первым разрядом тактового входа устройства, первый и второй разряды которого со- еди нены. со вторым управляющим входом первого коммутатора, первый и второй информационные входы которого соединены соответственно с входом старших разрядов кода сдвига устройства и с информационньлч выходом шифратора кода сдвига, сигнальный выход которого соединен с вторым управляющим входом блока синхронизации и с входом элемента НЕ блока управления, выходы четвертого и пятого элементов ИЛИ которого соединены соответственно с первым и вторым управляющими входами второго коммутатора, первый информационный вход которого соединен с. выходами старшего и младшего разрядо буферного регистра сдвига, информационный вход которого соединен с выходом третьего коммутатора, первый и второй информационные входы которого соединены соответственно с разрядами второй и предпоследней тетрад выхода комбинационного блока сдвига, вход знака устройства соединен с третьим информационным входом третьего коммутатора, управляющие входы которых соединены соответственно с выходами пятого, шестого, седьмого и восьмого элементов И блока управления, выходы первого, второго триггеров которого соединены соответственно с первым и вторым входами типа сдвига буферного регистра сдвига, тактовьй вход которого соединен со вторым выходом блока синхронизации, третий управляющий вход которого соединен с двумя старшими разрядами входа типа сдвига устройства, вход младших разрядов кода сдвига которог

1 3

соединен с четвертым управляющим RX дом блока синхронизации, вьгход первого коммутатора соединен с входом младших разрядов кода сдвига комбинационного блока сдвига, выходы ста шего и младшего разрядов регистра сдвига соединены со вторым информационным входом второго коммутатора, разряды выхода которого соединены соответственно со входами сдвига влево и вправо регистра сдвига, причем в блоке управления выходы, кром двух младших, дешифратора соединены соответственно с первыми входами .шестого и седьмого элементов ИЛИ, девятого, десятого и седьмого элементов И и со вторым входом шестого элемента ИЛИ, первый вход которого единен с первым входом третьего элемента ИЛИ, второй вход которого со- единен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с первыми входами девятого и одиннадцатого элементов И, третий вход шестого элемента ИЛИ соединен с первыми входами десятого и двенадцатого элементов И, третий вход седьмого элемента ИЛИ соединен с первым входом седьмого элемента И, второй вход которого соединени с первым входом восьмого и третьего элементов И, со вторыми входами первого,девятого,двенадцатого элементов И и с выходом элемента НЕ, вход которого соединен с первыми входами четвертого, пятого и шестого эл,емен- тов И, с вторыми входами второго, десятого и одиннадцатого элементов И, выход шестого элемента ИЛИ соеди

,

нен со вторыми входами пятого и чет вертого элементов И и с третьим входом первого элемента И, первый вход которого соединен со вторым входом третьего элемента И, третий вход ко,

торого соединен с третьим входом второго элемента И, вторым входом шестого элемента И и с выходом седьмого элемента ИЛИ, третий вход четвертого элемента И соединен с первым входом второго элемента И, вы-

f5

291

-. -5 о- 203525

30

40

45

0

96216.

ход третьего элемента ИЛИ соединен со вторым входом восьмого элемента И, выходы девятого и десятого элементов И соединены соответственно со входами четвертого элемента ИЛИ, выходы одиннадцатого и двенадцатого элементов И соединены соответственно со входами пятого элемента ИЛИ.

2. Устройство по п,1, отличающееся тем, что блок синхронизации содержит шифратор, пять элементов И, три элемента ИЛИ и эле- мент-.НЕ, причем разряды информационного входа блока синхронизации соединены соответственно с первым входом первого элемента ИЛИ, первыми входами первого, второго, третьего и четвертого элементов И, вторые входы которых соединены с соответствующими выходами шифратора, информационный вход и вход разрешения которого соединены соответственно с четвертым и первым управляющими входами блока синхронизации, второй управляющий вход которого через элемент НЕ соединен с первым вхо- пятого элемента И, второй вход которого соединен с третьими входами элементов И с первого по четвертый и с выходом второго элемента или, входы которого соединены соответственно с разрядами третьего управляющего входа блока синхронизации,, первый и второй выходы которого соединены соответственно с выходами первого и третьего элементов ИЛИ, первый вход первого элемента ИЛИ соединен с первым входом третьего элемента ИЖ, выходы второго, третьего и четвертого элементов И соединены соответственно со вторым, третьим и четвертым входами первого и третьего элементов ИЛИ, пятые входы которых соединены соответственно с выходами первого и пятого элементов И, третий и четвертый входы пятого элемента И соединены соответственно с первым и вторым входами первого элемента И.

От SAQKO 7

Редактор В.Данко Заказ 265/47

Составитель А.Клюев

Техред В.Кадар Корректор с.Черни

„,„ 673 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственно-полиграфическое

9uz.6

предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1978 |

|

SU736106A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для управления ленточным перфоратором | 1981 |

|

SU970402A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повьшение быстродействия. Поставленная цель достигается тем, что устройство, содержащее комбинационный блок сдвига, регистр сдвига, блок синхронизации и блок управления, содержит три коммутатора, буферный регистр сдвига, шифратор кода сдвига, элементы И и ИСКЛЮЧАКИЧЕЕ ИЛИ с соответствующими связями. Изобретение может быть использовано в процессорах малых и средних ЭВМ, вычислительных устройствах и приборах цифровой автоматики. 1 з.п. ф-лы, 6 ил., 3 табл. СО QD Од Ю

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига с контролем | 1984 |

|

SU1238058A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-04-09—Подача