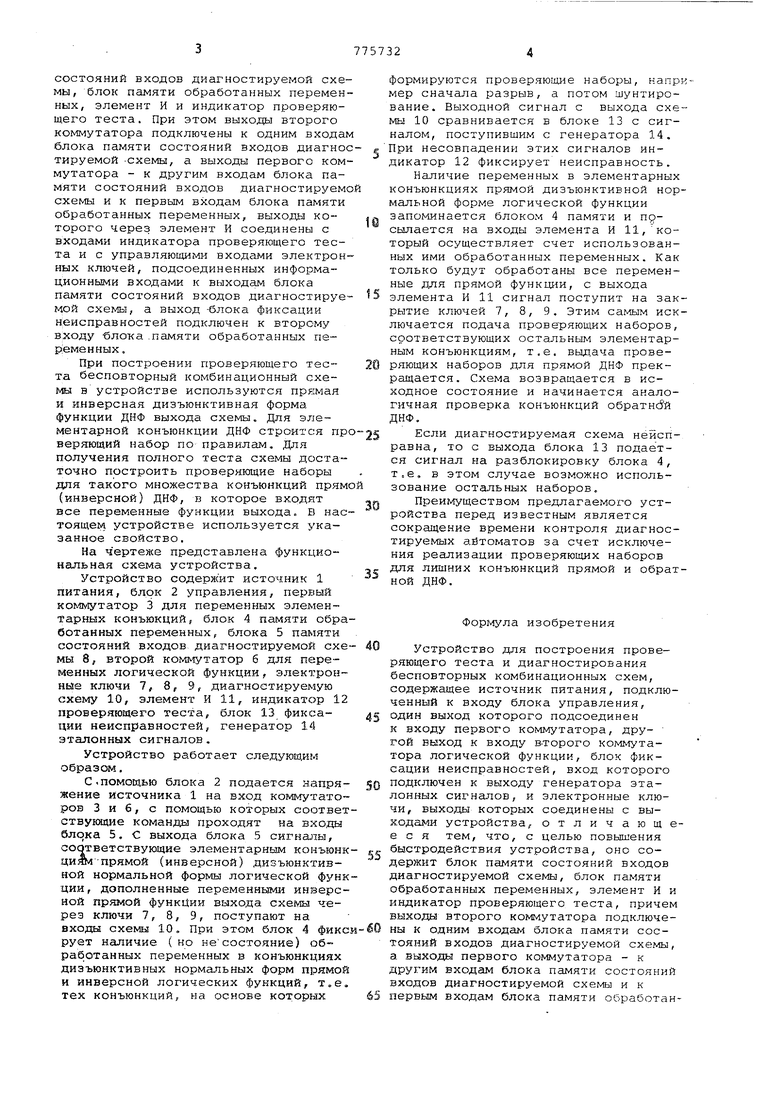

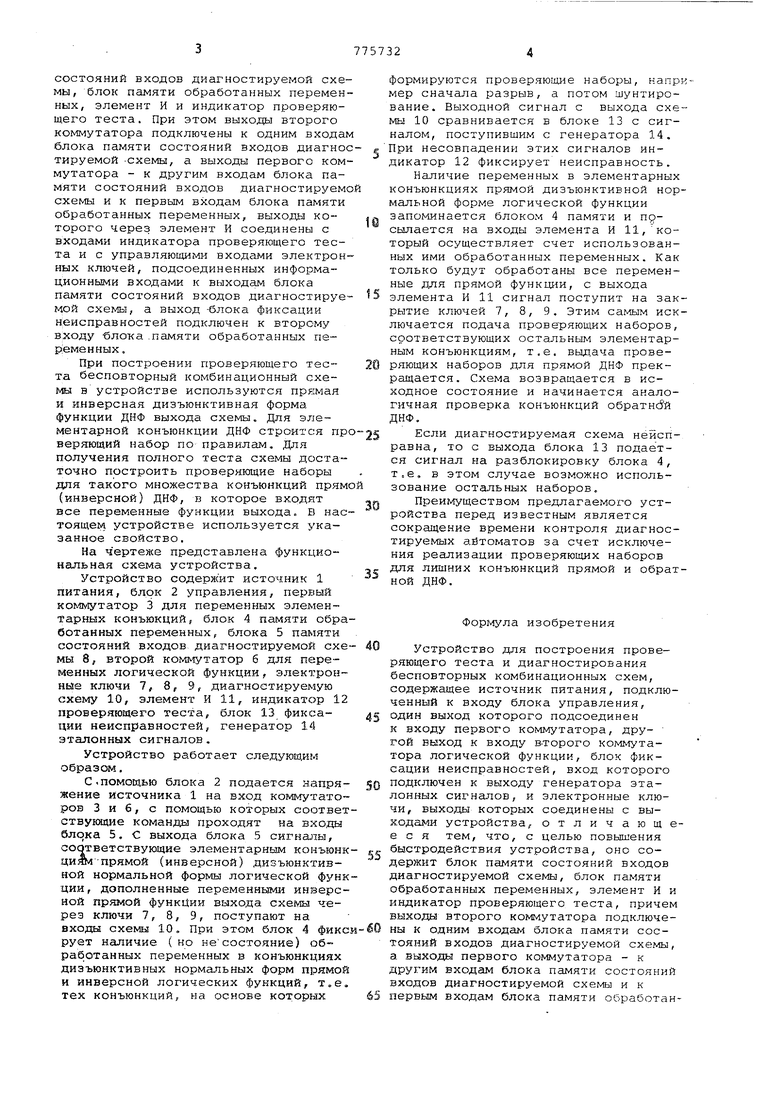

(54) УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОВЕРЯЮЩЕГО ТЕСТА И ДИАГНОСТИРОВАНИЯ БЕСПОРТОРНЫХ КОМБИНАЦИОННЫХ СХЕМ Изобретение относится к автомати ке и контрольно-измерительной технике и может быть использовано при создании автоматических устройств контроля и поиска неисправностей дискретных автоматов. Известно устройство 1 поиска неисправностей логических схем, осно ванное на измерении реакции диагностируемого автомата на наборы теста, вырабатываемого генератором случайных чисел и сравнении ее с сигналом контрольного автомата. Недостатками этого устройства являются большое время контроля, поскольку посылаемые на вход наборы соответствуют случайным числам, а также трудности определения места неисправности, т.е. дешифрация резул контроля. Известно автоматическое устройств контроля и поиска неисправностей 2 основанное на сравнении выходного сигнала диагностируемого автомата на наборах проверяющего и диагностического тестов с эталонным его значением. Недостаток этого устройства большой объем вычислительных операций, связанных с получением диагностического и проверяющего тестов, что приводят к большому времени контроля различных диагностируемых схем. Наиболее близким по технической сущности к изобретению является устройство контроля и поиска неисправностей бесповторных комбинационных схем 3 . Оно содержит источник питания, подключенный к входу блока управления, один выход которого подключен к входу первого коммутатора, а другой, выход - к входу второго коммутатора, блок фиксации неисправностей, вход которого подключен к выходу генератора эталонных сигналов, и электронные клю.чи, выходы которых соединены с выходами устройства. Недостаток данного устройства заключается в том, что для обнаружения логических неисправностей бесповторных комбинационных схем в нем используются избыточные проводящие, наборы, что приводит к большому расходу ресурса диагностируемой схемы и необоснованному увеличению времени диагностирования. Цель изобретения - повышение быстродействия устройства. Указанная цель достигается тем, .что устройство содержит блок памяти состояний входов диагностируемой схемы, блок памяти обработанных перемен ных, элемент И и индикатор проверяющего теста. При этом выходы второго коммутатора подключены к одним входам блока памяти состояний входов диагнос тируемой Схемы, а выходы первого ком мутатора - к другим входам блока памяти состояний входов диагностируем схемы и к первым входам блока памяти обработанных переменных, выходы которого через элемент И соединены с входами индикатора проверяющего теста и с управляющими входами электрон ных ключей, подсоединенных информационными входами к выходам блока памяти состояний входов диагностируе мой схег/и, а выход -блока фиксации неисправностей подключен к второму входу блока .памяти обработанных переменных. При построении проверяющего теста бесповторный комбинационный схеt sti. в устройстве используются прямая и инверсная дизъюнктивная форма функции ДНФ выхода схемы. Для элементарной конъюнкции ДНФ строится пр веряющий набор по правилам. Для получения полного теста схемы достаточно построить проверяющие наборы для такого множества конъюнкций прям (инверсной) ДНФ, в которое вкодя т все переменные функции выхода. В нас тоящем устройстве используется указанное свойство. На чертеже представлена функциональная схема устройства. Устройство содержит источник 1 питания, блок 2 управления, первый коммутатор 3 для переменных элементарных конъюкций, блок 4 памяти обра ботанных переменных, блока 5 памяти состояний входов диагностируемой схе мы 8, второй коммутатор б для переменных логической функции, электронные ключи 7, 8, 9, диагностируемую схему 10, элемент И 11, индикатор 12 проверяющего теста, блок 13 фиксации неисправностей, генератор 14 эталонных сигналов. Устройство работает следующим образом, С помощью блока 2 подается напряжение источника 1 на вход коммутаторов 3 и б, с помощью которых соответ ствующие команды проходят на входы блока 5, С выхода блока 5 сигналы, соответствующие элементарным конъюнк ци,Ф -прямой (инверсной) дизъюнктивной нормальной формы логической функ ции , дополненные переменными инверс ной прямой функции выхода схемы через ключи 7, 8, 9, поступают на входы схемы 10. При этом блок 4 фикс рует наличие (но несостояние) обработанных переменных в конъюнкциях дизъюнктивных нормальных форм прямой и инверсной логических функций, т„е тех конъюнкций, на основе KOTOpiax формируются проверяющие наборы, наприер сначала разрыв, а потом шунтирование. Выходной сигнал с выхода схемы 10 сравнивается в блоке 13 с сигналом, поступившим с генератора 14. ри несовпадении этих сигналов индикатор 12 фиксирует неисправность. Наличие переменных в элементарных конъюнкциях прямой дизъюнктивной нормальной форме логической функции запоминается блоком 4 памяти и пдсьшается на входы элемента И 11, который осуществляет счет использованных ими обработанных переменных. Как только будут обработаны все переменные для прямой функции, с выхода элемента И 11 сигнал поступит на закрытие ключей 7, 8, 9. Этим самым исключается подача проверяющих наборов, соответствующих остальным элементарным конъюнкциям, т.е. выдача проверяющих наборов для прямой ДНФ прекргидается. Схема возвращается в исходное состояние и начинается аналогичная проверка конъюнкций обратной ДНФ. Если диагностируемая схема неисправна, то с выхода блока 13 подается сигнал на разблокировку блока 4, . в этом случае возможно использование остальных наборов. Преимуществом предлагаемого устройства перед известным является сокращение времени контроля диагностируемых айтоматов за счет исключения реализации проверяющих наборов для лишних конъюнкций прямой и обратной ДНФ. Формула изобретения Устройство для построения проверяющего теста и диагностирования бесповторных комбинационных схем, содержащее источник питания, подключенный к входу блока управления, один выход которого подсоединен к входу первого коммутатора, другой выход к входу в-торого коммутатора логической функции, блок фиксации неисправностей, вход которого подключен к выходу генератора эталонных сигналов, и электронные ключи,, выходы которых соединены с выхода и устройства, отличающееся тем, что, с целью повьшения быстродействия устройства, оно содержит блок памяти состояний входов диагностируемой схемы, блок памяти обработанных переменных, элемент И и индикатор проверяющегс теста, причем выходы второго коммутатора подключены к одним входам блока памяти состояний входов диагностируемой схемы, а выходы первого коммутатора - к другим входам блока памяти состояний входов диагностируемой схемы и к первым входам блока памяти обработанных переменных, выходы которого через элемент И соединены с входами индикатора проверяющего теста и с управляющими входами электронных ключей, подсоединенных информационными входами к выходам блока памяти состояний входов диагностируемой схемы, а выход блока фиксации неисправностей подключен к второму входу блока памяти обработанных переменных.

Источники информации, принятые во внимание при экспертизе

1.Патент США №3614608, кл. 32 1-г73, опублик. 1972.

2.Кострыкин А.И. Логический контроль релейно-контактных схем. М.,

Связь, 1970, с. 80-86. .

3.Авторское свидетельство СССР

t 526834, кл. G 06 F 11/02, 06.09.74 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| "Устройство для формирования тес-TOB КОМбиНАциОННыХ лОгичЕСКиХ блО-KOB | 1979 |

|

SU836635A1 |

| Устройство для получения тестов бесповторных комбинационных схем | 1975 |

|

SU570897A1 |

| Устройство для поиска неисправностей бесповоротных комбинационных схем | 1974 |

|

SU526834A1 |

| Устройство для получения диагностических тестов бесповторных комбинационных схем | 1975 |

|

SU550639A1 |

| Устройство для получения минимальных диагностических тестов бесповторных комбинационных схем | 1973 |

|

SU458830A1 |

| Устройство для диагностирования бесповторных комбинационных схем | 1976 |

|

SU684556A1 |

| Устройство для получения диагностических тестов логических блоков | 1977 |

|

SU736103A1 |

| Устройство для получения тестов бесповоротных комбинационных схем | 1974 |

|

SU526895A1 |

| Устройство для формирования тестов бесповоротных комбинационных схем | 1974 |

|

SU607220A1 |

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

Авторы

Даты

1980-10-30—Публикация

1978-07-19—Подача