(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕСТОВ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Устройство для построения проверяющего теста и диагностирования бесповторных комбинационных схем | 1978 |

|

SU775732A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство синтаксически управляемого перевода | 1986 |

|

SU1399767A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1976 |

|

SU748420A1 |

| Устройство для получения тестов бесповторных комбинационных схем | 1975 |

|

SU570897A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

Изобретение относится к автоматике и вычислительной технике и может быт использовано в диагностирующих автоматах и в специализированных устройствах для получения тестов. Известно устройство, предназначенное для формирования тестов дискретных автоматов, содержащее индикатор тестовых наборов, блок управления, коммутатор переменных логической-функ ции и коммутатор элементарных конъюнкций Это устройство предназначено только для бесповторных комбинационных схем и не выделяет тех тестовых наборов, которые отличают данную неисправность от других неисправностей или от исправной схемы. Наиболее близким техническим решением к изобретению является устройство для формирования тестов дискретньпс автоматов, содержащее блок управления, коммутатор переменных логической функции, коммутатор элементарных конъюнкций, дешифратор и индикатор тестовых наборов, причем выход блока управления соединен со входом коммутатора переменных логической функции, выходы которого подключены ко входам коммутатора элементарных конъюнкций, выходы .которого связаны со входами дешифратора, нагрузкой которого является индикатор тестовьпс наборов 2. Это устройство для формирования тестов применимо для повторных комбинационных схем, однако, оно не позволяет определять входящие в диагностический тест наборы, на которых искомая неисправность заданной крат- . ности отличается от других неисправностей или от полностью исправнойсхемы. При этом каждому тестовому диагностического теста нельзя поставить в соответствие неисправность, которую он различает, поэтому oпpe eлeниe таких диагностических наборов оператор должен производить вручную, используя всю эту совокупость наборов, которую индицирует стройство.

Целью изобретения является расшиейие функциональных возможностей за счет формирования тестов, различаюих неисправности любой кратности ля комбинационных логических схем без памяти.

Поставленная цель достигается тем, что в устройство, содержащее блок ю синхронизации, коммутатор элементарных конъюнкций, дешифратор, блок индикации, причем первый выход блока синхронизации соединен со входом коммутатора элементарных конъюнкций, вы- 15 ходы которого соединены со входами дешифратора, введена группа RS-триггеров, регистр и группа сумматоров по модулю два, причем второй, третий и четвертый выходы блока синхрониза- 20 ции соединены соответственно с R-BXOдами RS-триггеров групгаэ), со входом синхронизации регистра и с R-входом регистра. Выходы дешифратора соединены соответственно с S-входами триг- 25 геров группы. Выходы триггеров соединены с соответствующими входами регистра и с первым входом ,с;рответст вующего сумматора по модулю два, выход которого соединен со входом блока зо индикации, выходы регистра соединены со вторыми входами соответствующих сумматоров по модулю два.

Такое устройство позволяет получать тестовые наборы, различающие 35 исправную схему и любые константные неисправности произвольной кратности, необходимые для контроля работоспособности и диагностики класса комбинационных схем.40

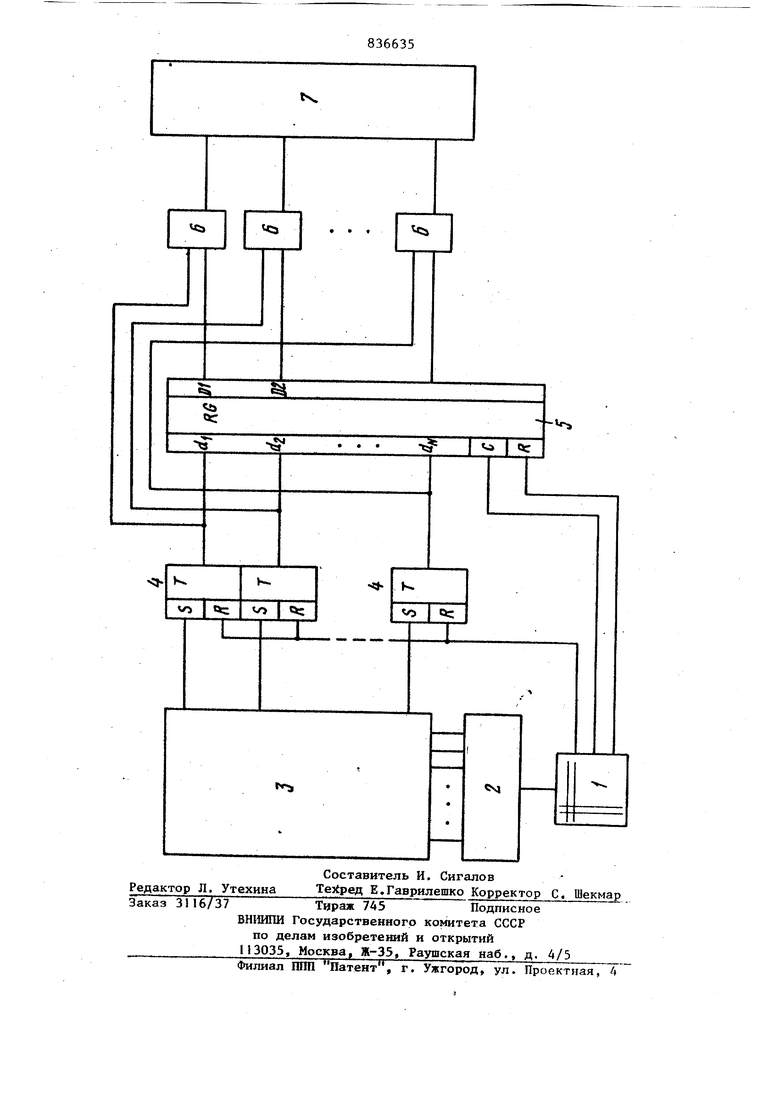

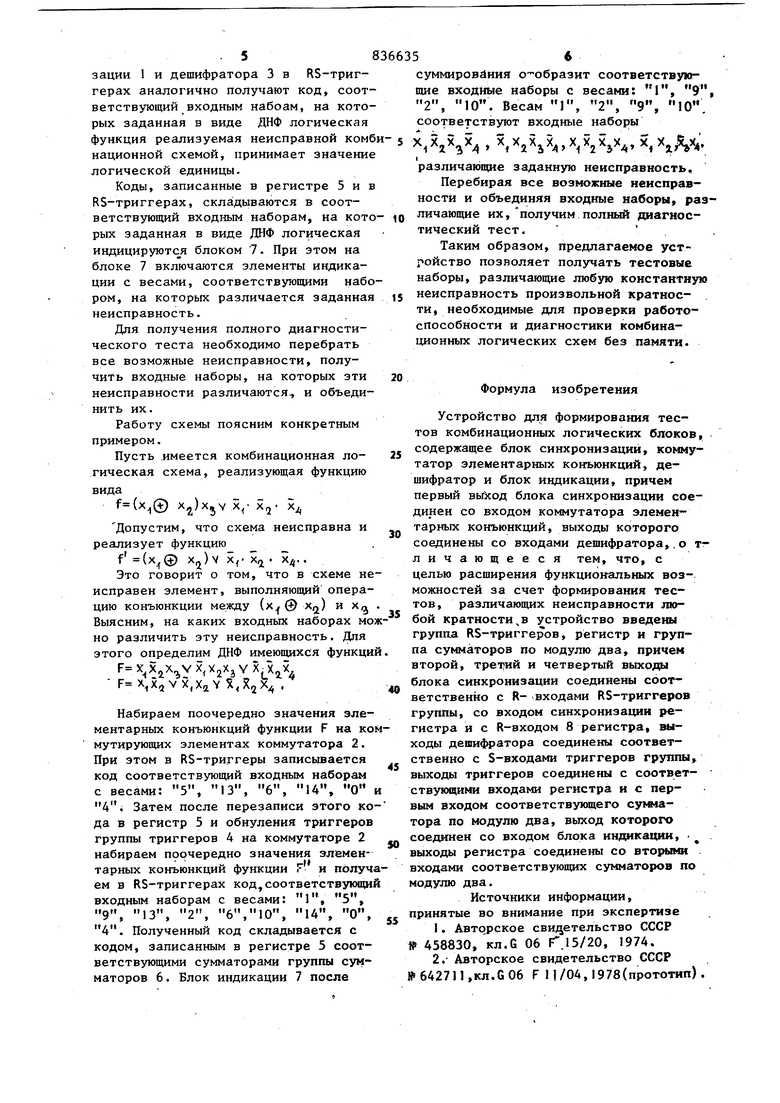

На чертеже изображена функциональная схема устройства для формирования тестов комбинационных логических блоков.

Устройство содержит блок 1 сянхронизации, коммутатор 2 элементарных конъюнкций, дешифратор 3, rpjrany 4 RS-триггеров, регистр 5, группу сумматоров по модулю два 6 и блок инди- jg кации 7.

Первый выход блока синхронизации 1 подключен ко входу коммутатора 2 в1лходы которого соединены со входами дешифратора 3, Вькоды депшфратора 3 свя-55 заны со входами S-группы и RS-триггеФов. Выход каждого триггера группы подключен к первым входам соответстBjropero сумматора группы 6 и ко.

входам D регистра 5. Выходы регистра 5 соединены со вторыми входами соответствующих сумматоров группы 6, выходы которых связаны со входами блок индикации 7. Входы С и R регистра 5, также как и объединенные меясду собой входы R группы триггеров 4 подключены к соответствующим выходам блока синхронизации 1.

Устройство работает следующим образом.

В исходном состоянии в RS-триггерах группы триггеров 4 в регистре 5 записаны нули, а все коммутирующие .элементы коммутатора 2 находятся в выключенном состоянии.

Каждому коммутирующему элементу коммутатора 2 сопоставляются переменные X , t 1 12 J П

логической функции, реализуемой диагностируемой комбинационной схемой, индицирующим элементам блока 7 - вес состояний наборов 0,1,2,... (), где п- число переменных функций.

Определяются дизъюнктивные нормальные формы (ДНФ логической функции, реализуемой исправной комбинационной схемой, и логической функции реализуемой этой же схемой в неисправном состоянии.

Для определения тестовых наборов, выявляющих заданную неисправность, с помощью коммутирующих элементов комутатора 2 поочередно набираются все переменные каждой элементарной конъюкции, входящей в состав ДНФ логической функции, реализуемой исправной комбинационной схемой. После набора каждой элементарной конъюнкции на коммутатор 2 подается сигнал от блока синхронизации 1, при этом в RSтриггеры группы триггеров 4 записывaefcя код, соответствующий входным наборам, на которых заданная конъюнкция принимает значение логической единицы. В конечном итоге, после перебора всех элементарных конъюнкций в RS-триггерах будет записан код,соответствующий входным наборам, на которых заданная в виде ДНФ функция принимает значения логической единицы.

Полученный в RS-триггерах группы код по сигналу с блока J синхронизации переписывается в регистр 5. После этого все RS-триггеры устанавливаютсз в исходное нулевое состояние.

Затем с помощью коммутирующих элементов коммутатора 2 блока синхрони. 5 зации 1 и дешифратора 3 в RS-триггерах аналогично получают код, соот ветствующий входным набоам, на кото рых заданная в виде ДНФ логическая функция реализуемая неиспра:вной ком национной схемой, принимает значени логической единицы. Коды, записанные в регистре 5 и RS-триггерах, складываются в соответствующий входным наборам, на кот рых заданная в виде ДНФ логическая индицируются блоком 7. При этом на блоке 7 включаются элементы индикации с весами, соответствующими набо ром, на которых различается заданная неисправность. Для получения полного диагностического теста необходимо перебрать все возможные неисправности, получить входные наборы, на которых эти неисправности различаются, и объединить их. Работу схемы поясним конкретным примером. Пусть имеется комбинационная логическая схема, реализующая функцию вида X.V X, Допустим, что схема неисправна и реализует функцию f( X,j)V Xf- Х,; Х. . Это говорит о том, что в схеме не исправен элемент, выполняющий операцию конъюнкции между (х ф Xf) и х Выясним, на каких входных наборах мо но различить эту неисправность. Для этого определим ДНФ имеющихся функци ,,X2XjYX.j(A F Х.Ха Y Набираем поочередно значения элементарных конъюнкций функции F на ко мутирующих элементах коммутатора 2. При этом в RS-триггеры записывается код соответствующий входным наборам с весами: 5, 13, 6, 14, О 4. Затем после перезаписи этого ко да в регистр 5 и обнуления триггеров группы триггеров 4 на коммутаторе 2 набираем прочередно значения элементарных конъюнкций функции F и получ ем в RS-триггерах код,соответствующи ticll входным наборам с весами: 1 - Или 9, 13, 2, 6,10, 14, О 4. Полученный код складывается с кодом, записанным в регистре 5 соответствующими сумматорами группы сумматоров 6. Блок индикации 7 после 5 суммировйния о образит соответствующие входные наборы с весами: 1, 9, 10. Весам Г соответствуют входные наборы , различающие заданную неисправность. Перебирая все возможные неисправности и объединяя входные наборы, различающие их, получим полный диагностический тест. Таким образом, предлагаемое устройство позволяет получать тестовые наборы, различающие любую константную неисправность произвольной кратности , необходимые для проверки работоспособности и диагностики комбинационных логических схем без памяти. Формула изобретения Устройство для формирования тестов комбинационных логических блоков, содержащее блок синхронизации, коммутатор элементарных конъюнкций, дешифратор и блок индикации, причем первый вьйсод блока синхронизации соединен со входом коммутатора элементарных конъюнкций, выходы которого соединены со входами дешифратора,,о тличающееся тем, что, с целью расширения функциональных возможностей за счет формирования тестов, различающих неисправности любой кратности в устройство введены групп.а RS-триггеров, регистр и группа сумматоров по модулю два, причем второй, третий и четвертый выходы блока синхронизации соединены соответственно с R- входами RS-триггеров группы, со входом синхронизации регистра и с R-входом 8 регистра, выходы дешифратора соединены соответственно с S-входами триггеров группы, выходы триггеров соединены с соответствующими входами регистра и с первым входом соответствующего суынатора по модулю два, выход которого соединен со входом блока инда1кацш{, выходы регистра соединены со вторыми входами соответствующих сумматоров по одулю два. Источники информации, ринятые во внимание при экспертизе 1. Авторское свидетельство СССР P 458830, кл.а 06 Г.15/20, 1974. 2. Авторское свидетельство СССР 642711,кл.а 06 F И/04,1978(прототип).

ш

о I «

v

f«

«

м

Авторы

Даты

1981-06-07—Публикация

1979-07-03—Подача