(54) СХЕМА СРАВНЕНИЯ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Схема сравнения кодов | 1982 |

|

SU1016778A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Схема сравнения кодов | 1988 |

|

SU1522192A2 |

| Устройство для вычисления булевых дифференциалов | 1980 |

|

SU940166A1 |

| Устройство для вычисления булевых производных | 1982 |

|

SU1128263A1 |

| Устройство для сравнения кодов | 1983 |

|

SU1103220A1 |

| Устройство для вычисления булевых производных | 1985 |

|

SU1277089A1 |

| Устройство для вычисления булевых производных | 1987 |

|

SU1481793A1 |

| Устройство для вычисления булевых производных | 1986 |

|

SU1370651A1 |

| Схема сравнения кодов | 1988 |

|

SU1599852A2 |

t

ИзоОретение относится к области автомати и и вычислительной техники и предназначено для автоматизации процесса вычисления булевой разности при проектировании сре;цств тестового и аппаратурного контроля комбинационных схем.

Известна схема сравнения кодов, содержащая .элементы ИЛИ-НЕ едостатком ее является невозможность вычисления булевой разности.

Наиболее близким техническим решением к данному является схема сравнения кодов, содержащая регистр и группу элементов неравнозначность, первые входы которых являются входами первой группы схемь 2. Схема содержит, кроме того, элемент ИЛИ.

Недостатком ее является невозможность вычисления булевой разности.

Целью изобретения является расширение функциональных возможностей за счет вычисления булевой разности.

Цель достигается тем, что в схему введены счетчик, два коммутатора, элемент неравнозначность, дешифратор, группу элементов И, причем выходы счетчика соединены со вторыми входами элементов неравнозначнсУсть группы, с входами дешифратора и управляющими входами первого коммутатора, информационные входы которого являются входами второй группы схемы и соединены с информационными входами второго коммутатора, управляющие входы которого соединены с выходами элементов неравнозначность ,группы, а выходы первого и второго коммутаторов соединены с первым и

10 вторым входами элемента неравнозначнрсть, выход котор ого подключен к первым входам элементов И группы, вторые входы которых соединены с соответствующими выходами дешифратора, а выходы подключены к входам реги15Ътра, выходы которого являются выходами схемы.

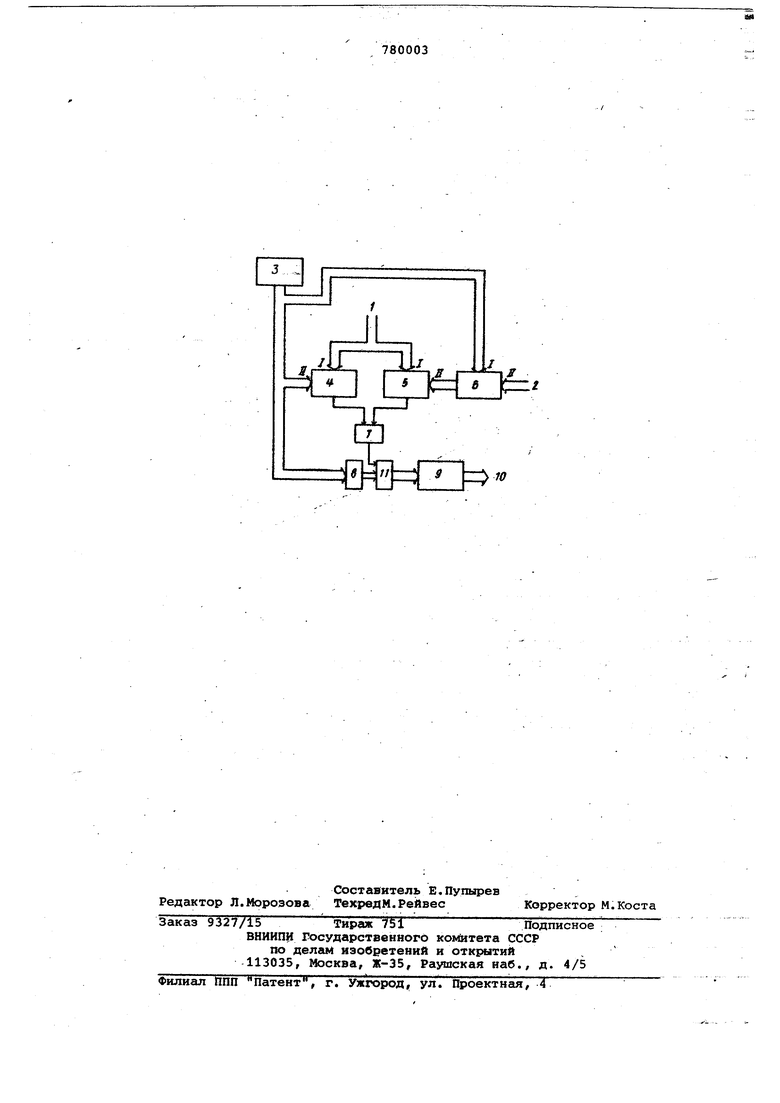

Схема представлена на чертеже. Схема содержит входы 1 схемы второй группы, входы 2 первой группы

20 схемы, счетчик 3, первый коммутатор 4, второй коммутатор 5, группу 6 элементов неравнозначность, элемент неравнозначность 7, дешифратор 8, регистр 9, выходы 10 схемы, группу

25 -11элементов И.

Коммутаторы 4 и 5 имеют п управляющих входов, 2 информационных входов , один выход состоит из п-входового дешифратора, 2 двухвходовых

30

схем И, сщной 2 -входовой схемы ИЛИ и предназначены для выбора на основании управляющего двоичного кода (П) соответствующего разряда из информационного.двоичного кода.

Рассмотрим работу булевой схемы.

По определению булевой разностью логической функции F (х , . . .,х,) по переменной х называется логическая функция R{x,. . . ,Xf,) вида R{x.,. . . , х)(х , . . . , . . . ,х)ФР(х , . . .X,-, ...,хи). То есть для вычисления функции R(х ,...,х) необходимо вычислять значение функции F на наборе X ,... , х ,., . , X у, и сложить по модулю два со значением исходнойфункции на рассматриваемом наборе.

Значения исходной функции на всех двоичных наборах., входных переменных (таблица истинностц функции) подаются на входы 1.

На входы 2 подается п-разрядный двоичный код, несущий информацию о . , по переменным вычисляется булевая разность. Если она вычисляется по переменной х , то в i -м разряде двоичного кода будет 1, втз Всех остальных разрядах - О. Например, для , при вычислении булевой разности по переменной х двоич{}ый код имеет вид 100.

Счетчик 3 формирует последователь- нрсть двоичных наборов (двоичных слов). Для каждого набора производится определение значения исходной функции на данном (на выходе коммутатора 4) , в группа 6 на основаййи управлякядего кода формируется набор х ,. . .ху,.. .„, и определяется значение исходной функции на этом наборе (на выходе коммуУатора 5). Элемент неравяоЗначЕНОСТь 7 производит, сложение по модулю два значений функции на наборах х,...«

X; , ... х у, и х , . . . , . 4 . I f.

Результат сложения поступает на перёые входы элементов И rpynrw 11 В зависимости от рассматрйваешго двоичного набора (пойтупаймчего с йвоич-; ного счетчика 3) вйдаефся то соотвег cтвyШё 4y выходу в регистр ; ;-..-;.

После рассмЬтренмя всех набЬрёв в регистре сформирована булевая разность . Устройство работает аналогично в случае; вычисления булевой разности по нескольким переменный.

Рассмотрим пример работы устройства для . Пусть 3:адана исходная функцияf таблица ИСТИННОСТИ которой приведена в табл. Необходимо вычислить булевую разность lio переменной х. Двоичный код, поступающий на входы 1, имеет вид 01111010,

а двоичный код, поступаквдий на входы 2 имеет .вид 010.

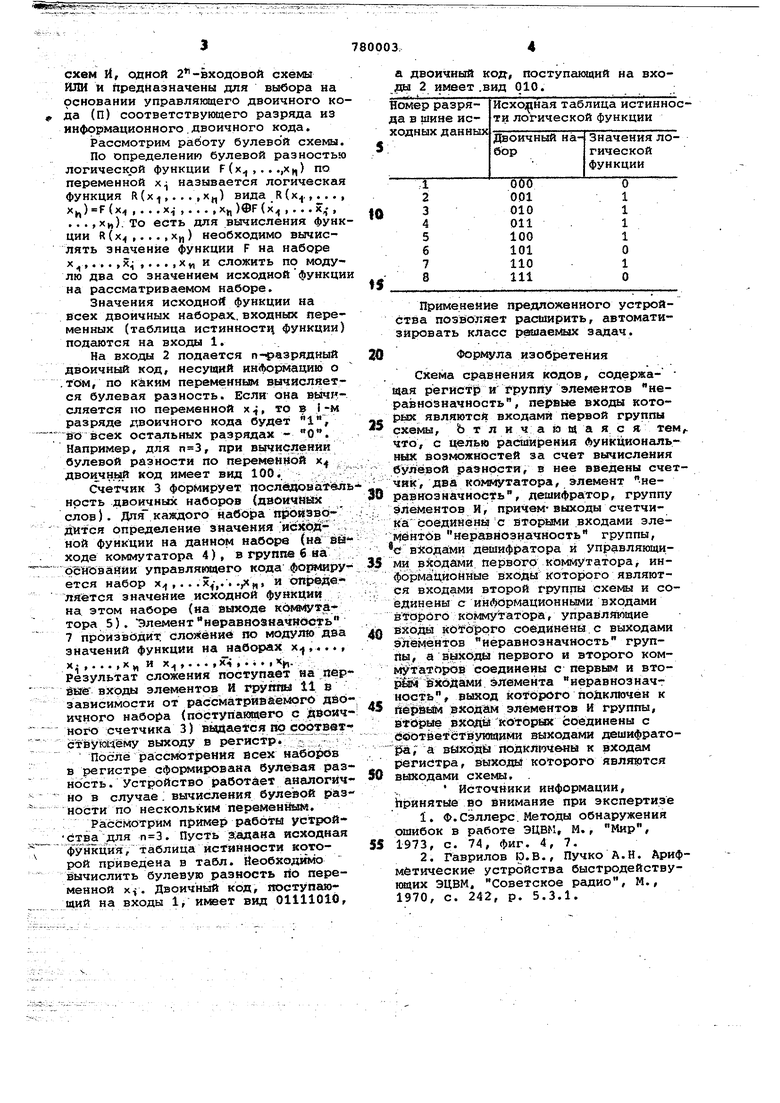

Исхо;рная таблица истинности ло1ической функции

Значения лодаоичный нагическойбор функции

оио

О 1 1 1 1 О 1 О

001 010 011 100 101 110 111

Применение предложенного устройства позволяет расширить, автоматизировать класс решаемых задач.

Формула изобретения

Схема сравнения кодов, содержа- щая регистр и группу элементов неравнозначность, первые входы которых являютсй входами первой группы

5 схемы, Ь т л и ч а ю щ а я с я тем,, что, с целью расширения функциональных возможностей за счет вычисления булевой разности, в нее введены счетчик, два ко Ф4утатора, элемент не0 равнозначность, дешифратор, группу элементов И, причем-выходы счетчика соединены с вторыми входами элементов неравнозначность группы, е входами дешифратора и Управляющими входами первого коммутатора, информационные входы которого являются входами второй группы схемы и соединены с инАормационными входами второго коммутатора, упрайля1ощие

входы которого соединены с выходами элементов неравнозначность группы, а выхода первого и второго комМУтатороа соединены с первым и вторШ &х6йамй элемента неравнозначность выход йойключен к

5 liEepi t ВХОДИМ элементов И группы,

втЬрьае вхойй которых соединены с е 1бот6етбтвуювдими выходами дашифратоga; а находи nojBiKJin4eHa к входам регистра, выходы которого являются выходами схемы. .

Источники информации, Ьринятые во внимание при экспертизе

Авторы

Даты

1980-11-15—Публикация

1978-12-19—Подача