ь

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств тестового и аппаратурного контроля цифровых устройств.

Известна схема сравнения кодов, 5 содержащая элементы НЕРАВНОЗНАЧHOCTb(;i.

Недостаток известной схемы состоит в невозможности вычисления булевой разности.10

, Наиболее близкой к предлагаемой является схема сравнения кодов, содержащая регистр, группу элементов НЕРАВНОЗНАЧНОСТЬ,счетчик, два коммутатора, элемент НЕРАВНОЗНАЧ- S НОСТЬ, дешифратор, группу элементов И, при этом выходы счетчика соединены с вторыми входами элементов НЕРАВНОЗНАЧНОСТЬ группы,с входами дешифратора и управляющими входами вого коммутатора, информациойные входы которого явлзчются входами второй группы схемы и соединены с информационными входами второго коммутатора, -управляющие входы которого соеди-25 нены с выходами элементов НЕРАВНОЗНАЧНОСТЬ группы, первые входы которых являются входами первой группы схемы, а выхода первого и второго коммутаторов соединены с первым и вторым входами элемента НЕРАВНОЗНАЧНОСТЬ, 30 выход которого подключен к первым входам элементов И группы, вторые входы которых соединены с соответствующими выходами дешифратора, а выходы подключены к входам регистра, 35 выходы которого являются выходами схемы 21.

Недостатком данной схемы сравнения кодов является сложность уст- , ройства, поскольку требуется дешифра-40 тор с числом выходов 2 JJ акое же-число элементов И, где п-число переменных, от которых зависит исходнаяфункция, а также большое число связей между дешифратором, группой д элементов И и регистром, причем в каждом такте информация передается только по одной из этих связей.

Цель изобретения - упрощение схе№1 сравнения кодов.чп

Поставленная цель достигается тем, что схема сравнения кодов, содержащая счетчик, коммутаторы, группу элементов НЕРАВНОЗНАЧНОСТЬ, элемент НЕРАВт НОЗНАЧНОСТЬ, причем входы первой группы схемы подключены соответственно к 55 информационным входам коммутаторов, управляющие входы первого коммутатора подключены соответственно к выходам счетчика, управляющие входы второго коммутатора подключены к выходамбО элементов НЕРАВНОЗНАЧНОСТЬ группы, . первые входы кЪторых подключены соответственно к выходам счетчика, вторые входы элементов НЕРАВНОЗНАЧНОСТЬ подключены к входам второй группы схе- 5

мы, выходы коммутаторов подключены соответственно к входам элемента НЕ,РАВНОЗНАЧНОСТЬ, содержит сдвиговый регистр, причем выход элемента НЕРАВНОЗНАЧНОСТЬ подключен к информационному входу сдвигового регистра, управляющий вход которого подсоединен . к входу счетных импульсов схемы и счетному входу счетчика.

На чертеже показана структура схемы сравнения кодов.

схема содержит входы 1 схемы первой группы, входы 2 схемы второй группы, счетчик,3, коммутаторы 4 и 5, группу элементов НЕРАВНОЗНАЧНОСТЬ 6, элемент НЕРАВНОЗНАЧНОСТЬ 7, сдвиговый регистр 8, выходы 9 схемы, вход 10 счетных импульсов.

Схема работает следующим образом.

В исходном состоянии счетчик 3 находится в нулевом состоянии. Значение исходной функции на всех двоичных наборах входных переменных (таблица истинности) подается на входы .

На входы 2 подается п-разрядный двоичный код, несущий информацию о том, по каким переменным вычисляется булева р,азно.сть. При вычислении булевой разности по переменной х- в 1-м разряде кода - единица,в остальных - нули..

При подаче .счетных импульсов на вход 10 счетчик формирует последовательность двоичных наборов. На каждом из них производится определение значения функции с помощью коммутатора 4. В группе элементов НЕРАВНОЗНАЧНОСТЬ б по н.абору, поступающему со счетчика 3, и коду переменной, поступающему на входы схемы, формируется второй набор, на котором определяется значение функции с помощью коммутатора 5. На выходе элемента НЕРАВНОЗНАЧНОСТЬ 7 формируется значение

булевой разности, поступающее на информационный вход сдвигового регистра 8, выходы 9.которого являются выходами схемы.

По окончании счетного импульса значение булевой разности запишется в сдвиговый регистр 8, а счетчИк 3 изменит свое состояние на единицу. После подачи 2 счетных импульсов счетчик 3 возвратится в исходное состояние, а процесс вычисления болевой разности будет закончен.

Работа схемы иллюстрируется примером, приведенным в табл.1 и 2.

Воспользуемся для оценки сложности данной схемы и схекы прототипа числом входовв логические элементы (оценкапо Квайну) . Тогда, сложность схемы-прототипа S определится по .формуле

+2«2 +П+С,

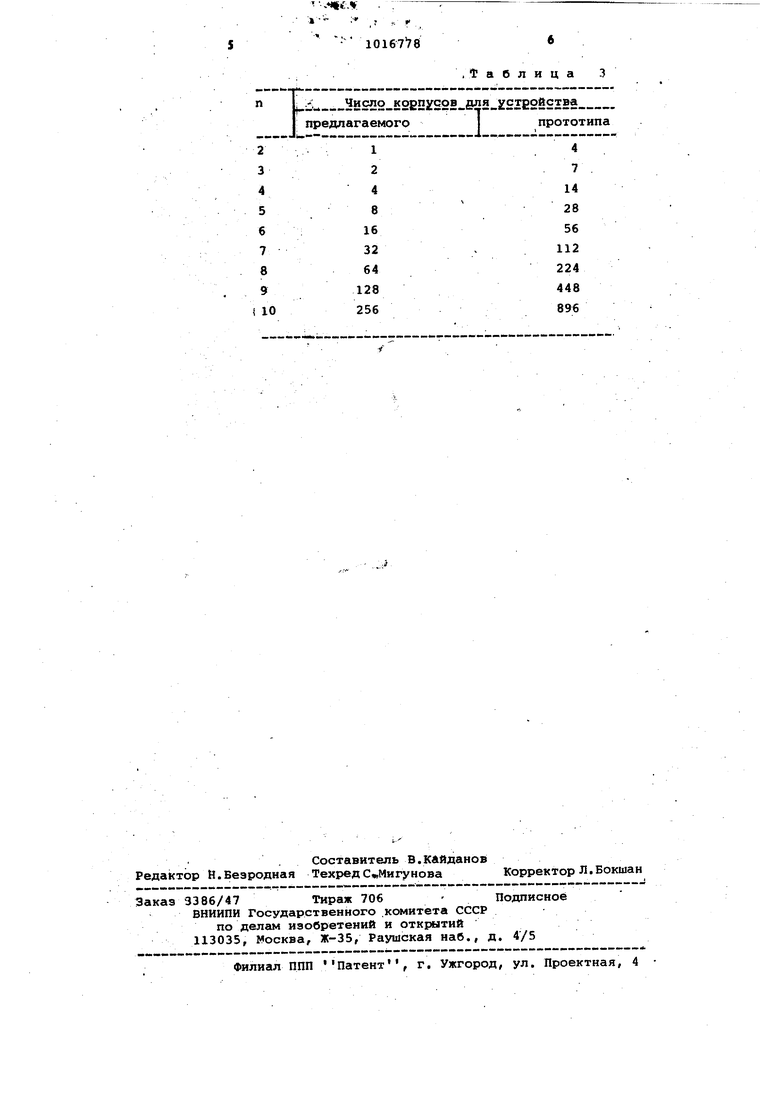

где А - сложность одной ячейки регистра; сложность всего регистра; 2- 2 - сложность группы элементов п п- 2 -1-п - сложность дааиф тора; п - число переменных, от ксхгорых зависит исходная функция; С - сложность остальной части схемы. Сложность предлагаемой схемы 82 оценивается формулой So D 2 С, сложность одной ячейки сдвиго вого регистра. Предлагаемая схема проще схеьы-про тотипа, кОЕда выполняется неравенствоЕсли для регистра в качестве ячейки памяти принять в схеме-прототипе простой RS-триггер, то в данной схеме D-триггер с внутренней задержкой информации, то , а , получим что неравенство +С 44-2 +2-2 -l-n-2ln+C справедливо при следовательно при построении устройства для вычкс- ления булевой разности логической функции, зависящей от шести и более переменных, предлагаемая схема является более простой, чем схема-про тотип., сравним сложность обоих устройств по числу корпусов серийно выпускаю шйхся интегральных схем, необходимых для их реализации. Для обеспечения равных условий при сравнении примем, что будут использоваться интегральные схемл. имеющие 14 или 16 выводов. Символом А С будем обозначать ближайшее число, не. мен1{Шее А. Число корпусо необходимых дли реализации предлагаемого устройства можно рассчитать по формуле Вычисление булевой разности I по X,,. (код 3 2 / 4 Г - чибл о корпу со в, необходимых для регшизации сдвигового регистра; С - число корпусов, необходимых для реализации остальной части схе№. исло корпусов, необходимых для троения схемы-прототипа, определяя формулой 2 /8t+ 22/403 , Щ - число корпусов, необходимых для реализации дешифv ратора; 2 /4L - число корпусов, необходи. мых для реализации группы элементов И; - число корпусов, необходимых для реализации регистр ра. В табл. 3 отражены затраты на реалиию обоих устройств,расчитанные по муле 4 и 5 .Коэффициент С в табе не учтен,поскольку он одинаков для их устройств. Кроме того,предлагаемая схема сравия кодов имеет значительно меньшее ло связей между корпусами, чем схе- прототип. Таблица Пример исходной функции при Т а б л и -ц а пер енной 0101

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Устройство для сравнения кодов | 1983 |

|

SU1103220A1 |

| Схема сравнения кодов | 1988 |

|

SU1522192A2 |

| Схема сравнения кодов | 1988 |

|

SU1599852A2 |

| Устройство для вычисления булевых производных | 1982 |

|

SU1128263A1 |

| Схема сравнения кодов | 1978 |

|

SU780003A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Устройство для счета изделий | 1985 |

|

SU1305737A1 |

| Устройство для вычисления булевых производных | 1986 |

|

SU1370651A1 |

| Устройство для вычисления булевых производных | 1988 |

|

SU1518825A2 |

СХЕМА CP VBHEHJffl КОДОВ, содержащая счетчик, .коммутатохмл, группу элементов НЕРАВНОЗНАЧНОСТЬ, элемент НЕРАВНОЗНАЧНОСТЬ, Причем входы первой группы схемы подключень соответственно к информационньм входам коммутаторов, управляющие входы первого коммутатора подключены соответственно к выходам счетчика, управляющие входы второго ксялмутатора подключены к выходам зл& JHTOB НЕРАВНОЗНАЧНОСТЬ группы, первые входы которых подключены соответственно к выходам счетчика, вторые входы элементов ,НЕРАВНОЗНАЧНОСТЬ подключены к входам второй группы схемы, выходы коммутаторов подключены соответственно к входам элемента НЕРАВНОЗНАЧНОСТЬ, отличающая с я тем. Что, с целью ее упрощения, схема:, содержит сдвиговый регистр, причем выход элемента НЕРАВ- , И НОЗНАЧНОСТЬ подключен к информационному входу сдвигового регистра, iyn4 равляющий вход которого подключен к ; входу счетных импульсов схемы и к счетному входу счетчика.

Авторы

Даты

1983-05-07—Публикация

1982-02-15—Подача