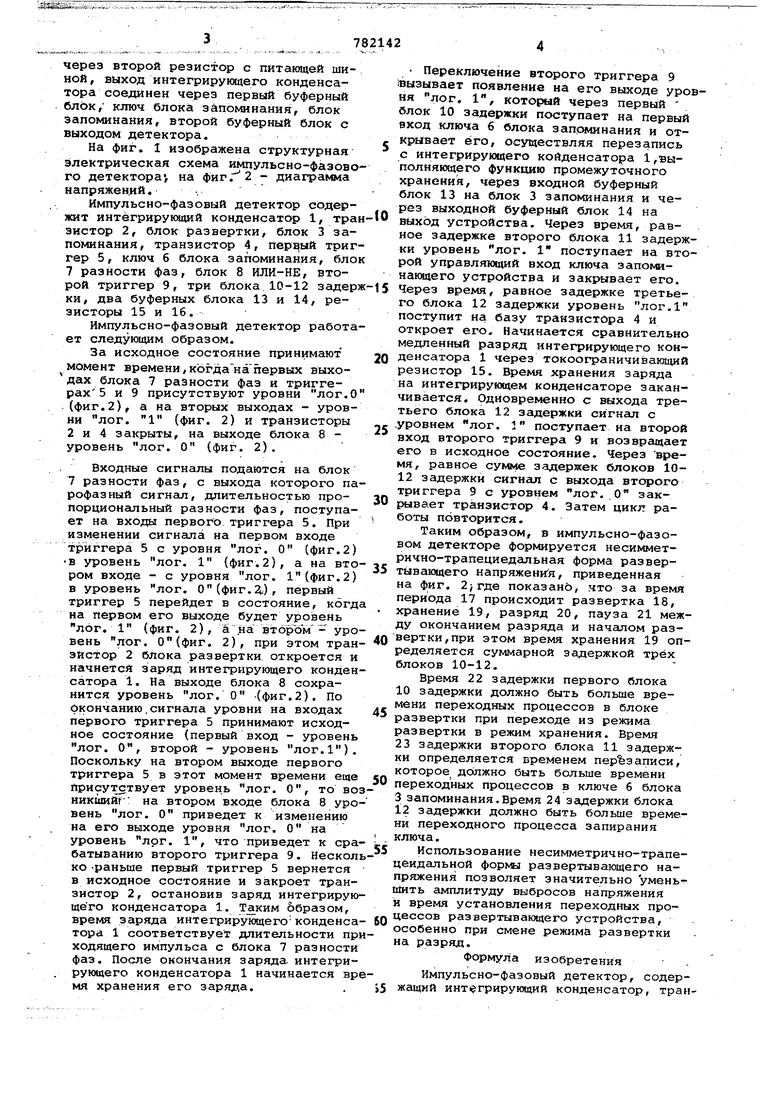

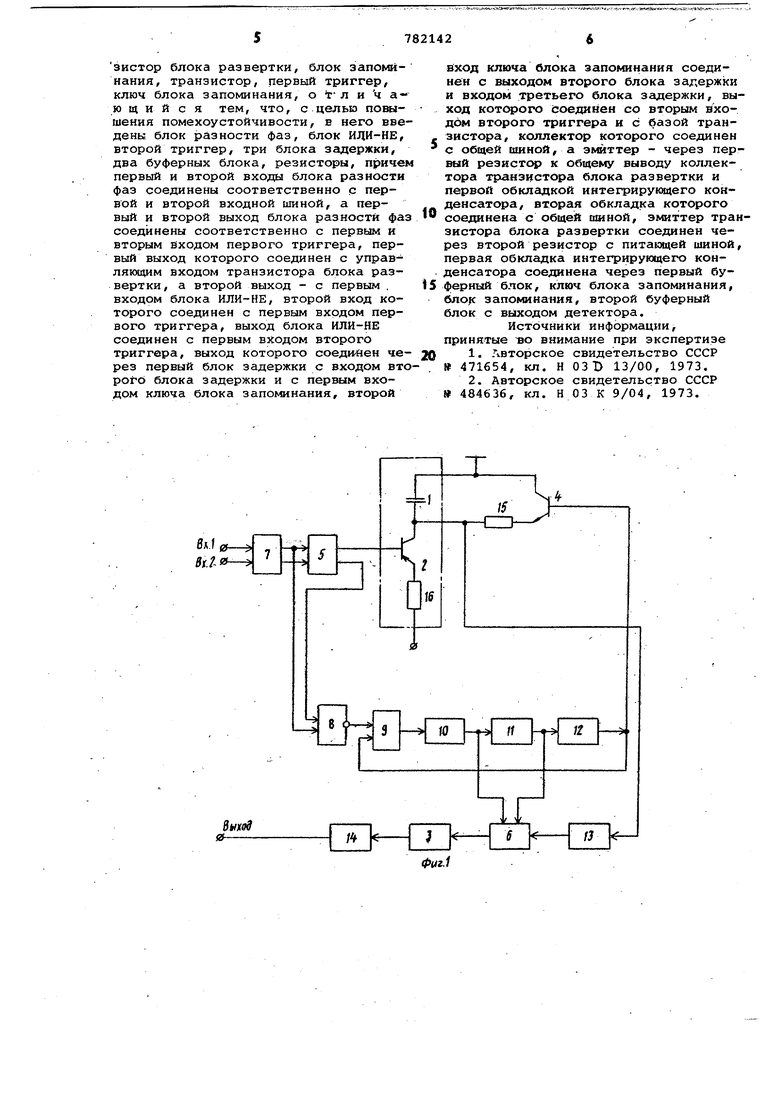

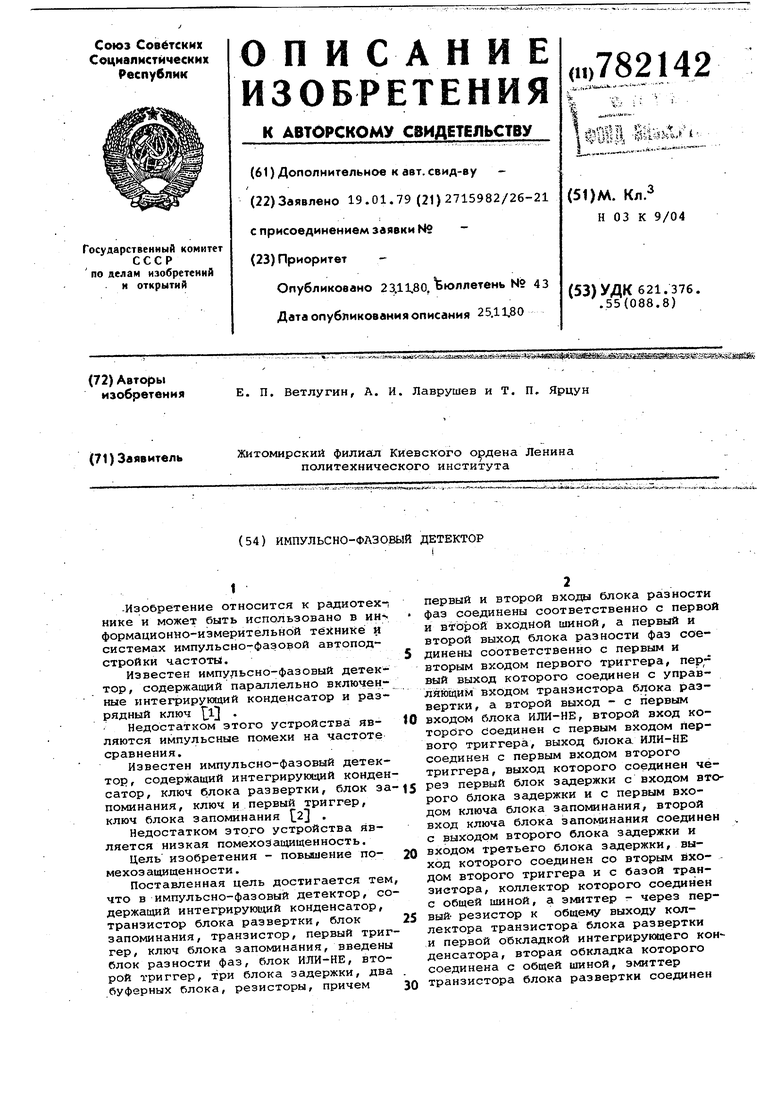

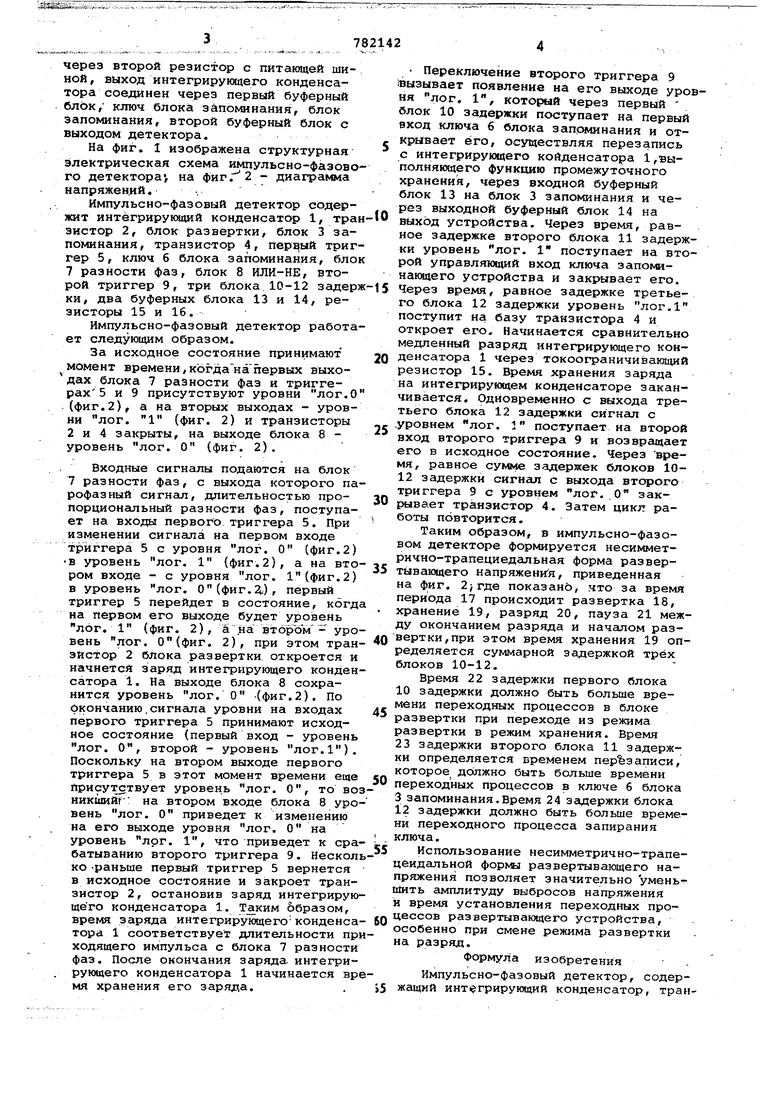

(54) ИМПУЛЬСНО-ФЛЗОВЫЙ ДЕТЕКТОР -Изобретение относится к радиотехнике и может быть использовано в ин формационно-иэмерительной технике и системах импульсно-фаэовой автоподстройки частоты. Известен импульсно-фазовый детектор, содержащий параллельно включенные интегрирукиций конденсатор и разрядный ключ 1 . Недостатком этого устройства являются импульсные помехи на частоте сравнения. Известен импульсно-фазовый детектор , содержащий интегрирующий конден сатор, ключ блока развертки, блок за поминания, ключ и первый триггер, ключ блока запоминания 2 . Недостатком этого устройства является низкая помехозащищенность. Цель изобретения - повышение помехозащищенности. Поставленная цель достигается тем что в импульсно-фазовый детектор, со держащий интегрирующий конденсатор, транзистор блока развертки, блок запоминания, транзистор, первый триг гер, ключ блока запоминания, введены блок разности фаз, блок ИЛИ-НЕ, второй триггер, три блока задержки, два буферных блока, резисторы, причем первый и второй входы блока разности фаз соединены соответственно с первой и второй входной шиной, а первый и второй выход блока разности фаз соединены соответственно с первым и вторым входом первого триггера, пер; вый выход которого соединен с управляющим входом транзистора блока развертки , а второй выход - с первым входом блока ИЛИ-НЕ, второй вход которого соединен с первым входом первого триггера, выход блока. ИЛИ-НЕ соединен с первым входом второго триггера, выход которого соединен через первый блок задержки с входом второго блока задержки и с первым входом ключа блока запоминания, второй вход ключа блока запоминания соединен с выходом второго блока згщержки и входом третьего блока задержки, выход которого соединен со вторым входом второго триггера и с базой транзистора, коллектор которого соединен с общей шиной, а эмиттер - через первый резистор к общему выходу коллектора транзистора блока развертки и первой обкладкой интегрирующего конденсатора, вторая обкладка которого соединена с общей шиной, эмиттер транзистора блока развертки соединен . 37821424 ерез второй резистор с питающей ши- Переключение второго триггера 9 ной, выход интегрирующего конденса-1вызывает появление на его выходе уровтора соединен через первый буферныйня лог. 1, который через первый блок/ ключ блока запоминания, блокблок 10 задержки поступает на первый запоминания, второй буферный блок свход ключа 6 блока запоминания и отвыходом детектора. крывает его, осуществляя перезапись На фиг. 1 изображена структурная с интегрирующего койденсатора 1,выэлектрическая схема импульсно-фазово-полняющего функцию промежуточного го детектора , на фиг. - диаграммахранения, через входной буферный напряжений. -,блок 13 на блок 3 запоминания и чеИмпульсно-фазовый детектор содер-рез выходной буферный блок 14 на жит интёгрирукяций конденсате 1, тран-О выход устройства. Через время, равзистор 2, блок азвертки, блок 3 за-ное згщержке второго блока 11 задержпоминания, транзистор 4, первый триг-ки уровень лог. 1 поступает на втогер 5, ключ 6 блока запоминания, блокрой управляющий вход ключа запоми7 разности фаз, блок 8 ИЛИ-НЕ, вто-нающего устройства и закрывает его. рой триггер 9, три блока 10-12 задерж-15 Через время, равное задержке третьеки, два буферных блока 13 и 14, ре-го блока 12 задержки уровень лог.1 зисторы 15 и 16.поступит на базу транзистора 4 и Импульсно-фазовый детектор работа-откроет его. Начинается сравнительно ет следующим образом.медленный разряд интегрирующего конЗа исходное состояние принимают20 денсатора 1 через токоограничивающий момент времени,когданапервых выхо-резистор 15. Время хранения заряда дах блока 7 разности фаз и тригге-на интегрирующем конденсаторе заканрах5 и 9 присутствуют уровни лог.О чивается. Одновременно с выхода тре(фиг.2), а на вторых выходах - уров-тьего блока 12 задержки сигнал с ни лог. 1 (фиг. 2) и транзисторы.уровнем лог. 1 поступает на второй 2 и 4 закрыты, на выходе блока 8 вход второго триггера 9 и возвращает уровень лог. О {фиг. 2).его в исходное состояние. Через вре. входные сигналы подаются на блок о задержек блоков 107 разности фаз, с выхода которого па-1 задержки сигнал с выхода второго рофазный сигнаА, длительностью про-ЗО п „ Уровнем лог. .0 зак . рывает транзистор 4. Затем цикл оапорциональный разности фаз, поступа- повтооитс я ет на входы первого триггера 5. При °™ повторится. изменении сигнала на первой входе„ «« образом, в импульсно-фазотриггера 5с уровня лог. О (фиг.2) детекторе формируется несимметi iii i:r.i,:.K:.i.;f.i ,™г..ла, -.-i-. вень лог. О (фиг. 2), при этом тран- 40 тся суммарной задержкой трёх зйстор 2 блока развертки откроется и блоков 10-12 « , начнется заряд интегрирующего конден- г, т. - --« .Г.°реS2 « pS-r/sSK./HS- « r,L-r sr;;eS;r- ; ное состояние (первый вход - уровень Развертки в режим хранения Время лог. О, второй - уровень лог.1). задержки второго блока 11 задержПоскольк на втором выходе первого « определяется временем перезаписи, триггера 5 в этот момент времени еще 50 ° ° времени присутствует уровень лог. О, то воз-° переходных процессов в ключе 6 блока никшийГ: на втором входе блока 8 уро J запоминания.Время 24 задержки блока ..гг , JSoJ-SouSa s«-L:rуровень лог. 1, что приведет к ера- г, , батыванию второго триггера 9. Несколь- Использование несимметрично-трапеТ - . r.no ieS--pr J « KSoSr - ,,Z,. ходящего импульса с блока 7 разности - фаз. после окончания заряда интегри-Формула изобретения рующего конденсатора 1 начинается вре- Импульсно-фазовый детектор, содермя хранения его заряда. . 5жащий инт15:грирующий конденсатор, транзистор блока развертки, блок запоминания, транзистор, первый триггер, ключ блока запоминания, о т л и ч аю щ и и с я тем, что, с целью повышения помехоустойчивости, в него введены блок разности фаз, блок ИДИ-НЕ, второй триггер, три блока задержки, два буферных блока, резисторы, причем первый и второй входы блока разности фаз соединены соответственно с первой и второй входной шиной, а первый и второй выход блока разности фаз соединены соответственно с первым и вторым йходом первого триггера, первый выход которого соединен с управляющим входом транзистора блока развертки, а второй выход - с первым , входом блока ИЛИ-НЕ, второй вход которого соединен с первым входом первого триггера, выход блока ИЛИ-НЕ соединен с первым входом второго триггера, выход которого соединен через первый блок задержки с входом второго блока задержки и с перклм входом ключа блока зaпo мнaния, второй

вход ключа блока запоминания соединен с выходом второго блока задержки и входом третьехчэ блока згшержки, выход которого соединен со вторым входом второго триггера и с базой транзистора, коллектор которого соединен с общей шиной, а эмиттер - через первый резистор к общему выводу коллектора транзистора блока развертки и первой обкладкой интегрирукицего конденсатора, вторая обкладка которого

0 соединена с общей шиной, эмиттер транзистора блока развертки соединен через второй резистор с питающей шиной, первая обкладка интегрирующего конденсатора соединена через первый буферный блок, ключ блока запоминания, 6nofc запоминания, второй буферный блок с выходом детектора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

0 471654, кл. Н ОЗЪ 13/00, 1973.

2.Авторское свидетельство СССР 484636, кл. Н 03 К 9/04, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-фазовый детектор | 1987 |

|

SU1492462A1 |

| Фазовый детектор | 1988 |

|

SU1688377A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1992 |

|

RU2106060C1 |

| Преобразователь угла поворота вала в напряжение | 1983 |

|

SU1124360A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

| Импульсно-фазовый детектор | 1986 |

|

SU1522395A1 |

| Устройство для измерения вихрево-гО КОМпОНЕНТА СКОРОСТи пОТОКА | 1979 |

|

SU822038A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Импульсно-фазовый детектор | 1989 |

|

SU1698973A1 |

Авторы

Даты

1980-11-23—Публикация

1979-01-19—Подача