со to

О5 N3

Изобретение относится к импульсной технике и может быть использовано в информаиионно-измерительных системах с фазовым представлением информации или D системах импульсно-фазовой автоиодстройки частоты.

Цель изобретения - повышение быстродействия устройства путем уменьшения времени разряда интегрирующего конденсатора.

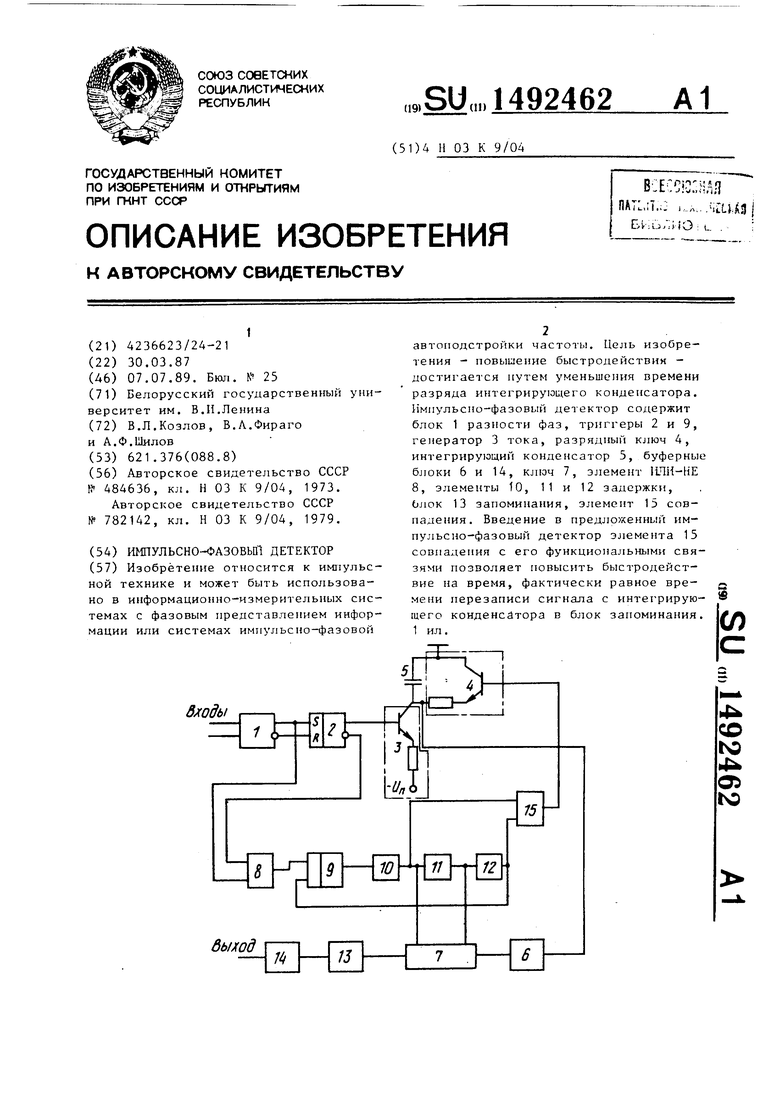

На чертеже приведена функциональная схема импульсно-фазового детектора.

Он содержит блок 1 разности фаз, триггер 2, генератор 3 тока, разрядный ключ 4, интегрирующий конденсатор 5, буферный блок 6, ключ 7, элемент ИЛН-НЕ 8, триггер 9, элементы

может быть .выполнен на транзисторе, Оаза которого соединена с управляющим входом, а в цепь эмиттера или коллектора включен резистор для ограничения разрядного тока и регулирования времени разряда интегрирующего конденса- тора 5. Ключ 7 может быть выполнен на интегральной схеме двухпозиционного ключа, в управляющую цепь которого включен RS-триггер с приоритетом одного из входов или дифференцирующими цепочками на входах.

Устройство работает следующим образом.

В отсутствие входных сигналов на прямых выходах блока 1 разности фаз и триггеров 2,9 присутствуют уровни Лог.О, а на инверсных Лог.1,

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-фазовый детектор | 1979 |

|

SU782142A1 |

| Устройство фазоимпульсной модуляции | 1985 |

|

SU1411958A1 |

| "Устройство для декодирования кода "Манчестер-2" | 1990 |

|

SU1809536A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197073A2 |

| Фазовый детектор | 1988 |

|

SU1688377A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Оптоэлектронный матричный индикатор напряжения | 1987 |

|

SU1594434A1 |

| Импульсно-фазовый детектор | 1989 |

|

SU1698973A1 |

| Устройство измерения временных интервалов | 1984 |

|

SU1144062A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

Изобретение относится к импульсной технике и может быть использовано в информационно-измерительных системах с фазовым представлением информации или системах импульсно-фазовой автоподстройки частоты. Цель изобретения - повышение быстродействия - достигается путем уменьшения времени разряда интегрирующего конденсатора. Импульсно-фазовый детектор содержит блок 1 разности фаз, триггеры 2 и 9, генератор 3 тока, разрядный ключ 4, интегрирующий конденсатор 5, буферные блоки 6 и 14, ключ 7, элемент ИЛИ-НЕ 8, элементы 10,11 и 12 задержки, блок 13 запоминания, элемент 15 совпадения. Введение в предложенный импульсно-фазовый детектор элемента 15 совпадения с его функциональными связями позволяет повысить быстродействие на время, фактически равное времени перезаписи сигнала с интегрирующего конденсатора в блок запоминания. 1 ил.

10 - 12 задержки, блок 13 запоминания,20 транзисторы генератора 3 и ключа 4 за

буферный блок 14, элемент 15 совпадений,при этом входы блока 1 разности фаз соединены с входными шинами устройства, а прямой и инверсный выходы блока 1 разности фаз соединены соответственно с S- и R-входами триггера 2, прямой выход которого соединен с управляющим входом генератора 3 тока, выход которого соединен через включенные параллельно разрядный ключ 4 и интегрирующий конденсатор 5 с общей шиной, а непосредственно - с входом бу4)ерного блока 6, выход которого соединен через включеннпые последовательно ключ 7, блок 13 запоминания и буферный блок 14 с выходной шиной устройства, причем входы элемента ИЛИ-НЕ 8 соединены с прямым выходом блока 1 разности фаз и инверсным выходом триггера 2, а выход эле- мента ИЛИ-НЕ 8 соединен с первым входом триггера 9, к выходу которого подключены соединенные последовательно элементы 10 - 12 задержки, выход элемента 10 задержки подключен к пер- вому управляющему входу ключа 7 и первому входу элемента 15 совпадений, выход которого соединен с управляющим входом разрядного ключа 4, а второй вход - с вторым входом триггера 9 и выходом элемента 12 задержки, вход которого соединен с вторым управляющим входом ключа 7. Генератор 3 тока в простейшем случае может быть выполнен на транзисторе, коллектор которого соединен с выходом генератора, база - с управляющим входом, а эмиттер через резистор с источником питания. Разрядный ключ 4 в простейшем случае

5

5

0 Q ,

0

5

крыты, на выходе элемента 8 - Лог.0.

Входные сигналы подаются на блок 1 разности фаз, на выходах которого появляется парафазный сигнал, длительность которого пропорциональна разности фаз. При появлении на S-входе триггера 2 уровня Лог. 1 на прямом выходе триггера появится Лог.1 (на инверсном - Лог. О), при этом транзистор генератора 3 откроется и начнется заряд интегрирующего конденсатора 5. По окончании импульса на выходе блока 1 триггер 2 перейдет в исходное состояние, нри этом транзистор генератора 3 закроется и заряд конденсатора 5 прекратится. Таким образом, время заряда интегрирующего конденсатора 5, а следовательно, и напряжение на нем, соответствуют длительности импульса, приходящего с блока 1 разности фаз. После окончания заряда начинается время хранения его заряда.

В момент окончания импульса с блока 1 на инверсном выходе триггера 2 на время, равное задержке сигнала в триггере 2, хранится уровень Лог.О. Поэтому па выходе элемента ПЛН-НЕ 8 возникает единичный импульс, длительность которого равна времени задержки в триггере 2. Этот импульс.переключает триггер 9 в состояние Лог. 1. С выхода триггера 9 Лог.1 через элемент 10 задержки поступает на вход ключа 7 и открывает его, осуществляя перезапись сигнала с конденсатора 5 через буферный блок 6 в блок 13 запоминания, с выхода которо

го сигнал через буферный блок 14 поступает на выход устройства. Через время, равное задержке элемента 11, уровень Лог,1 поступает на второй вход ключа 7 и закрывает его. Через время, рапное задержке элемента 12, уровень Лог.1 поступает на вход элемента 15 совпадений, на втором входе которого уже находится уровень Лог.1 с выхода элемента 10, и, значит, на его выходе появится уровень Лог. 1, открывающий транзистор ключа 4, через который начинаетс разряд конденсатора 5. Одновременно с выхода элемента 12 сигнал поступае на второй вход триггера 9 и возвращает его в состояние Лог. О. Через время, равное задержке элемента 10, уровень Лог. О поступит на вход элемента 15, на его выходе появится Лог.О, транзистор ключа 4 закроется и разряд конденсатора 5 прекратится. Время задержки элемента 10 должно быть больше времени пе- 1эеходных процессов при переходе из режима заряда в режим хранения и достаточным для обеспечения разряда конденсатора 5, и приблизительно равняться V - RC, где R - сопротивление резистора ключа 4, С - емкость конденсатора 5. Время задержки элемента 11 определяется временем, необходмым для перезаписи сигнала в блок 13 и затухания переходных процессов в

ключе 7. Задержка элемента 12 должна быть больше времени переходных процессов запирания ключа 7.

Время обработки принятой информации (хранение, перезапись и разряд интегрирующего конденсатора) в известном устройстве равняется удвоенной сумме задержек элементов 10 - 12. В данном устройстве, как следует из его принципа работы, это время составляет сумму задержек элементов 11 и 12 и удвоенной задержке элемента 10 что на время задержки элементов 11 и 12 меньше, чем в известном. Следо

10

0

с 25

0

5

0

5

пательно, минимально потможныи период следования импульсов на входе им- пульсно-фазового детектора уменьшается на время задержки элементов 11 и 12, что повышает быстродействие уст- poi tcTBa.

Таким образом, введение в известное устройство элемента совпадений с его связями позволяет повысить быстродействие на время, фактически равное времени перезаписи сигнала с интегрирующего конденсатора в блок запоминания .

Формула изобретения

Импульсно-фазовый детектор, содержащий блок разности фаз, входы которого соединены с входными шинами устройства, а инверсные выходы - с S- и R-входами первого триггера, прямой выход которого соединен с управляющим входом генератора тока, выход которого соединен через включенные параллельно интегрирующий конденсатор и разрядный ключ с общей шиной, а непосредственно - с входом первого буферного блока, выход которого через включенные последовательно ключ, блок запоминания и второй буферный блок соединен с выходной шиной, и элемент 11ЛИ-НЕ, входы которого соединены с прямым выходом блока разности фаз и инверсным выходом первого триггера, а выход - с первым входом второго триггера, к выходу которого подключены соединенные последовательно три элемента задержки, выходы первого и второго из которых соединены с первым и вторым управляющими входами ключа, а выход третьего - с вторым входом второго триггера, отличающий- с я тем, что, с целью повышения быстродействия, в него дополнительно введен элемент совпадений, входы которого соединены с выходами первого и третьего элементов задержки, а выход - с управлякхдим входом разрядного ключа.

| Импульсно-фазовый детектор | 1973 |

|

SU484636A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсно-фазовый детектор | 1979 |

|

SU782142A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-07—Публикация

1987-03-30—Подача