управляквдим входам дополнительных элементов Зсщержки, а выходы - к первым входам первого сумматора и к первым входам элементов поразрядного сравнения чисел, управляющий вход первого сумматора соединен с входной шиной, выходы каждого предьщущего сумматора через элементы задержки соединены с первыми входами последующих сумматоров и свторыми входами соответствующих элементов поразрядного сравнения чисел, выходы которых подключены к вторым управляющим входам всех элементов задержки, к управляющим входам остальных сумматоров и через расширители импульсов - к остальным входам порогового элемента, выходы элементов числовых констант соединены с вторыми входами сумматоров.

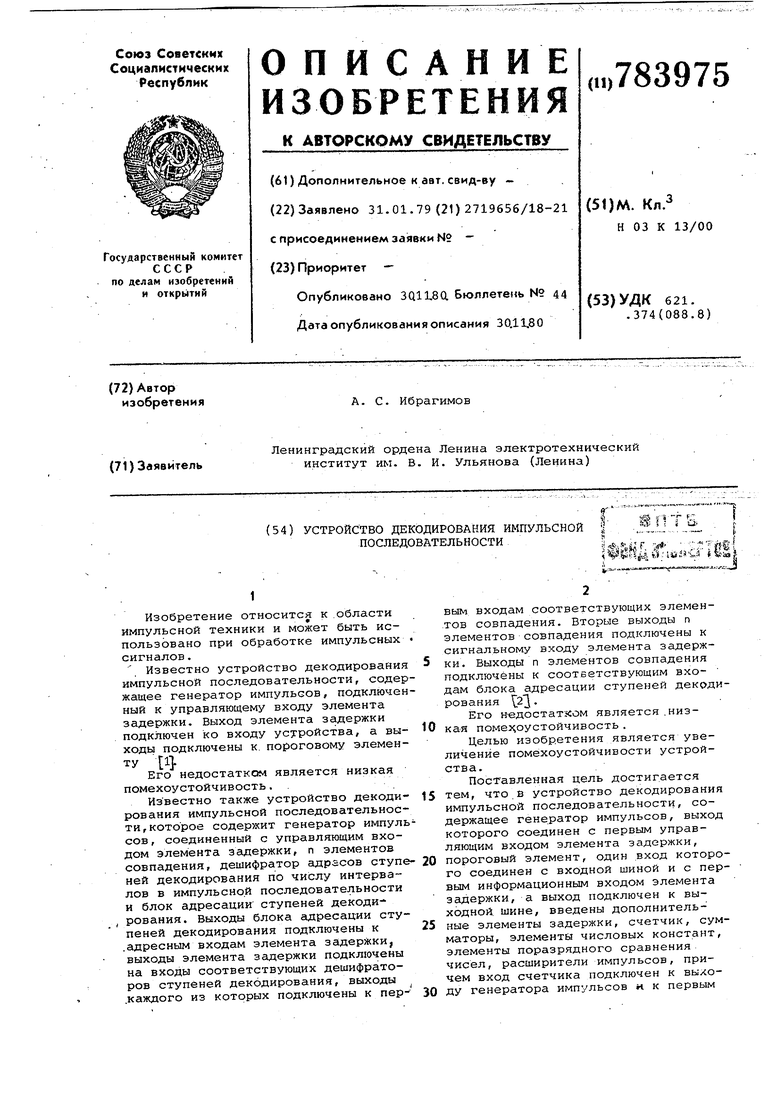

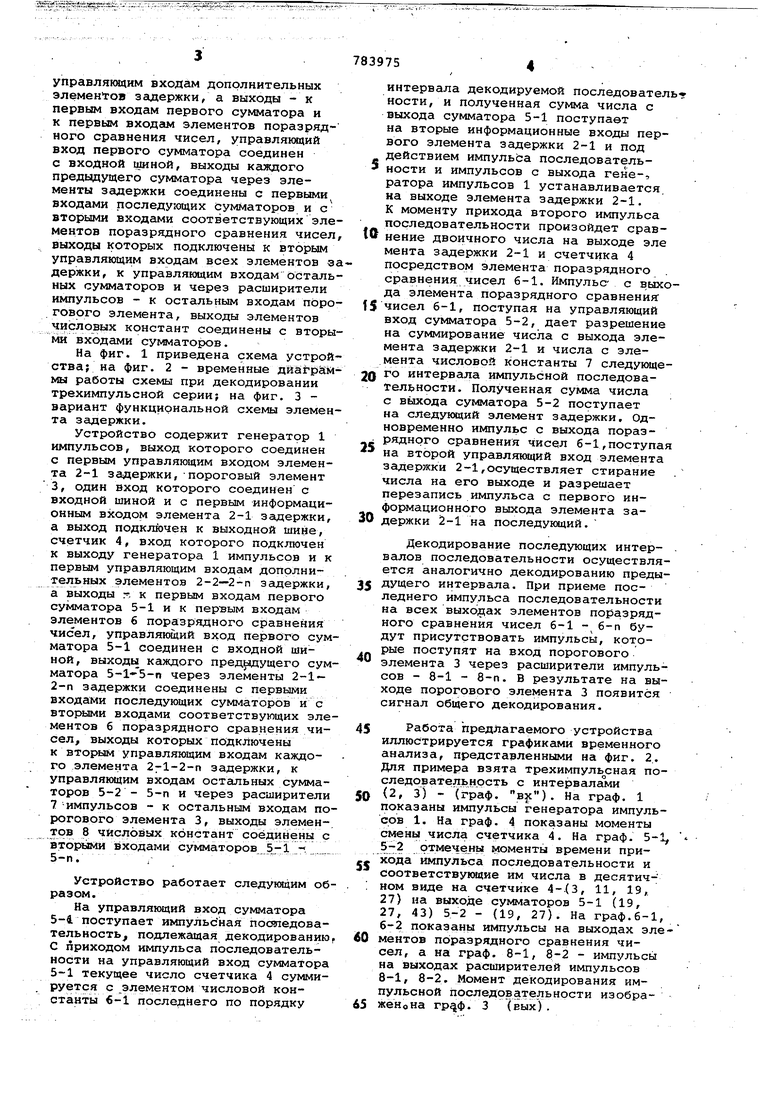

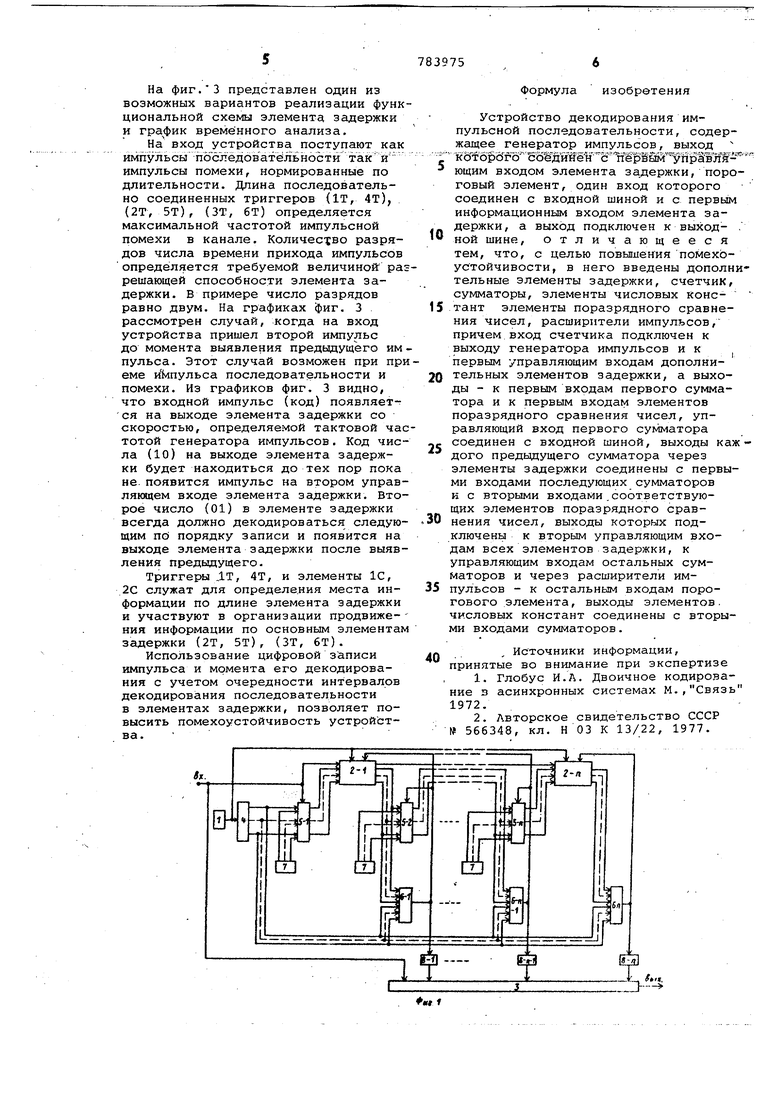

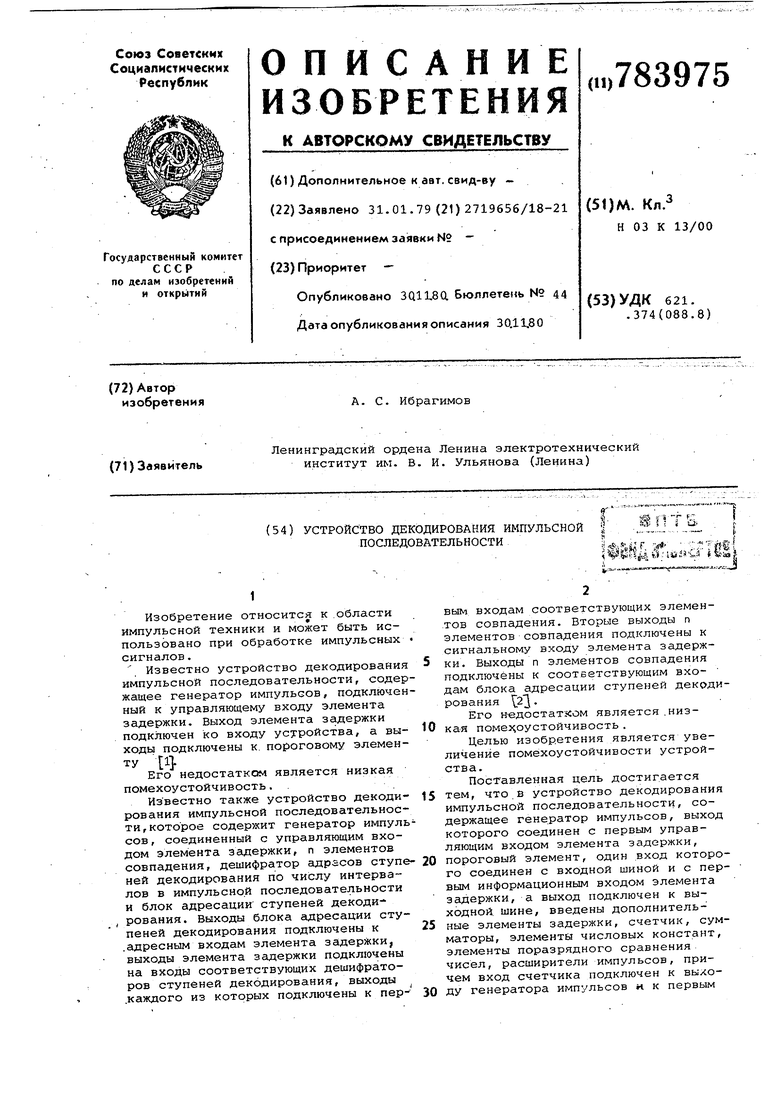

На фиг. 1 приведена схема устройства; на фиг. 2 - временные дйа ранмы работы схемы при декодировании трехимпульсной серии; на фиг. 3 вариант функциональной схемы элемента задержки.

Устройство содержит генератрр 1 импульсов, выход которого соединен с первым управляющим входом элемента 2-1 задержки, пороговый элемент 3, один вход которого соединен с входной шиной и с первым информационным входом элемента 2-1 задержки, а выход подключен к выходной шине, счетчик 4, вход которого подключен к выходу генератора 1 импульсов и к первым управляющим входам дополнительных элементов 2-2--2-п задержки, а выходы г. к первым входам первого сумматора 5-1 и к перэым входам элементов 6 поразрядного сравнения чисел, управлякаций вход первого сумматора 5-1 соединен с входной шиной, выходы каждого предьадущего сумматора 5-1-5-п через элементы 2-1 - 2-п задержки соединены с первыми входами последующих сумматоров и с вторыми входами соответствующих элементов б поразрядного сравнения чисел, выходы которых подключены к вторым управляющим входам каждого элемента 2 1-2-0 эадержки, к управляющим входам остальных сумматоров 5-2 - 5-п и через расширители 7 импульсов - к остальным входам порогового элемента 3, выходы элементов 8 числовых констант соединены с BTopbiottj входами сумматоров 5„-1 -. . „ 5-п. г ,

Устройство работает следующим образом.

На управляющий вход сумматора 5-4 поступает импульсная посяаедовательность, подлежащая декодированию С приходом импульса последовательности на управляющий вход сумматора 5-1 текущее число счетчика 4 суммируется с элементом числовой константы €-1 последнего по порядку

интервала декодируемой последовательности, и полученная сумма числа с выхода сумматора 5-1 поступает на вторые информационные входы первого элемента задержки 2-1 и под действием импульса последовательности и импульсов с выхода гене-, ратора импульсов 1 устанавливается, на выходе элемента задержки 2-1. К моменту прихода второго импульса последовательности произойдет сравw нение двоичного числа на выходе эле мента задержки 2-1 и счетчика 4 посредством элемента поразрядного сравнения чисел 6-1. Импульс- с выхода элемента поразрядного сравнения

5 чисел 6-1, поступая на управляющий вход сумматора 5-2, дает разрешение на суммирование числа с выхода элемента эадержки 2-1 и числа с элемента числовой константы 7 следующего интервала импульсной последовательности. Полученная сумма числа с выхода сумматора 5-2 поступает на следующий элемент задержки. Одновременно импульс с выхода поразрядного сравнения чисел 6-1,поступая на второй управляющий вход элемента задержки 2-1,осуществляет стирание числа на его выходе и разрешает перезапись импульса с первого информационного выхода элемента задержки 2-1 на последующий.

Декодирование последующих интер- . валов последовательности осуществляется аналогично декодированию предыJ дущего интервала. При приеме последнего последовательности на всех выходах элементов поразрядного сравнения чисел 6-1 - 6-п будут присутствовать импульсы, которые поступят на вход порогового

элемента 3 через расширители импульсов - 8-1 - 8-п. В результате на выходе порогового элемента 3 появится сигнал общего декодирования.

5 Работа предлагаемого устройства иллюстрируется графиками временного анализа, представленными на фиг. 2. Для примера взята трехимпуль сная последовательность с интервалами

0 (2, 3) - (граф. вх). На граф. 1 показаны импульсы генератора импульсов 1. На граф. 4 показаны моменты смены числа счетчика 4. На граф. 5-1 5-2 отмечены моменты времени прихода импульса последовательности и

соответствующие им числа в десятичном виде на счетчике 4-.(3, 11, 19,, 27) на выходе сумматоров 5-1 (19, 27, 43) 5-2 - (19, 27). На граф.6-1, 6-2 показаны импульсы на выходах элементов поразрядного сравнения чисел, а на граф. 8-1, 8-2 - импульсы на выходах расширителей импульсов 8-1, 8-2. Момент декодирования импульсной последовательности изображенона . 3 (вых).

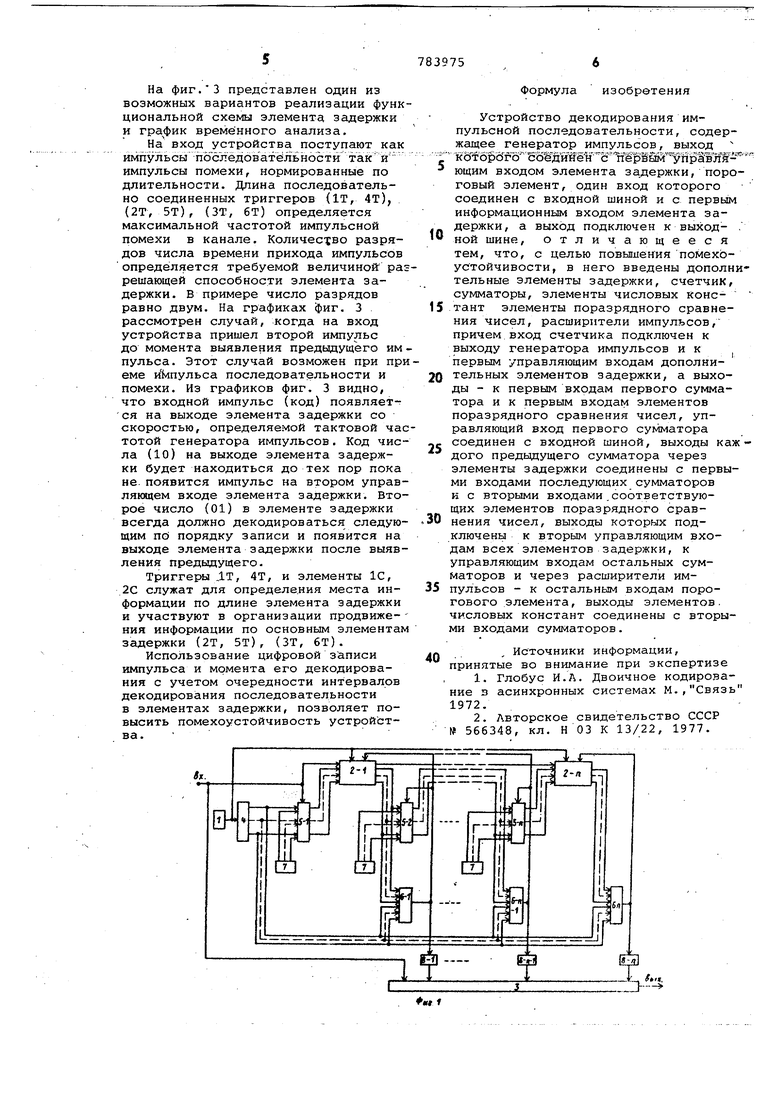

На фиг.З представлен один из возможных вариантов реализации функциональной схемы элемента задержки и временного анализа.

На вход устройства поступают как импульсы пбслёдоватёльностй так и импульсы помехи, нормированные по длительности. Длина последовательно соединенных триггеров (IT, 4Т), (2Т, 5Т), (ЗТ, 6Т) определяется максимальной частотой импульсной помехи в канале. Количество разрядов числа времени прихода импульсов определяется требуемой величиной разрешающей способности элемента задержки. В примере число разрядов равно двум. На графиках фиг. 3 рассмотрен случай, когда на вход устройства пришел второй импульс до момента выявления предыдущего им пульса. Этот случай возможен при приеме ийпульса последовательности и помехи. Из графиков фиг. 3 видно, что входной импульс (код) появляется на выходе элемента задержки со скоростью, определяемой тактовой частотой генератора импульсов. Код числа (10) на выходе элемента задержки будет находиться до тех пор пока не. появится импульс на втором управляющем входе элемента задержки. Второе число (01) в элементе задержки всегда должно декодироваться следующим но порядку записи и появится на выходе элемента задержки после выявления предыдущего.

Триггеры .IT, 4Т, и элементы 1C, 2С служат для определения места информации по длине элемента задержки и участвуют в организации продвижения информации по основным элементам задержки (2Т, 5Т), (ЗТ, 6Т).

Использование цифровой записи импульса и момента его декодирования с учетом очередности интервалов декодирования последовательности в элементах задержки, позволяет повысить помехоустойчивость устройства.

Формула изобретения

Устройство декодирования импульсной последовательности, содержащее генератор импульсов, выход кот6рбго еШШйё1 If Ifipi n ШЖ ющим входом элемента задержки, пороговый элемент, один вход которого соединен с входной шиной и с первым информационным входом элемента задержки, а выход подключен к выход- .

0 ной шине, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены дополнительные элементы задержки, счетчик, сумматоры, элементы числовых коне5тант элементы поразрядного сравнения чисел, расширители импульсов, причем вход счетчика подключен к выходу генератора импульсов и к первым управляющим входам дополнительных элементов задержки, а выхо0ды - к первым входам первого сумматора и к первым входам элементов поразрядного сравнения чисел, управляющий вход первого сумматора соединен с входной шиной, выходы каж5дого предыдущего сумматора через элементы задержки соединены с первыми входами последующих сумматоров и с вторыми входами.соответствующих элементов поразрядного сравDнения чисел, выходы которых подключены к вторым управляющим входам всех элементов задержки, к управляющим входам остальных сумматоров и через расширители им5пульсов - к остальным входам порогового элемента, выходы элементов. числовых констант соединены с вторыми входами сумматоров.

. Источники информации,

принятые во внимание при экспертизе

1.Глобус И.Л. Двоичное кодирование в асинхронных системах М.,Связь

1972.

2.Авторское свидетельство СССР № 566348, кл. Н 03 К 13/22, 1977.

(nepSbiif ijifp. Sxod)

; (Второй упр. бкод)

(пербыи инф. Ъьпод)

хоЗ

ует

ietiepai. I I I I I I I I I I М имп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования импульсной последовательности | 1978 |

|

SU729837A1 |

| Устройство для исследования путей в графе | 1982 |

|

SU1076909A1 |

| Устройство для исследования путей в графах | 1980 |

|

SU943738A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2039365C1 |

| Устройство для вычисления порядковых статистик последовательности двоичных чисел | 1988 |

|

SU1509936A1 |

| АКУСТООПТИЧЕСКИЙ АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2024026C1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Счетчик с предварительной уставкой | 1974 |

|

SU560341A1 |

к первым

У///////Л бхоаам

5Т

Т

///////Л

F сумматора

6Тf горой

Ш

т

управляющий

бход иг.З

Авторы

Даты

1980-11-30—Публикация

1979-01-31—Подача