(54) ДЕЛИТЕЛЬ ЧАСТОТг С УСТАНОВКОЙ НАЧАЛЬНОГО : ;

Изобретение относится к области вычислительной техники и может быть использовано в электронных вычислительных машинах, терьмналах, цифровых измерительных приборах в качестве де- 5 лителя частоты с установкой начального состояния.

Известен делитель частоты с установкой начального состояния, содержищий счетчик, первый и второй дешифра- w торы и триггер, входы,установки и сброса которого соединены с выходами дешифраторов, входы которых соединены с выходами счетчика 11.

Недостатком этого делителя частоты 15 с установкой начального состояния является относительно низкая достоверность функционирования, что связано с отсутствием контроля окончания установки счетчика в исходное 20 состояние.

Известен делитель частоты с установкой начального состояния, содержащий счетчик, выходы которого соедине-25 ны с входами дешифратора конечного состояния, выход которого соединен с входом установки вспомогательного триггера/ выход которого соединен с входом установки счетчика З. ЭО

СОСТОЯНИЯ

Недостатком этого делителя частоты является относительно низкое быстродействие.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в делитель частоты с установкой начального состояния, содержащий счетчик, выходы которого соединены с входами дешифратора конечного состо яния, выход KOTOjporo соединен с входом установки вспомогательного триггера, выход которого соединен с входом установки счетчика, введен дешифратор исходного состояния, входы которого соединены с выходами Счетчика, а выход дешифратора исходного состояния соединен с входом сброса .вспомогательного триггера.

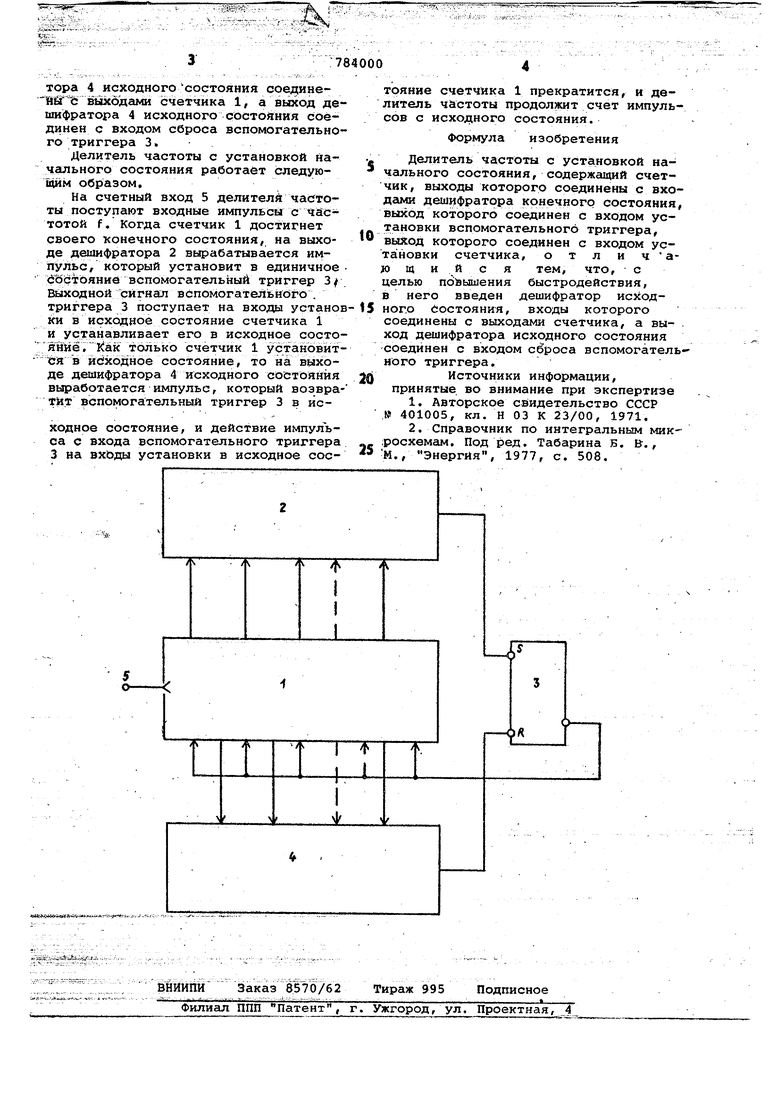

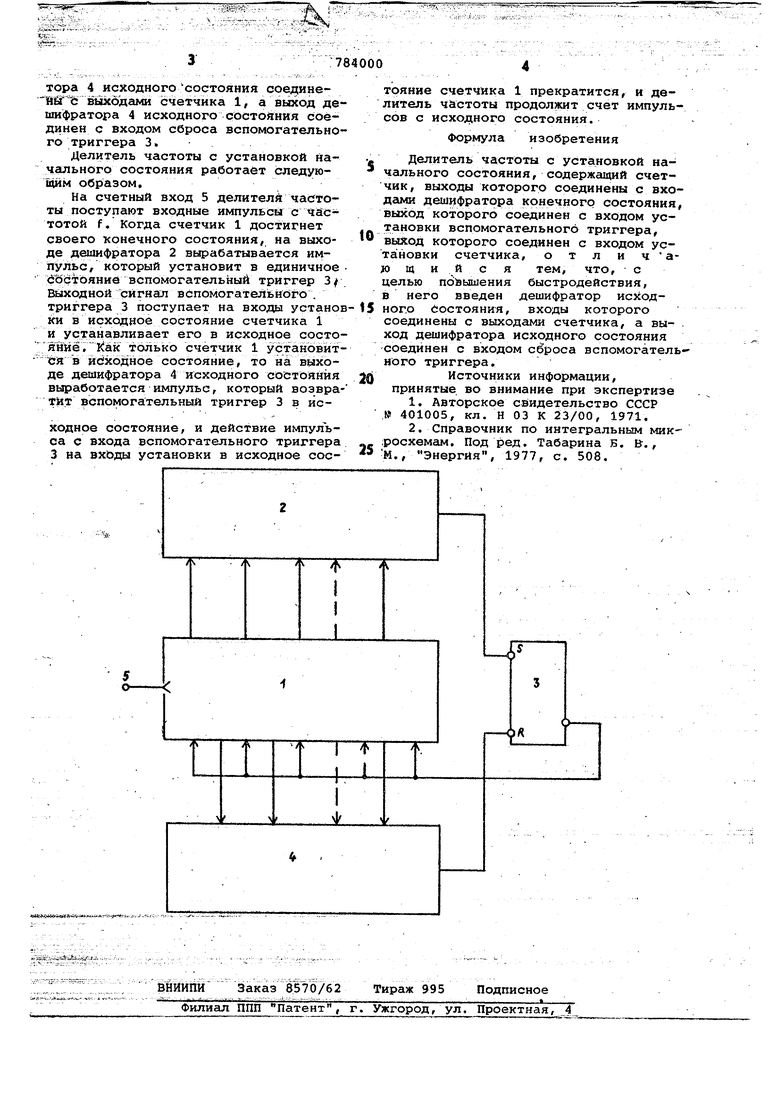

На чертеже пбказана структурная схема делителя частоты с установкой начального состояния.

Делитель частоты с установкой начального состояния содержит счетчик 1, выходы которого соединены с входами дешифратора 2 конечного состояния, выход которого соединен с входом установки вспомогательного триггера 3, выход которого соединен с входом установки счетчика 1, входы дешифратора 4 исходногосостояния соедине ЙЙ : выходами счетчика 1, а выход дешифратора 4 исходного состояния соединен с входом сброса вспомогательного триггера 3. Делитель частоты с установкой Начального состояния работает следую1цйм образом. На счетный вход 5 делители частоты поступают входные импульсы с частотой f. Когда счетчик 1 достигнет своего конечного состояния, на выходе дешифратора 2 вырабатывается импульс, который установит в единичное йостЪяние вспомогательный триггер 3f Выходной сигнал вспомогательного . триггера 3 поступает на входы установ ки в исходное состояние счетчика 1 и устанавливает его в исходное состояниё.ак только счётчик 1 установйттея в исходное состояние, то нё1 выходе дешифратора 4 исходного состояния выработается импульс, который воэвра ТИТ вспомогательный триггер 3 в исходное состояние, и действие импульса с входа вспомогательного триггера 3 на вхЬды установки в исходное состояние счетчика 1 прекратится, и делитель частоты продолжит счет импульсов с исходного состояния. Формула изобретения Делитель частоты с установкой начального состояния, содержащий счетчик, выходы которого соединены с входгши дешифратора конечного состояния, выход которого соединен с входом установки вспомогательного триггера, выход которого соединен с входом установки счетчика, о т л и ч аJO щ и и с я тем, что, с целью поЬышения быстродействия, в него введен дешифратор исХодног.о йостояния, входы которого соединены с выходами счетчика, а выход дешифратора исходного состояния соединен с входом сброса вспомогательного триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 401005, кл, Н 03 К 23/00, 1971. 2.Справочник по интегральным микросхемам. Под ред. Табарина Б. В,, М., Энергия, 1977, с. 508.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

| Фазометрическое устройство | 1982 |

|

SU1064225A1 |

| Фазосдвигающее устройство | 1980 |

|

SU938196A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1987 |

|

SU1480120A1 |

| Синхронное счетное устройство | 1985 |

|

SU1283962A1 |

| Устройство для моделирования подвижных объектов | 1987 |

|

SU1539791A1 |

| Делитель частоты | 1980 |

|

SU869055A1 |

| Преобразователь двоичного кода в числоимпульсный код | 1986 |

|

SU1383513A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

Ж

4-t

I JL

о

r

Авторы

Даты

1980-11-30—Публикация

1979-02-07—Подача