ЬА) ДЕЛИТЕЛЬ ЧАСТОТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1983 |

|

SU1162037A1 |

| Делитель частоты | 1983 |

|

SU1112571A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU949822A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1307587A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Электронные часы с коррекцией показаний по эталонным сигналам времени | 1986 |

|

SU1405020A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

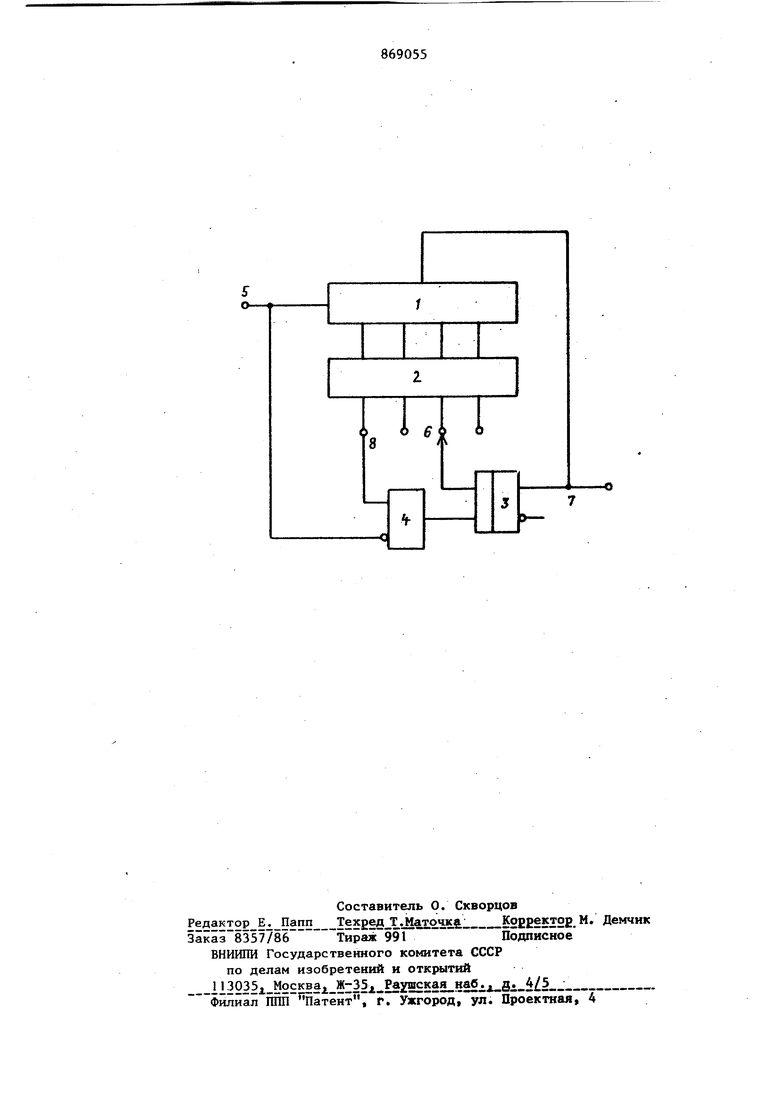

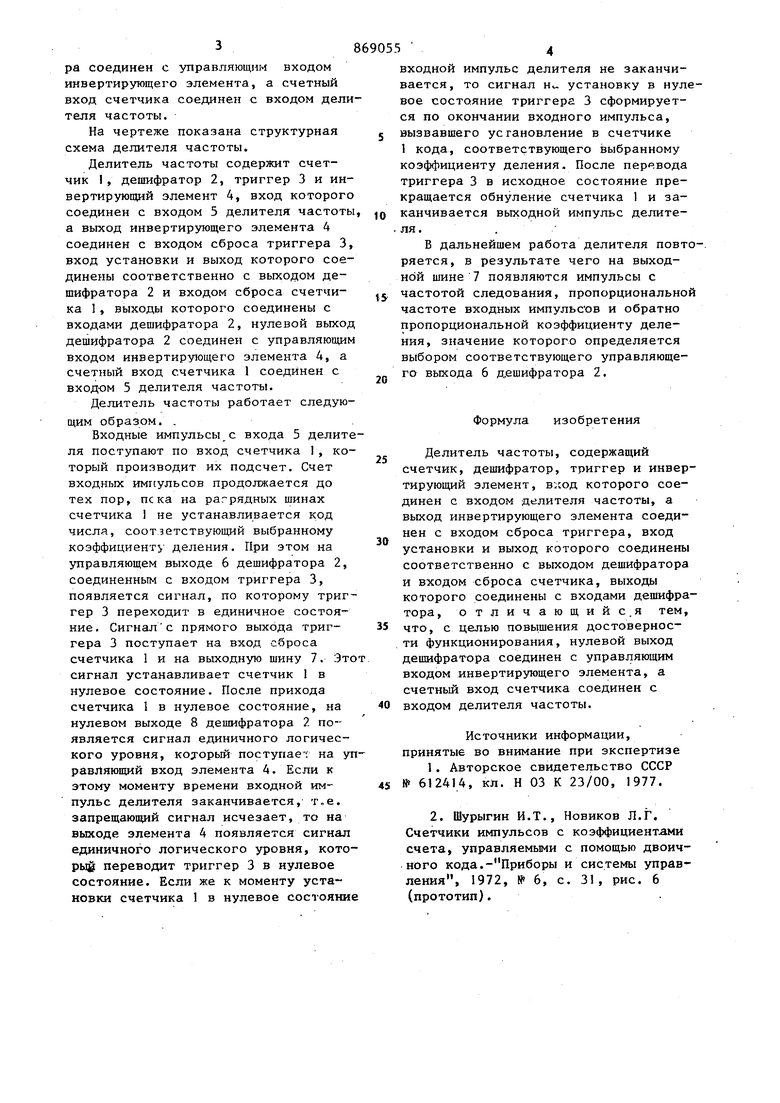

Изобретение относится к импульсной технике. Оно предназначено для использования в устройствах вычислительной техники, а также в устройствах автоматики и телемеханики. Известен делитель частоты, содержащий счетчик, выход которого соединен со входом дешифратора, инвертор, вход которого подключен к входной шине делителя, и триггер, счетный вход которого соединен с выходом дешифратора, установочный вход с выходом инвертора, а выход - с шиной сброса счетчика, счетный вход которого подключен к входной шине делителя | }. Недостатком этого делителя частоты является относительно низкая достовер ность функционирования. Наиболее близким техническим решением к предлагаемому является делитель частоты, содержащий счетчик, дешифратор, триггер и у.нвертирующий эл мент, вход которого соединен с входом Делителя частоты, а выход инвертирующего элемента соединен с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифратора t2. Недостатком этого делителя частоты является относительно низкая достоверность функционирования. Цель изобретения - повьшение достоверности функционирования. Поставленная цель достигается тем, что в делителе частоты, содержащем счетчик, дешифратор, триггер и инвертирующий элемент, вход которого соединен с входом делителя частоты, а выход инвертирующего элемента соединен- с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифратора, нулевой выход дешифратор;;pa соединен с управляющ 1м входом инвертирующего элемента, а счетный вход счетчика соединен с входом дел теля частоты. На чертеже показана структурная схема делителя частоты. Делитель частоты содержит счетчик 1, дешифратор 2, триггер 3 и ин вертирующий элемент 4, вход которог соединен с входом 5 делителя частот а выход инвертирующего элемента 4 соединен с входом сброса триггера 3 вход установки и выход которого сое динены соответственно с выходом дешифратора 2 и входом сброса счетчика 1, выходы которого соединены с входами дешифратора 2, нулевой выхо дешифратора 2 соединен с управляющи входом инвертирующего элемента 4, а счетный вход счетчика 1 соединен с входом 5 делителя частоты. Делитель частоты работает следую щим образом. . Входные импульсы с входа 5 делит ля поступают по вход счетчика 1, ко торый производит их подсчет. Счет входных имг ульсов продолжается до тех пор, пека на parрядных шинах счетчика 1 не устанавливается код числа, соотзетствующий выбранному коэффициенту деления. При этом на управляющем выходе 6 дешифратора 2, соединенным с входом триггера 3, появляется сигнал, по которому триг гер 3 переходит в единичное состояние. Сигналс прямого выхода триггера 3 поступает на вход, сброса счетчика 1 и на выходную шину 7. Эт сигнал устанавливает счетчик 1 в нулевое состояние. После прихода счетчика 1 в нулевое состояние, на нулевом выходе 8 дешифратора 2 появляется сигнал единичного логического уровня, Kojopbrti поступает на у равляющий вход элемента 4. Если к этому моменту времени входной импульс делителя заканчивается, т.е. запрещающий сигнал исчезает, то на выходе элемента 4 появляется сигнал единичного логического уровня, кото рый переводит триггер 3 в нулевое состояние. Если же к моменту установки счетчика 1 в нулевое состояни 4 входной импульс делителя не заканчивается, то сигнал установку в нулевое состояние триггера 3 сформируется по окончании входного импульса, вызвавшего установление в счетчике 1 кода, соответствующего выбранному коэффициенту деления. После перевода триггера 3 в исходное состояние прекращается обнуление счетчика 1 и заканчивается выходной импульс делителя. В дальнейшем работа делителя повто-. ряется, в результате чего на выходной шине 7 появляются импульсы с частотой следования, пропорциональной частоте входных импульсов и обратно пропорциональной коэффициенту деления, значение которого определяется выбором соответствующего управляющего выхода 6 дешифратора 2. Формула изобретения Делитель частоты, содержащий счетчик, дешифратор, триггер и инвертирующий элемент, вход которого соединен с входом делителя частоты, а выход инвертирующего элемента соединен с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифраотличающийс.я тем. что, с целью повышения достоверности функционирования, нулевой выход дешифратора соединен с управляющим входом инвертирующего элемента, а счетный вход счетчика соединен с входом делителя частоты. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 612414, кд. Н 03 К 23/00, 1977. 2.Шурыгин И.Т., Новиков Л.Г. Счетчики импульсов с коэффициентами счета, управляемыми с помощью двоичного кода.- Приборы и системы управ1972, № 6, с. 31, рис. 6 ления (прототип),

Т

64

i

Авторы

Даты

1981-09-30—Публикация

1980-01-14—Подача