f

Изобретение относится к области инетульсной техники и может быть использовано в устройствах обработки цифровой информации в измерительных приборах и вычислительных устройст- 5 вах.

Известен делитель частоты с коэффициент « пересчета 2N-1, содержащий Ы-разряднь й регистр сдвига, дополнительный триггер, элемент НЕ и два JO элемента и-НЕ.

Недостатком известного делителя является его относительная сложность-.

Известен делитель частоты с коэффициентом пересчета 2N-1, содержащий 15 Nr-pasрядный регистр сдвига, каждый разряд которого построен на D-тригге-ре f и входную шину, которая соединена с тактовыми входами разрядов регистра сдвига, инверсный выход послед-0 него разряда которого соединен с входами D и установки в О первого разряда регистра сдвига.

Недостатком известного делителя является несимметричность выходного 25 сигнала.

Целью изобретения является получение симметричного выходного сигнгша.

Для достижения поставленной цели в делитель частоты с коэффициен- Ю

том пересчета. 2N-1, содержащий N-разрядный регистр сдвига, каждый разряд которого построен на и-триггере, и вхойную шину. Которая соединена с тактовыми входами разрядов регистра сдвига, инверсный выход последнего разряда которого соединен с входами D и установки в О первого разряда регистра сдвига, введен-установоч О ный триггер, вход установки в

которого соединен с входной шиной, а.

1 - с инверсным

вход установки в

.вькоцом последнего разряда регистра сдвига.

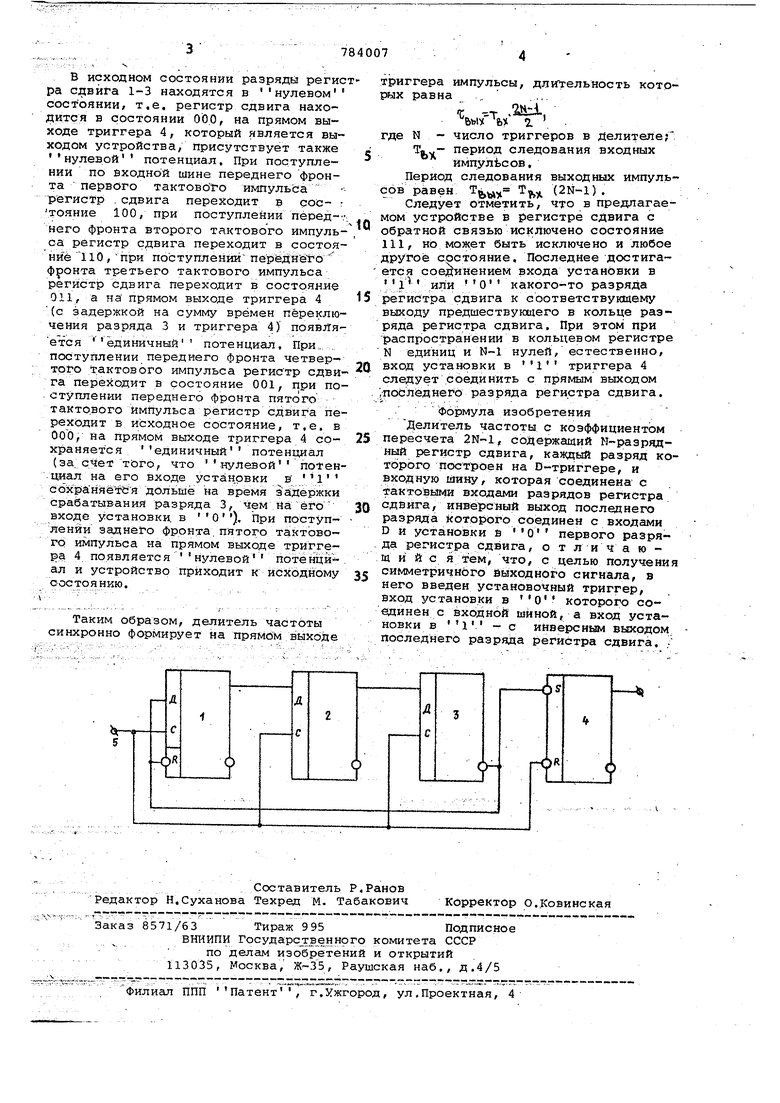

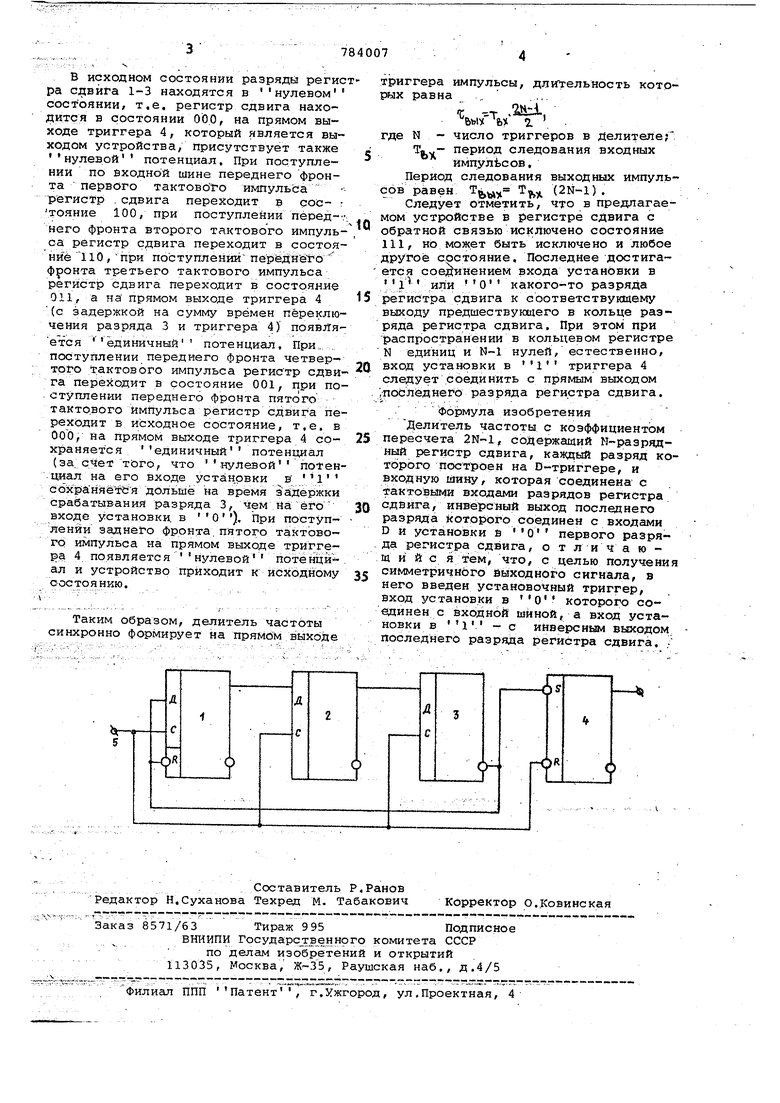

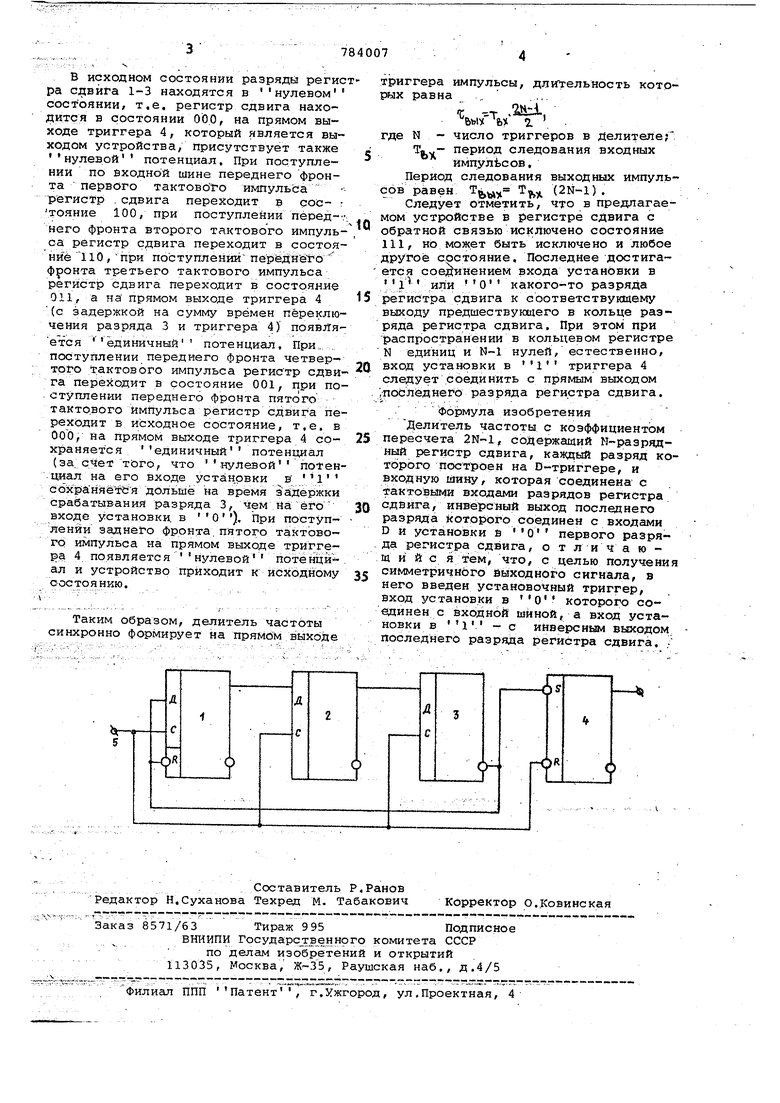

На чертеже приведена принципиальная схема делителя частоты с коэффициентом пересчета, равным пяти.

Делитель содержит разряды регистра сдвига 1-3 на D-триггерах, установочный триггер 4 и входную шину 5.

Входная шина 5 соединена с тактовыми входами разрядов регистра сдвига 1-3 и с входом установки в О установочного триггера 4, вход установки в которого соединен с инверсным выходом разряда регистра сдвига 3 и с входами D и установки в О разряда регистра сдвига 1.

Делитель работает следукхчим образом.

В исходном состоянии разряда регис ра С15вйга 1-3 находятся в нулевом состоянии, т.е. регистр сдвига находится в состоянии 00.0, На прямом выходе триггера 4, который является выходом устройства, присутствует также нулевой потенциал. При поступлении по входной шине переднего фронта первого тактового импульса регистр .сдвига переходит в сое- г тонкие 100, при поступлении перед--. него фронта второго тактового импульса регистр сдвига переходит в состояниё 110 , при поступлении перёдйётгб фронта третьего тактового импульса регистр сдвига переходит в состояние 011, а на прямом выходе триггера 4 (с задержкой на сумму времен переключения разряда 3 и триггера 4) появяяется единичный потенциал. При,., „ поступлении переднего фронта четвертого т.актового импульса регистр сдвига перегсодит в состояние 001, при по.отуплении переднего фронта пятого тактового импульса регистр сдвига переходит в исходное состояние, т.е. в 000, на прямом выходе триггера 4 сохраняется . единичный потенциал (за.. тйго, что .нулевой потен.циал на его входе установки в 1 сбхраняёФЬя дольше на время задержки срабатываний разряда 3, чем .на входе установки, в О ), При поступ ленйи заднего фронта.пятого тактового импульса на прямом выходе триггера 4 появляется нулевой потёнцй ал и устройство приходит к исходному состоянию.

Таким образом, делитель частоты синхронно формирует на прямб м выходе

триггера импульсы, длительность которых равна ., .... --Т .2iB..

ЬЫУ М 2. .

где N - число триггеров в Делителе;; период следования входных

m ,..

импульсов. Период следования выходных импульсов равен ,ч (2N-1). Следует отметить, что в предлагае- мом устройстве в регистре сдвига с обратной связью исключено состояние 111, но мож.ет быть исключено и любое другое состояние. Последнее достига- ется сое нением входа установки в

«I jl I

О какого-то разряда

или

регистра сдвига к соответствумдему выходу предшествующего в кольце разряда регистра сдвига. При этом при распространении в кольцевом регистре N единиц и нулей, естественно.

триггера 4

0 вход установки в

следует соединить с прямым выходом ;-послёднег Ь разряда регистра сдвига.

. Формула изобретения Делитель частоты с коэффициентом

5 пересчета 2N-1, содержащий М-разрядный регистр сдвига, каждый разряд которого построен на D-триггере, и входную шину, которая соединена с тактовьлми входами разрядов регистра

0 сдвига, инверсный выход последнего разряда которого соединен с входами Пи установки и о первого разряда регистра сдвига, о т л и i а ю щ и и с я ем, что, с целью получения

с симметричного Выходного сигнала, в него введен установочный триггер.

вход установ.ки в

которого соед инен с входной шиной, а вход установки в . - с инверсным выходом последнего разряда регистра сдвига. /

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для записи информации в регистр сдвига | 1976 |

|

SU617787A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Формирователь синхроимпульсов биимпульсного кода | 1983 |

|

SU1128373A1 |

| Синхронное счетное устройство с предварительной установкой | 1987 |

|

SU1448408A1 |

| Устройство для задержки импульсов | 1989 |

|

SU1626350A1 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Расширитель импульсов | 1981 |

|

SU1014133A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Функциональный счетчик | 1980 |

|

SU886247A1 |

Авторы

Даты

1980-11-30—Публикация

1979-02-15—Подача