О

VI

VI со

О

о

го

Изобретение относится к импульсной технике и может быть использовано при разработке БИС высокочастотных делителей для синтезаторов частот.

Цель изобретения - расширение функциональных возможностей путем обеспечения получения как дробных так и целых коэффициентов деления при сохранении высокого быстродействия.

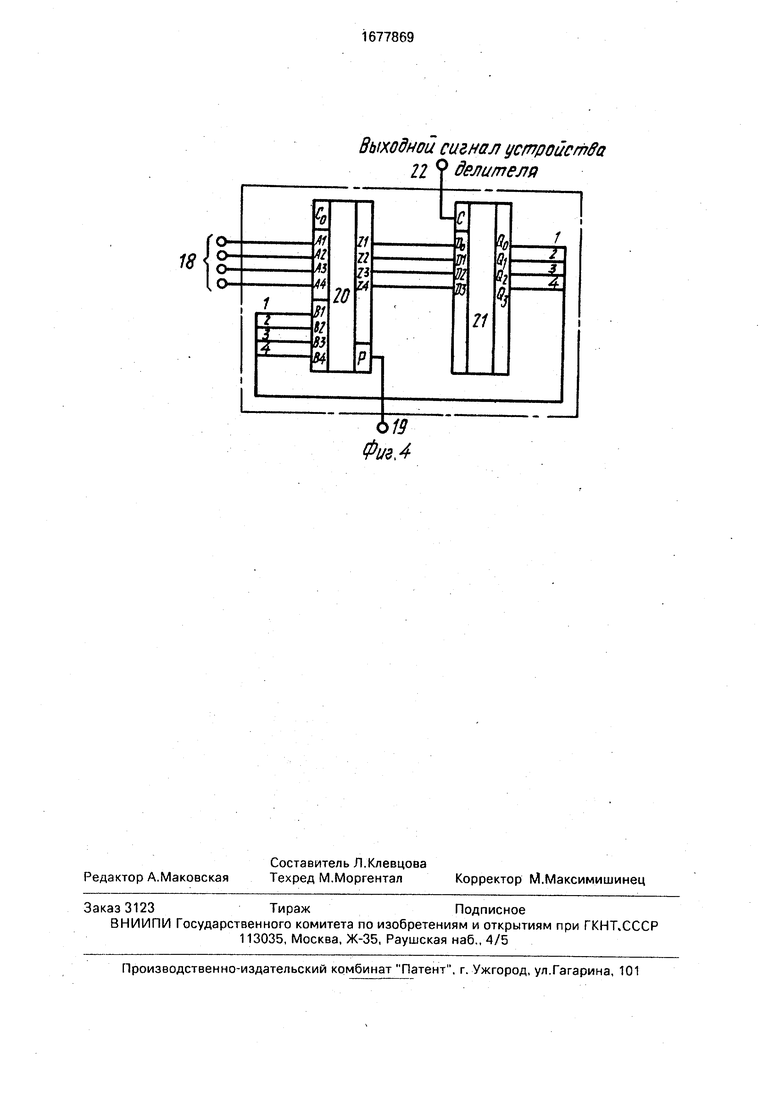

На фиг.1 приведена электрическая структурная схема делителя; на фиг.2 и 3 - временные диаграммы, поясняющие его работу; на -фиг.4 - структурная схема блока задания программы дробной части коэффициента деления.

Делитель содержит D-триггер 1 младшего разряда, D-триггер 2 управления младшим разрядом, первый D-триггер З, второй D-триггер 4, представляющие собой каскад 5 младшего разряда (младший каскад ) с коэффициентом деления 2/3, управляемый делитель 6 частоты старших разрядов (старший каскад, выполненный, например, на двоичном синхронном счетчике 6-1 импульсов типа К500ИЕ136 ЭСЛ серии К500. четыре выхода с четырех разрядов которого монтажно объединены для выполнения логической функции И для единичных сигналов и подключены к управляющему входу S, четыре информационных входа для параллельной установки разрядов в исходное состояние соединены с соответствующими шинами кода управления старших разрядов, а выход сигнала переноса подключен к шине сигнала записи каскада старших разрядов), шину 7 входного тактового сигнала, шины 8-1 ...8-N кода управления целой частью коэффициента деления, шины 9,10 сигналов подготовки записи младшего и записи старших разрядов, выходную шину 11 старшего каскада, выходную шину 12, а также третий D-триггер 13, элемент ИЛ И 14, элемент И 15, блок 16 задания программы дробной части коэффициента деления, вход которого подключен к выходной шине 12 устройства, информационные шины - к шинам 17-1...17-М кода управления дробной частью коэффициента деления, а выход - к первому входу элемента И 15, второй вход которого соединен с шиной 8-1 кода управления младшим разрядом устройства, причем элемент ИЛИ 14 включен между R-входом D-триггера 2 управления младшим разрядом и шиной 8-1 кода управления младшим разрядом устройства, а выход элемента И 15 соединен с R-входом третьего D-триггера 13, С- и D-входы которого соединены соответственно с С- и D-входами второго D-триггера 4, S-вход которого соединен с инверсным выходом третьего D- триггера 13.

Блок 16 задания программы дробной части коэффициента деления (фиг.4) содержит сумматор, первая группа информационных входов которого подключена к кодовой шине 18, а выход - к выходной шине 19 соответственно блока 16 задания программы дробной части коэффициента деления,

0 вторая группа информационных входов сумматора 20 подключена к информационным выходам регистра 21 сдвига, информационные входы которого подключены к информационным выходам сумматора 20, а тактовый

5 вход - к входной шине 22 блока 16 задания программы дробной части коэффициента деления.

Делитель работает следующим образом.

0 Введенный блок программы обеспечивает дробный коэффициент деления за счет увеличения на 1 коэффициента деления делителя в некоторых циклах счета. Например, длля обеспечения коэффициента

5 дробности 0,3 необходимо за 10 циклов деления устройства три раза делить на коэффициент К+1, где К - заданный коэффициент деления делителя, и 7 раз на К.

Блок программы дробности осуществ0 ляет манипуляции коэффициентами деления делителя К и К+1 в процессе работы делителя частоты с дробным коэффициентом деления. В качестве блока программы может быть использована схема стандарт5 ного накопительного сумматора, состоящего из регистров и сумматоров, как показано на фиг.4. Такая схема легко каскадируется при увеличении числа дробных разрядов. Блок программы фолрмирует для каж0 дого дробного коэффициента деления последовательность импульсов, определяющую количество циклов деления на К и на К+1. Последовательность импульсов с выхода блока программы управляет коэффициентом де5 ления младшего каскада. При единичном управляющем импульсе происходит увеличение коэффициента деления младшего каскада делителя на 1, нулевой управляющий импульс не влияет на коэффициент деления

0 младшего каскада. Если имеет место нулевой код дробной части коэффициента деления (шины 17-1...17-М в нуле), то работа делителя определяется кодом целой части коэффициента деления, поступающей на

5 его входы управления по шинам 8-1 ...8-N. Рассмотрим первый (а) режим работы устройства.

Режим а): при нулевом сигнале кода управления младшего каскада на шине 8-1 и нулевой дробности части коэффициента деления на выходе элементов ИЛИ 14 и 15 формируется уровень нуля, D-триггеры 2 и 13 постоянно находятся в нулевом состоянии независимо от сигналов на их информационных (D) входах. При этом D-триггер 13 не влияет на работу D-триггера 4, а D-триг- гер 2 не мешает D-триггеру 1, который работает в режиме автономного счета.

D-триггер З повторяет период выходного сигнала D-триггера 1 без снижения быстродействия последнего. С прямого выхода D-триггера З на тактовый вход старшего каскада подаётся сигнал, частота которого в два раза меньше частоты входного тактового сигнала устройства.

Старший разряд работает до заполнения своего счетчика 6-1 (состояние опознавания), при котором на выходах триггеров этого счетчика, монтажно объединенных для выполнения логической операции И, появляется единичный сигнал записи, поступающий на вход С управления режимом работы счетчика 6-1. В результате осуществляется параллельный ввод информации в счетчик 6-1 (процесс установки триггеров счетчика импульсов в состояния,определяемые заданным кодом управления на шинах 8-2...8-N, где N 5).

С некоторым запаздыванием относительно единичного сигнала записи на выходе Свых переноса этого счетчика импульсов формируется единичный сигнал.

Длительность указанных единичных сигналов равна периоду входного тактового сигнала старшего каскада, а период повторения определяется кодом управления на шинах 8-2...8-5.

Сигнал на выходе Свых. переноса счетчика 6-1 является выходным сигналом старшего каскада и используется в качестве сигнала записи старшего каскада, поступающего на информационные входы D-тригге- ров 4 и 13.

Независимо от коэффициента деления устройства сигнал, подаваемый на информационный вход D-триггера 4, должен формироваться в течение каждого цикла работы делителя, т.е. в течение каждого периода следования выходных импульсов устройства.

После прихода единичного сигнала записи старшего каскада с шины 10 по заднему фронту импульса с прямого выхода D-триггера З D-триггер 4 переходит в единичное состояние.

После окончания сигнала записи на шине 10 по заднему фронту очередного импульса с прямого выхода D-триггера З D-триггер 4 возвращается в нулевое состояние.

В результате на инверсном выходе этого триггера формируется нулевой сигнал, поступающий на выходную шину 12. Период этого сигнала определяется кодом управле5 ния на шинах 8-1...8-N. Поскольку прямые выходы D-триггеров 1 и 4 монтажно объединены для выполнения логической функцией И, то сигнал на прямом выходе D-триггера 4 (сигнал подготовки сигнала записи младше10 го каскада на шине 9) зависит от состояния этих триггеров. Шина 9 используется в том случае, если в качестве старшего каскада применить каскад, аналогичный младшему. Шина 9 такого каскада соединяется с ин15 формационным входом D-триггера 4 младшего каскада.

Режим б): при единичном сигнале кода управления младшего каскада на шине 8-1

0 и нулевой дробной части коэффициента деления работа устройства происходит согласно временным диаграммам (фиг.2).

В данном случае временные задержки триггеров не рассматриваются, так как воп5 рос быстродействия схемы подробно анали- зируется в описании к основному авторскому свидетельству.

Единичный сигнал, присутствующий на R-входе D-триггера 2, не оказывает влияния

0 на работу этого триггера.

Изменение состояний D-триггера 2 происходит в соответствии с сигналом на его информационном входе, а следовательно, зависит от состояний D-триггеров 1 и 4, так

5 как их прямые выходы монтажно объединены для выполнения логической функции И. При поступлении на шину 7 первых двух импульсов входного тактового сигнала устройства (фиг.2а) на прямом (фиг,2б) и инвер0 сном (фиг.2в) выходах D-триггера 1 формируются единичный и нулевой соответственно импульсы, длительность которых равна периоду входного тактового сигнала (фиг.2а). На прямом выходе D-триггера З в

5 соответствии с сигналом на информационном входе этого триггера также появляется единичный сигнал (фиг.2г), поступающий на вход синхронизации (тактовый вход) счетчика 6-1 и D-триггера 4. Последний до прихода

0 единичного сигнала записи старшего каскада (фиг.2д) находится в нулевом состоянии (фиг.2е) и, следовательно, на информационном входе D-триггера 2 (фиг.2ж) присутствует нулевой, а на инверсном выходе (фиг.2з)

5 этого триггера - единичный сигнал, не влияющий на работу D-триггера 1, D-триггер 1 продолжает работать в режиме автономного счета. Счетчик 6-1 старшего каскада работает до заполнения. Работа старшего аскада осуществляется так же, как и в случае нулевого сигнала кода управления младшего каскада.

После прихода единичного сигнала записи старшего каскада (фиг.2д) на информационный вход D-триггера 4 по заднему фронту второго импульса с прямого выход D-триггера З (фиг.2г) D-триггер 4 переходит в единичное состояние (фиг.2е).

Сигнал на информационном входе D- триггера 2 (фиг.2ж) начинает повторять сигнал на прямом выходе D-триггера 1 (фиг.2б). По заднему фронту n-го импульсов (п определяется кодом управления на шинах8-1...8-М) входной тактовой последовательности (фиг.2а) D-триггер 2 переходит в единичное состояние, а на его инверсном выходе (фиг.2з) появляется нулевой сигнал, блокирующий переход D-триггера 1 в единичное состояние по заднему фронту n+1-ro импульса входной тактовой последовательности (фиг.2а,б). В результате установка D-триггера 1 в нулевое состояние происходит без потери быстродействия всего устройства. При этом период выходного сигнала младшего каскада (фиг,2г) равен трем периодам входного тактового сигнала устройства (фиг.2а) и, следовательно, коэффициент деления младшего каскада равен 3.

После окончания единичного сигнала записи старшего каскада D-триггер 1 вновь начинает работать в режиме автономного счета, а коэффициент деления младшего каскада становится равным 2, С приходом каждого следующего сигнала записи старшего каскада процесс установки D-триггера 1 в нулевое состояние повторяется.

При наличии ненулевого кода дробной части коэффициента деления код дроби поступает по шинам 17-1...17-М на информационные входы блока 16 программы. На фиг,4 представлен один каскад накопительного сумматора, который предполагается использовать в качестве блока программы. На счетный вход блока программы поступает выходной сигнал устройства делителя, при этом на выходе блока программы - шине 23 (выходе переноса накопительного сумматора) - формируется импульсная последовательность, управляющая изменением коэффициента деления.

При единичном сигнале кода управления младшего каскада работа устройства происходит согласно временным диаграммам фиг.З.

Режим в): импульсы на выходе блока программы формируются по переднему фронту выходного сигнала устройства (фиг.Зж) и имеют длительность, кратную периоду работы делителя, поэтому когда на выходе блока программы имеет место нулевой сигнал, в дэнном периоде работа делителя совпадает с описанной выше (фиг.2).

Режим г): рассмотрим вариант, когда на выходе блока программы установлен единичный сигнал.

При единичном уровне сигнала на шине 8-1 элемент ИЛИ 14 разрешает по R-входу работу D-триггера 2, а при единичном сигнала с блока программы элемент И 15 раз0 решает по R-входу работу триггера 13. После прихода единичного сигнала записи старшего каскада (фиг.Зд) на информа- ционные входы D-триггеров 4 и 13 по заднему фронту второго импульса с прямого

5 выхода D-триггера 3 (фиг.Зг) D-триггеры 4 и 13 одновременно переходят в единичное состояние (фиг.Зе и Зз соответственно).

Сигнал на информационном входе D- триггера 2 (фиг.Зи) повторяет сигнал на пря0 мом выходе D-триггера 1 (фиг.36). По следующему входному тактовому (фиг.За) импульсу D-триггер 2 переходит в единичное состояние, а своим нулевым сигналом с инверсного выхода (фиг.Зк) блокирует пере5 ход D-триггера 1 в единичное состояние по заднему фронту следующего n+1-ro импульса входной тактовой последовательности (фиг.За.б), увеличивая при этом период работы D-триггера 1 и тем самым обеспечивая

0 коэффициент деления младшего каскада, равный 3.

После окончания единичного сигнала записи старшего каскада (фиг.Зз) по отрицательному фронту импульса с прямого выхо5 да D-триггера З D-триггер 13 устанавливается в исходное нулевое состояние (фиг.Зз), при этом D-триггер 4 остается в единичном состоянии до следующего импульса с прямого выхода D-триггера З

0 (фиг.Зе.г), так как D-триггер 13 блокирует D-триггер 4 по входу S.

За время, пока D-триггер 4 находится в единичном состоянии после возвращения D-триггера 13 в исходное нулевое состоя5 ние, на информационном входе D-триггера 2 повторно (фиг.Зи) возникает сигнал, повторяющий сигнал на прямом выходе D-триггера 1 (фиг.Зб).

По следующему n+З-му входному такто0 вому импульсу D-триггер 2 формирует на своем инверсном выходе (фиг.Зк) нулевой сигнал и повторно блокирует D-триггер 1.

При этом коэффициент деления младшего каскада становится разным 3.

5 Таким образом, за один период работы устройства младший каскад два раза работал с коэффициентом деления 3, 2 раза увеличив коэффициент деления устройства на 1.

Переключение сигнала с выхода блока 16 программы дробности (фиг.Зл) происходит по заднему фронту выходного сигнала устройства, то есть по окончанию сигнала с инверсного выхода D-триггера 4 (фиг.Зж), поэтому выходной сигнал блока 16 программы дробности может иметь задержку, равную почти периоду работы делителя, а точнее, на выходе элементов ИЛИ 14, И 15 должен быть сформирован единичный сигнал к окончанию сигнала импульса записи старшего каскада, то есть за три периода входной последовательности до окончания цикла счета.

При нулевом сигнале с блока программы работа делителя осущесвтляется с коэф- фициентом деления К и совпадает с описанным выше случаем по фиг.2.

Режим д): рассмотрим вариант, при котором на шине 8-1 управления младшим каскадом имеет место нулевой уровень, а с блока программы поступает сигнал единичного уровня напряжения. При этом на выходе элемента ИЛИ 14 будет сформирован единичный уровень напряжения, что разрешает работу D-триггера 2 по R-входу, а на выходе элемента И 15 будет иметь место уровень логического О, который по R-входу блокирует работу D-триггера 13.

Таким образом, работа делителя в этом режиме также сводится к описанному выше случают работы делителя по фиг.2.

Следовательно, данная схема обеспечивает увеличение коэффициента деления на 1 в тех периодах работы делителя, когда на выходе блока программы имеется сигнал уровня логической единицы, и тем самым формирует дробные коэффициенты деления делителя.

Общая формула коэффициента деления всего устройства имеет вид

м ( K+1) m +K(R -m) „ , m N0614p- - - К + -p- ,

где К - целая часть коэффициента деления, код которой установлен на шинах 8-1 ...8-N;

-н- - дробная часть коэффициента деления устройства;

R - емкость накопительного сумматора;

m - число разрядов дробности, код которых установлен на шинах 17-1.„17-М;

N - количество шин управления, определяющее емкость основного делителя 2 (а не код на шинах 8-1...8-N);

М - количество шин управления накопительным сумматором, определяющее емкость накопителя R 2м (не путать с кодом на шинах 17-1... 17-М).

На фиг.4 представлен двоичный накопитель, где М 4, a Ra 2м 16.

Исходя из выражения 105щ для получения дробного коэффициента деления необходимо за R циклов деления делителя m раз разделить на К+1 и (R-m) раз - на К. Таблица режимов работы устройства будет выглядеть следующим образом,

Обозначим через N1 код управления старшим каскадом делителя на шинах 8- 2...8-N. В режимах а) работы делителя код на шине 8-1 и шинах 17-1...17-М - нулевой, целочисленный режим работы делителя. Старший счетчик N раз делений младшего каскада на 2.

Мобщ-2М К, где К- четное.

В режиме б) код на шине 8-1 - единичный, а на шинах 17-1...17-М по-прежнему нулевой.

Для получения нечетного коэффициента деления младший каскад делит один раз на 3 и(м -1) раз на 2.

Мобщ-3 + 2(М|-1) 2М| + 1 U, где К - нечетное.

Старший счетчик считает работу млад- шего каскада с коэффициентом деления 2 и с коэффициентом деления 3. Общее количество делений младшего каскада равно N1.

В режимах в), г), д) осущесвтляется дробный режим работы делителя, Общий коэффициент деления делителя имеет вид

Мобщ К 4- к ,

m

где -g-дробная часть коэффициента деления.

Как было показано выше, дробный коэффициент деления образуется чередованием циклов работы делителя с целочисленными коэффициентами К и Ю 1,

Режим в) предусматривает случай деления на коэффициент К, и, таким образом, режим в) сводится к режиму б).

В режимах г) и д) рассматривается деление на коэффициент К+1.

В режиме г) код на шине 8-1 имеет единичный уровень, т.е. К - нечетное. При каждом нечетном К происходит увеличение коэффициента деления младшего разряда с 2 до 3 один раз за цикл деления делителя.

Следующее деление на 3 в младшем разряде увеличивает коэффициент деления делителя К на единицу. Как было показано в описании работы устройства, в этом случае младший каскад 2 раза делит на 3 из N раз,

Мобщ 3 + 3 + 2(М -2) 2N + 2 (2IM1 +

+ 1)+ 1 -К+1

В режиме д) К выбрано четным, код на шине 8-1 равен нулю. Чтобы увеличить К на единицу, достаточно одного деления на 3 в младшем разряде.

Младший каскад делит один раз на 3 и (N -1) раз на 2.

Мобщ 3 + 2(М -1) 2N1 + 1 К + 1

Устройство-прототип имеет коэффициент деления 2N1 +1, где N - код на шинах 8-2...8-N (справедливо только при условии, что на шине 8-1 имеет место уровень логической единицы). Аналогично устройство- прототип имеет коэффициент деления N , где N - код на шинах 8-1 ...8-N, т.е. К для рассматриваемого устройства.

Расширение функциональных возможностей предлагаемого делителя достигается путем получения любых дробных коэффициентов деления с максимальным коэффициентом

N&(2NLaKC+1) + -,

р Л

где -5- - максимально возможная дроб- к

ная часть коэффициента деления при данном R.

Устройство-прототип обеспечивает получение только целочисленных коэффициентов деления.

Предлагаемый делитель отличается простотой схемного построения. Введение дополнительных элементов расширяет его функциональные возможности и позволяет изменять коэффициент деления в сторону дробных разрядов без снижения быстродействия схемы, так как дополнительные элементы не нагружают высокочастотную входную шину 7 и не влияют на работу высокочастотных D-триггеров 1-3 младшего каскада. Это позволяет реализовать поданной схеме БИС высокочастотного делителя частоты с дробно-переменным коэффициентом деления для СВЧ синтезаторов по ЭСЛ технологии.

Формула изобретения 1. Делитель частоты с переменным коэффициентом деления по авт, св. № 1182669, о т л и ч а ю щ и и с я тем,

что, с целью расширения функциональных возможностей путем обеспечения возможности получения как дробных коэффициентов деления, так и целых при сохранении высокого быстродействия, в него-введены третий D-триггер, элемент ИЛИ, элемент И и блок задания программы дробной части коэффициента деления, вход которого подключен к выходной шине устройства,информационные шины - к шинам кода управления дробной частью коэффициента деления, а выход - к первому входу элемента И, причем элемент ИЛИ включен между R-входом D-триггера управления младшим разрядом и шиной кода управления младшим разрядом устройства, второй вход элемента ИЛИ подключен к первому входу элемента И, второй вход которого подключен к первому входу элемента ИЛИ, а выход элемента И соединен с

R-входом третьего D-триггера, С- и D-входы которого соединены соответственно с С- и D-входами второго D-триггера, S-вход которого соединен с инверсным выходом третьего D-триггера.

2. Делитель по п.1, о т л и ч а ю щ и и с я тем, что блок задания программы дробной части коэффициента деления содержит сумматор, первая группа информационных входов которого подключена к информационной

шине, а выход - к выходу блока задания программы дробной части коэффициента деления, вторая группа информационных входов сумматора подключена к информационным выходам регистра сдвига, информационные входы котсГрого подключены к информационным выходам сумматора, а тактовый вход- к входу блока задания программы дробной части коэффициента деления.

Выходной сигнал ycmpoucmffa 22 делителя

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Устройство для сопряжения с микроЭВМ | 1986 |

|

SU1709322A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

Изобретение относится к импульсной технике и может быть использовано при разработке БИС высокочастотных делителей для синтезаторов частот. Цель изобретения - расширение функциональных возможностей за счет обеспечения получения как дробных коэффициентов деления, так и целых при сохранении высокого быстродействия, -достигается путем введения в устройство D-триггера 13, элемента ИЛИ 14, элемента И 15, блока 16 задания программы дробной части коэффициента деления и образования новых функциональных связей. Кроме того, устройство содержит D-тригге- ры 1-4, управляемый делитель 6 частоты, шины 7, 8-1...8-N, 9-12, 17-1...17-М, входную, кода управления целой частью коэффи- циента деления, подготовки записи младшего разряда, подготовки записи старших разрядов, выходную старшего каскада, выходную устройства, кода управления дробной частью коэффициента деления. 1 з.п.ф-лы, 4 ил. Ё

Ы9

Фиг А

| Делитель частоты с переменным коэффициентом деления | 1987 |

|

SU1444939A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с переменным коэффициентом деления | 1984 |

|

SU1182669A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-15—Публикация

1988-12-12—Подача