t

Изобретение относится к области вычислительной техники и может быть использовано для преобразования параллельного двоичного кода в последовательный двоичный код.5

Известны устройства для параллельно-последовательного и последовательно-параллельного преобразования кодированного двоичным колом сигнала, у крторых сигналы на выходах импульс- 10 ного распределителя формируются при помощи двоичного счетчика и соединенной с выходами двоичного счетчика схемой совпадения. С j-ro выхода схемы совпадения сигнал снимается тогда и 15 только тогда, когда двоичный счетчик сосчитал в двоичной системе число J. Последовательный код снимается с выхода схемы ИЛИ, входы которой подключены к выходам схемы совпадения 1. 20

При увеличении разрядов преобразуемого кода в устройстве усложняются двоичный счетчик и схема совпадения и увеличивается необходимое количество входов схемы ИЛИ.25

Наиболее близким техническим решением к изобретению является устрой.ство для преобразования параллельното кода в последовательный 2, содержай1ее генератор импульсов, выход 30

которого соединен с информационным входом счетчика, выходы которого соединены с дешифратором. Выходы дешифратора соединены с первой группой входов блока элементов И, вторая группа входов которого соединена с выходами регистра. Информгщионные входы регистра подключены к входным шинам, а управляющий вход соединен с выходом блока управления. Выходы бло- ка элементов И соединены со входами элемента ИЛИ, выход которого подключен к выходной шине.

Преобразование параллельного(кода; в последовательный происходит путем поочередного подключения выходов регистра через элементы и на вход элемента ИЛИ, а затем к выходной шине. Выбор нужного элемента И осуществляется с помощью дешифратора и определяется состоянием счетчика.

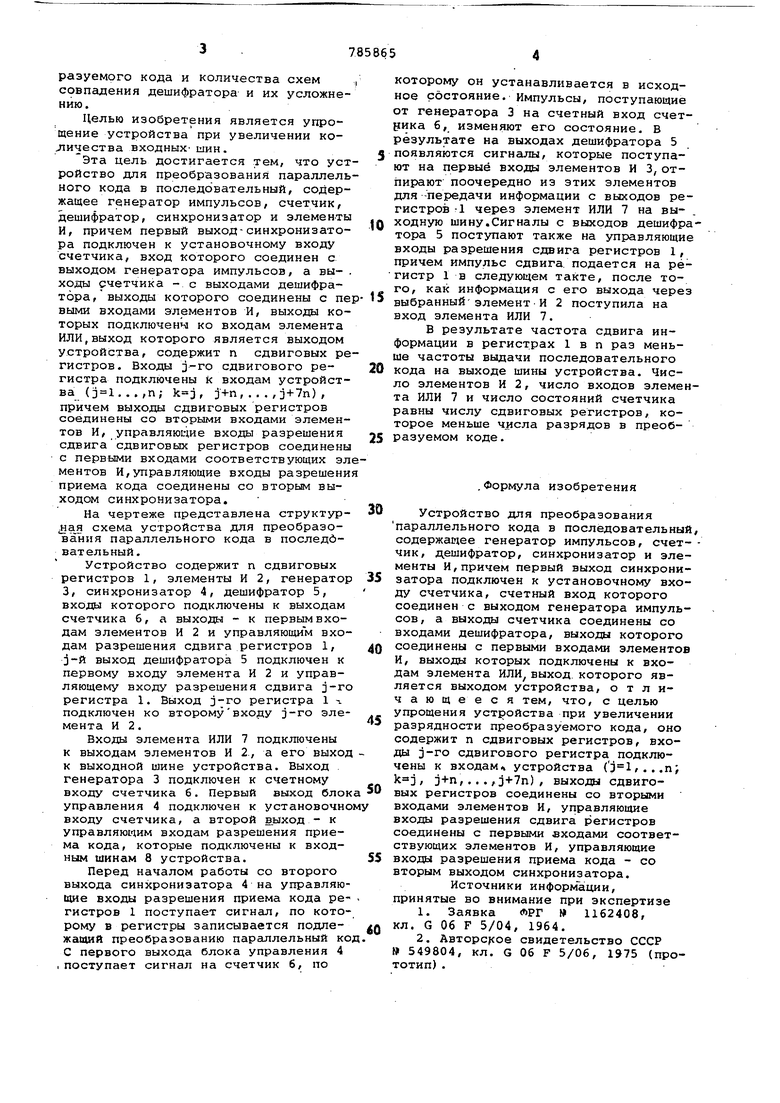

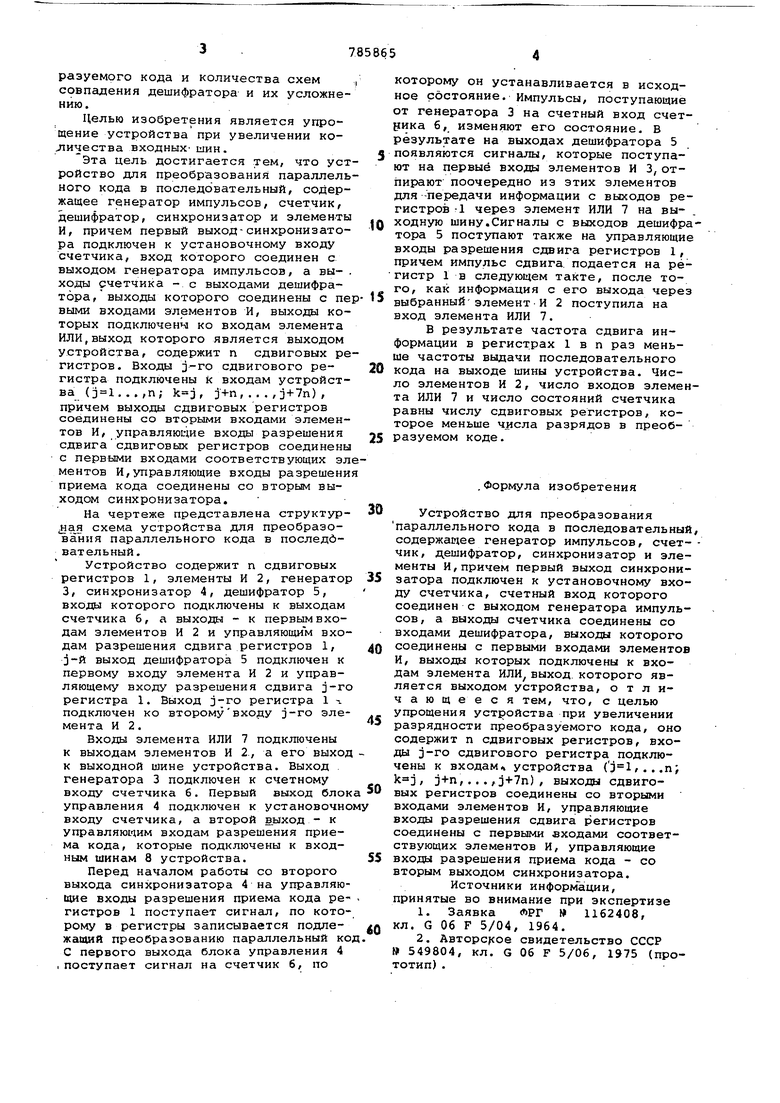

В этом устройстве увеличение разрядности преобразуемых кодов приводит к увеличению количества необходимых элементов блока элементов И и входов схемы ИЛИ, равное количеству разрядов в преобразуемом коде; разрядности счетчика, так как количех:тво состояний счетчика должно быть не меньше количества разрядов преобраэуемого кода и количества схем совпадения дешифратора и их усложнению. Целью изобретения является упрощение устройства при увеличении количества ВХОДНЫХ шин. Эта цель достигается тем, что уст ройство для преобразования параллель ного кода в последовательный, содержащее генератор импульсов, счетчик, дешифратор, синхронизатор и элементы И, причем первый выход-синхронизатора подключен к установочному входу счетчика, вход которого соединен с выходом генератора импульсов, а выходы счетчика - с выходами дешифратора, выходы которого соединены с пе выми входами элементов И, выходы которых подключены ко входам элемента ИЛИ,выход которого является выходом устройства, содержит п сдвиговых ре гистров. Входы j-ro сдвигового регистра подключены к входам устройства ( ... ,п ; , j+n,...,j+7n), причем выходы сдвиговых регистров соединены со вторыми входами элементов И, управляющие входы разрешения сдвига сдвиговых регистров соединены с первыми входами соответствующих эл ментов И,управляющие входы разрешени приема кода соединены со вторым выходом синхронизатора. На чертеже представлена структур(Ная схема устройства для преобразования параллельного кода в последбвательный. Устройство содержит п сдвиговых регистров 1, элементы И 2, генератор 3, синхронизатор 4, дешифратор 5, входы которого подключены к выходам счетчика б, а выходы - к первым входам элементов И 2 и управляющим входам разрешения сдвига регистров 1, j-й выход дешифратора 5 подключен к первому входу элемента И 2 и управляющему входу разрешения сдвига j-ro регистра 1. Выход j-ro регистра 1 т. подключен ко второмувходу j-ro элемента И 2. Входы элемента ИЛИ 7 подключены к выходам элементов И 2, а его выход к выходной шине устройства. Выход генератора 3 подключен к счетному входу счетчика б. Первый выход бло управления 4 подключен к установочно входу счетчика, а второй выход - к управляющим входам разрешения приема кода, которые подключены к входным шинам 8 устройства. Перед началом работы со второго выхода синхронизатора 4 на управляю щие входы разрешения приема кода ре гистров 1 поступает сигнал, по кото рому в регистры записывается подлежащий преобразованию параллельный ко С первого выхода блока управления 4 1 поступает сигнал на счетчик 6, по которому он устанавливается в исходное состояние. Импульсы, поступающие от генератора 3 на счетный вход счетрика б, изменяют его состояние. В результате на выходах дешифратора 5 появляются сигналы, которые поступают на первые входы элементов И 3, отпирают поочередно из этих элементов для -передачи информации с выходов регистров -1 через элемент ИЛИ 7 на выходную шину.Сигналы с выходов дешифратора 5 поступают также на управляющие входы разрешения сдвига регистров 1, причем импульс сдвига, подается на рёгистр 1 в следующем такте, после того, как информация с его выхода через выбранныйэлементИ 2 поступила на вход элемента ИЛИ 7. В результате частота сдвига информации в регистрах 1 в п раз меньше частоты выдачи последовательного кода на выходе шины устройства. Число элементов И 2, число входов элемента ИЛИ 7 и число состояний счетчика равны числу сдвиговых регистров, которое меньше числа разрядов в преобразуемом коде. .«Формула изобретения Устройство для преобразования параллельного кода в последовательный, содержащее генератор импульсов, счет-чик, дешифратор, синхронизатор и элементы И, причем первый выход синхронизатора подключен к установочному входу счетчика, счетный вход которого соединен с выходом генератора импульсов, а выходы счетчика соединены со входами дешифратора, выходы которого соединены с первыми входами элементов И, выходы которых подключены к входам элемента ИЛИ выход, которого является выходом устройства, отличающееся тем, что, с целью упрощения устройства при увеличении разрядности преобразуемого кода, оно содержит п сдвиговых регистров, входы j-ro сдвигового регистра подключены к входам устройства ...n; , j+n,...,j+7n), выходы сдвиговых регистров соединены со вторыми входами элементов И, управляющие входы разрешения сдвига регистров соединены с первыми входами соответствующих элементов И, управляющие входы разрешения приема кода - со вторым выходом синхронизатора. Источники информЪ ции, принятые во внимание при экспертизе 1.Заявка ЛРГ 1162408, кл. G 06 F 5/04, 1964. 2.Авторс ое свидетельство СССР 549804, кл. G 06 F 5/06, 1975 (прототип) .

BI

8,8.

BsSntS

SnSzn

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления процессом смешения жидких продуктов | 1985 |

|

SU1272314A1 |

| Устройство преобразования двоичного кода в двухполярное напряжение | 1986 |

|

SU1837398A1 |

| Устройство для измерения частоты | 1982 |

|

SU1247773A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1973 |

|

SU521564A1 |

| Цифровой стробоскопический преобразователь электрических сигналов | 1979 |

|

SU864136A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Вероятностный аналого-цифровой преобразователь | 1987 |

|

SU1531216A1 |

| Способ озвучивания кинофильмов и устройство для его осуществления | 1989 |

|

SU1705793A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

- /

.,

- /

On

Di

s

Авторы

Даты

1980-12-07—Публикация

1979-01-08—Подача