вход устройства соединен с входом установки числа регистра основания, разрядные выходы которого соединены с первыми разрядными входами блока возведения десятичной цифры в квадрат и двухразрядного умножителя, выход которого соединен с входом преобразователя десятичного числа в двоичньй код, выход которого соединен с счетным входом десятичного счетчика, разрядные входы которого соединены с выходом блока возведения десятичной цифры в квадрат, разрядные выходы регистра основания соединены соответственно с первой группой управляющих входов первой и второй схем сравнения, вторые группы управлякицих входов которых соединены соответственно с выходом десятичного счетчика, информационньй вход первой схемы сравнения соединен с вторым выходом третьего дешифратора, информационный вход второй схемы сравнения соединен с седьмым выходом второго дешифратора, вькод первой схемы сравнения соединен с первым входом первого элемента И, второй вход которого соединен с шестым выходом второго дешифратора, третий вход первого элемента И соединен с выходом генератора импульсов и тактовым входом преобразователя десятичного числа в дво- ичньй код, третий, четвертый, пятьй, шестой и седьмой выходы третьего дешифратора соединены соответственно с вторыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, двухразрядного умножителя, преобразователя десятичного числа в двоичный код и десятичного счетчика, отличающееся тем, что, с целью повышения быстродействия, в него введены вычитающий счетчик, сдвиговый регистр, элемент задержки, одновибратор, второй, третий и четвертьй элементы ИЛИ и третий триггер, выход которого соединен с четвертым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом сдвига регистра сдвига, разрядные выходы которого соединены соответственно с разрядными входами вычитающего счетчика, разрядные выходы которого соединены соответственно с вторыми разрядными входами блока возведения десятичной цифры в квадрат и двухразрядного умножителя, счетньй вход вычитакнцего счетчика соединен с выходом триггера реверса, первьй вход которого соединен с выходом третьего элемента РШИ, первьй вход которого соедине с выходом первой схемы сравнения и первым входом четвертого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, второй вход которого соединен с вторым входом триггера реверса, входом запуска одновибратора и выходом второй схемы сравнения, выход одновибратора соединен с вторым входом второго элемента ИЛИ и через элемент задержки подключен к информационному входу регистра сдвига, входы сброса вычитающего счетчика, регистра сдвига, установочный вход одновибратора, вторые входы третьего и четвертого элементов ИЛИ соединены с восьмым выходом второго дешифратора, девятьй выход которого соединен с вторым информационным входом первой схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1133593A1 |

| Устройство для возведения в степень | 1982 |

|

SU1076904A1 |

| Устройство для возведения в степень | 1982 |

|

SU1084787A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Устройство для возведения в квадрат | 1977 |

|

SU703807A2 |

| Способ определения индукции магнитного поля в зазоре магнитопровода | 1987 |

|

SU1688211A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1644054A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1675810A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1732305A1 |

УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее регистр основания, блок , возведения десятичной цифры в квадрат, двухразрядный умножитель, десятичный счетчик, преобразователь десятичного числа-в двоичньй код, первую и вторую схемы сравнения, генератор импульсов, триггер реверса, первый элемент И, блок управления, причем блок управления содержит генератор тактов, счетчик, первьш, второй и третий дешифраторы, второй, третий и четвертьм элементы И, счетчик циклов, счетчик тактов, первый и второй триггеры, элемент ИЛИ, группу элементов ИЛИ, триггер операций, выход генератора тактов соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами первого дешифратора, выходы с первого по пятьй которого соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с первого по пятьй выходами второго дешифратора, информационные входы которого соединены с разрядными выходами счетчика циклов, счетный вход которого соединен с выходом второго элемента И, первьш вход которого соединен с выходом генератора тактов и первым входом третьего элемента И, выход которого соединен со счетным входом счетчика тактов, разрядные выходы которого соединены с информационными входами третьего дешифратора, первьй выход которого соединен с первым входом четвертого элемента И, выход которого соедилен с входом сброса счетчика циклов и первым входом элемента ИЛИ, выход которого соединен с первым входом первого триггера, первьй выход которого соединен с вторым входом второго.элемента И, (Л второй вход первого триггера соединен с шестым выходом второго дешифратора, вторым входом элемента ИЛИ и первым входом второго триггера, выход которого соединен с вторым вхо дом четвертого элемента И, первьй выход триггера операций соединен с входа «1 стробирования первого и вто4; рого дешифраторов, второй выход триг гера операций соединен с входом стробирования третьего дешифратора, втоо аь рой выход первого триггера соединен с вторым входом третьего элемента И, выходы элементов ИЛИ группы соединены соответственно с первыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, двухразрядного умножителя, преобразователя десятичного числа в двоичньй код десятичного счетчика, входы выбора операции устройства соединены с первым и вторым входами триггера операций, информационный

1

Изобретение, относится к вычислительной технике и может быть применено в цифровых приборах для обработки результатов измерения (вычисление промежуточных операций).

Известнр устройство для возведения в квадрат, состоящее из регистра основания, матрицы разрядов.

матрицы произведения двух разрядов,накопителя, преобразователя числа в код, генератора импульсов и схемы управления.

Возведение числа в квадрат производится за несколько тактов, которые формируются схемой управления. В де.рвый такт при поступлении числа в

регистр основания матрица разрядов вьдает команду, соответствующую дан ному числу, которая запоминается в накопителе. Во второй такт матрица произведений двух разрядов вьщает константу, соответствующую удвоенному произведению первого разряда на второй, где первый разряд является младшим разрядом числа. Удвоенное произведение преобразуется преобра- зователем числа в код в число-импульсньй код, которьй поступает в определенные разряды накопителя. В третий такт производится умножение первого разряда на третий и суммирование число-импульсного кода, соответствую щего их удвоенному произведению, с цифрами определенных разрядов накопителя . Количество подобных операхщй сложения определяется количеством разрядов числа, которые необходимо возвести в квадрат СОНедостатком данного квадратора является невозможность извлечь из данного числа квадратный корень,

Наиболее близким техническим решением к изобретению является устройство для возведения в квадрат и извлечения квадратного корня, содержащее регистр основания, матрицу возведёния десятичной цифры в квадрат, матрицу произведения двух разрядов, (десятичный счетчик, преобразователь десятичного числа в двоичный код, две схемы сравнения, генератор импульсов, реверсивный счетчик, элемент И, триггер реверсов, блок управления, разрядные выходы реверсивного счетчика соединены с разрядными входами матриц возведения.десятичной цифры в квадрат и произведения двух разрядов, выходы которых соединены соответственно с входами десятичного счетчика и преобразователя десятичного числа в двоичный код, выход которого соединен со счетным входов t десятичного счетчика, выход которого соединен с первыми группами управляющих входов первой и второй схем сравнения, вторые группы управляющих входов которых соединены с разрядными выходами регистра основания.

Извлечение квадратного корня в известном устройстве производится методом последовательных проб за несколько циклов, нач1;ная с единицы 2

Недостатком известного ycтpoйcтвia является большое время, необходимое

для достижения результата при больших значениях подкоренногочисла.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для возведения в квадрат и извлечения квадратного корня, содержащее регистр основания, блок возведения десятичной ци.фры в квадрат, двухразрядный умножитель, десятичный счетчик, преобразователь десятичного числа в двоичный код, первую и вторую схемы сравнения, генератор импульсов, триггер реверса,

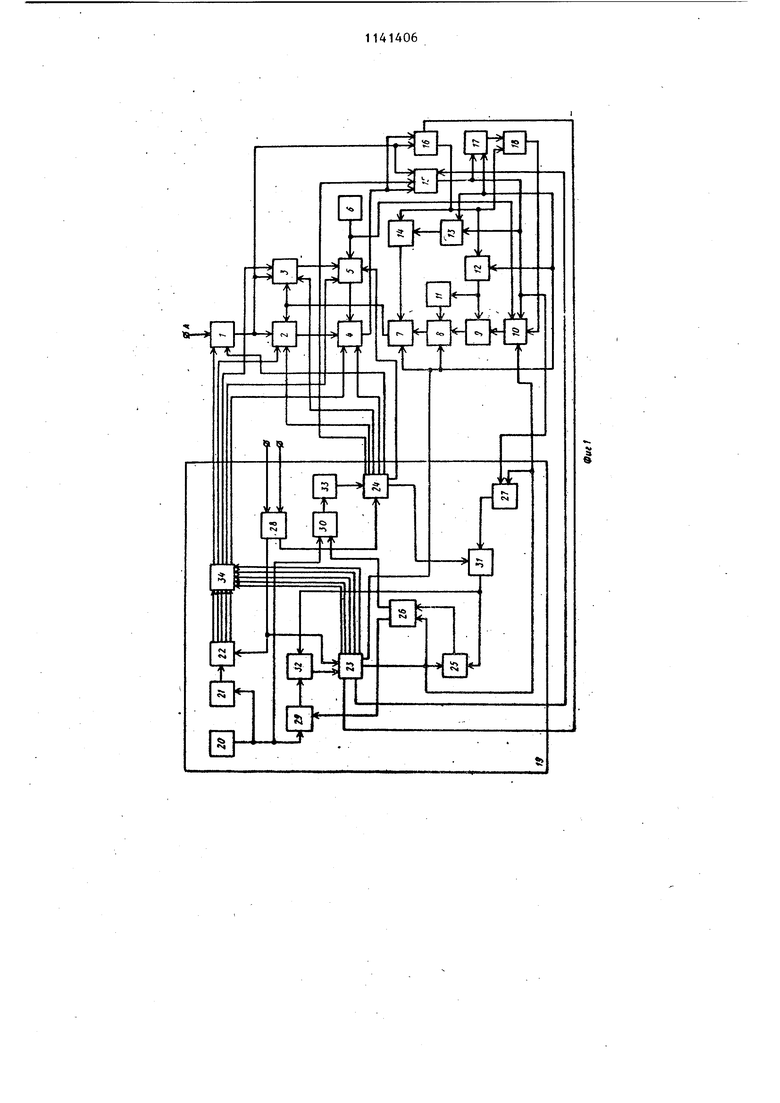

первый, элемент И, блок управления, причем блок управления содержит генератор TaijTOB, счетчик, первый, второй и третий дешифраторы, второй, третий и четвертый элементы И, счетчик циклов, счетчик тактов, первый и второй триггеры, элемент ИЛИ, группу элементов ИЛИ, триггер операций, выход генератора тактов соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами первого дешифратора, выходы с первого по пятый которого соединены с первыми входами эле ментов ИЛИ группы,вторые входы кото- рых соединены с первого по пятый выходами второго деишфратора, информационные входы которого соединены с разрядными выходами счетчика циклов, счетный вход которого соединен с выходом второго элемента И, первый вход которого соединён с выходом генератора тактов и первым входом третьего элемента И, выход которого соединен со счетным входом счетчика тактов, разрядные выходы которого соединены с информационными входами третьего дещифратора, первый выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом сброса счетчика циклов и первъзм входом элемента , выход которого соединен с входом первого триггера, первый выход которого соединен с вторьм входом второго элемента И, второй вход первого триггера соединен с шестым выходом второго дешифратора, вторым входом элемента ИЛИ и первым входом второго триггера, выход которого сое динен с вторым входом четвертого элемента И, первый выход триггера операций соединен с входами стробирования первого и второго дешифрато511ров, второй выход триггера операций соединен с входом стробирования третьего дешифратора, второй выход первого триггера соединен с вторым входом третьего элемента И, выходы элементов ИЛИ группы соединены соответственно с первыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, двух разрядного умножителя, преобразовате- 10 ля десятичного числа в двоичньй код десятичного счетчика, входы выбора операции устройства соединены с первым- и вторым входами триггера операций, информационный вход устройства - с входом установки числа регист ра основания, разрядные выходы которого соединены с первыми разрядными входами блока возведения десятичной цифры в квадрат и двухразрядного умножителя, выход которого соединен с входом преобразователя десятичного числа в двоичный код, выход которого соединен со счетнь1М входом десятично го счетчика, разрядные входы которого соединены с выход-ом блока возведе ния десятичной цифры в квадрат, разрядные выходы регистраоснования сое динен1 1 соответственно с первой группой управляющих входов первой и второй схем сравнения, вторые группы упраЕ- ляющю входов которых соединены соответственно с выходом десятичного счетчика, информационный вход первой схемы сравнения соединен с вторым выходом третьего дешифратора, инфорйацио.чкьй вход второй схемы сравнения - с седьмьпм выходом второго дешифратора, выход первойСхемы сравнения - с первым входом первого элемента И, второй вход которого соединен с шестым выходом второго дешифра тора, третий вход первого элемента И - с выходом генератора импульсов и тактовым входом преобразователя десятичного числа в двоичный код, третий, четвертьй, пятьй, шестой и седьмой выходы третьего дешифратора соединены соответственно с вторыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, двухразрядного умножителя, преобразователя десятичного числа в двоичный код и десятичного счетчика, введены вычитакяций счетчик, сдвиговый регистр, элемент задержки, одновибратор, второй, третий и четвертый элементы ИЛИ и тре6тий триггер, выход которого соединен с четвертым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом сдвига регистра сдвига, разрядные выходы которого соединены соответст венно с разрядными входами вычитающего счетчика, разрядные выходы которого соединены соответственно с вторыми разрядными входами блока возведения десятичной цифры в квадрат и двухразрядного умножителя, счетный вход вычитающего счетчика - с выходоп триггера реверса, первый вход которого соединен с выходом третьего элемента ИЛИ, первьй вход которого соединен с выходом первой схемы сравнения и первым входом четвертого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, второй вход которого соединен с вторым входом триггера реверса, входом запуска одновибратора и выходом второй схемы сравнения, выход одновибратора - с вторым входом второго элемента ИЛИ -и через элемент задержки подключен к информационному входу регистра сдвига, входы сброса вычитающего счетчика, регистра сдвига, установочньш вход одновибратора, вто- рые входы третьего и четвертого элементов ИЛИ соединены с восьмым выходом второго дешифратора, девятьй выход которого соединен с вторым информационным входом первой схемы сравнения. На фиг.1 представлена блок-схема предлагаемого устройства , на фиг.2 блок-схема преобразователя десятичного чис-па в двоичньй код. Устройство для возведения в квадрат и извлечения квадратного корня (фиг.1) содержит регистр 1 основания, блок 2 возведения десятичной цифры в квадрат, двухразрядньй умножитель 3, десятичный счетчик 4, преобразователь 5 десятичного числа в двоичный код, генератор 6 импульсов, вычитакщий счетчик 7, сдвиговый регистр 8, второй элемент ИЛИ 9, первьй элемент И 10, элемент 11 задержки, одновибратор 12, третий элемент ИЛИ t3, триггер 14 реверса,первую 15 и вторую 16 схемы сравнения, четвертьй элемент ИЛИ 17, третий триггер 18, блок 19 управления, генератор 20 тактов, счетчик 21, первьй 22, второй 23 и

третий 24 дешифраторы, первый элемент ИЛИ 25, первый 26 и второй 27 триггеры, триггер 28 режимов, второй 29, третий 30 и четвертый 31 элементы И, счетчик 32 циклов, счетчик 33 тактов и группу элементов ИЛИ 34.

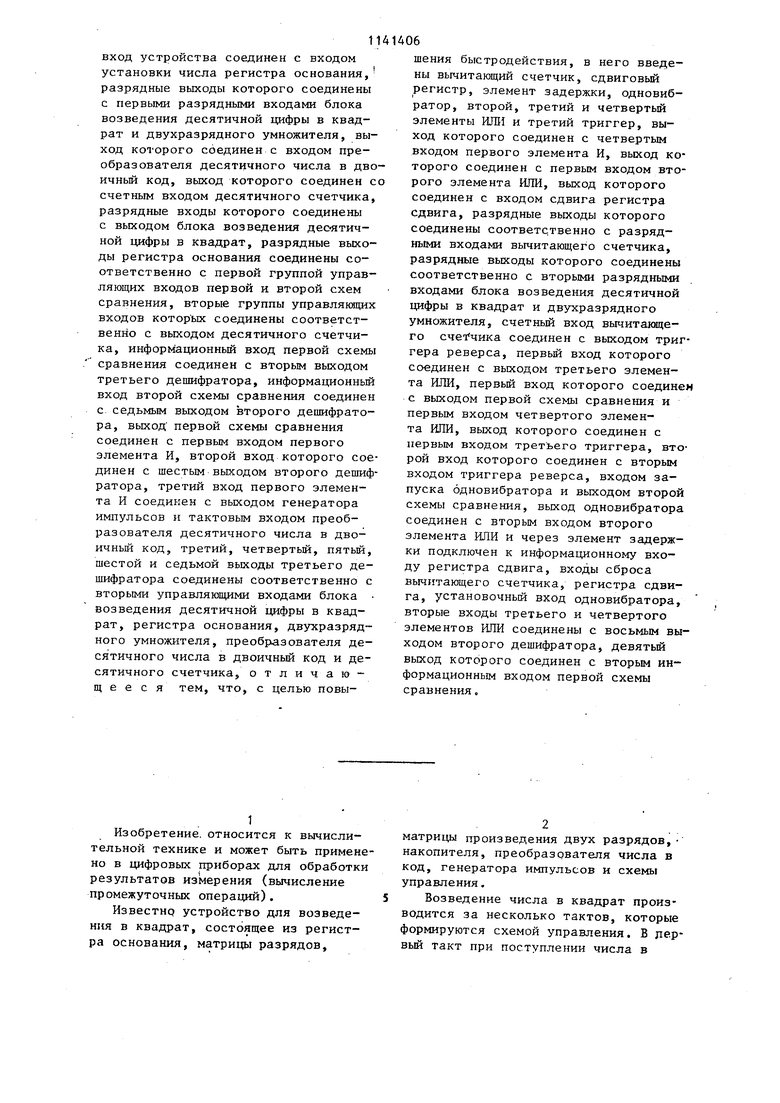

Преобраэователь десятичного числа в двоичный код (фиг.2) содержит сдви говый регистр 35, схемы И 36 и 37, схему ИЛИ 38, триггер 39 и схему И 40.

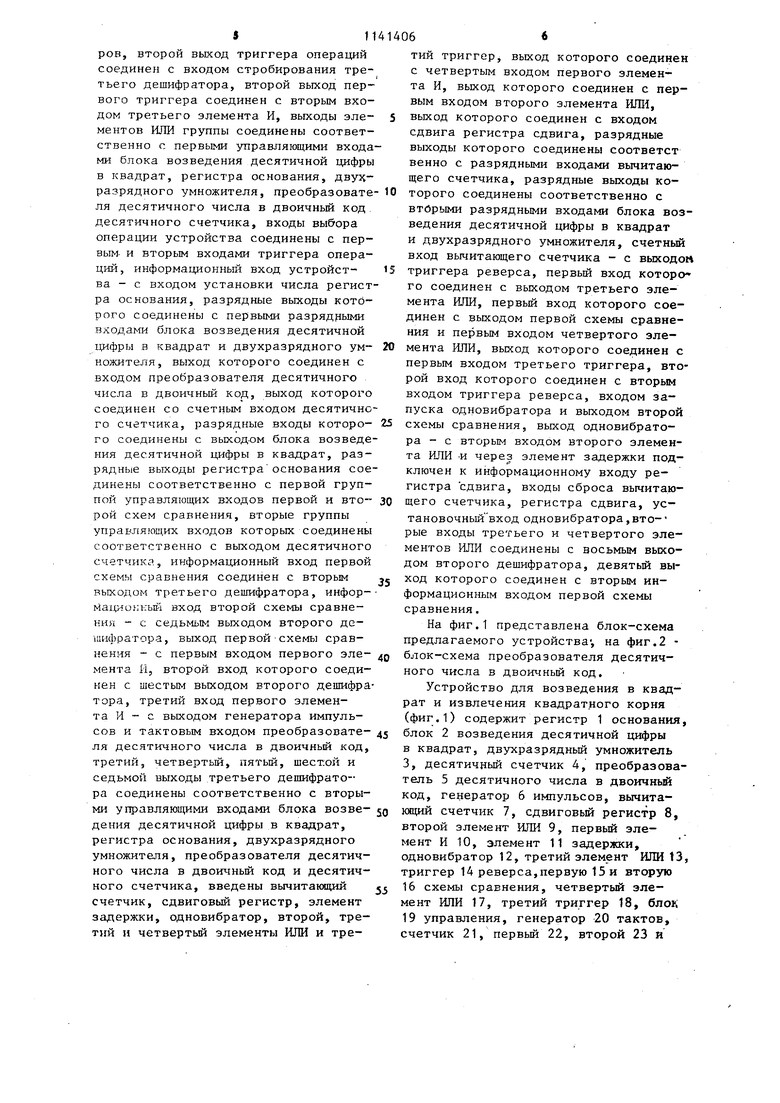

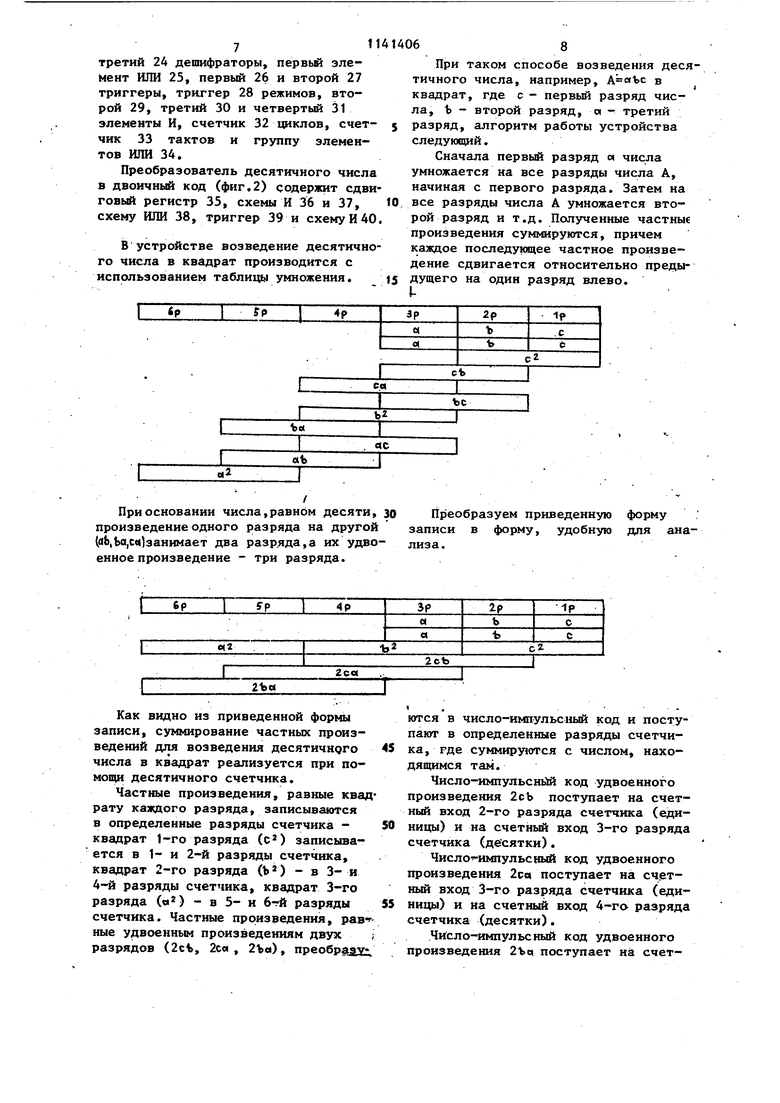

В устройстве возведение десятичного числа в квадрат производится с использованием таблицы умножения.

При основании числа,равном десяти, зо произведение одного разряда на другой (аЬ,Ьа,с«|)занимает два разряда,а их удвоенное произведение - три разряда.

Как видно из приведенной формы записи, суммирование частных произведений для возведения десятичного числа в квадрат реализуется при помощи десятичного счетчика.

Частные произведения, равные квад рату каждого разряда, записываются в определенные разряды счетчика квадрат 1-го разряда (с) записывается в 1- и 2-й разряды счетчика, квадрат 2-го разряда (t) - в 3- и 4-й разряды счетчика, квадрат 3-го разряда («) - в 5- и 6-гй разряды счетчика. Частные произведения, удвоенным произведениям двух ; разрядов (2сЪ, 2сс« , 2Ъс|), преобразх:

При таком способе возведения десятичного числа, например, в квадрат, где с - первый разряд числа, Ъ - второй разряд, я - третий разряд, алгоритм работы устройства следующий.

Сначала первый разряд п числа умножается на все разряды числа А, начиная с первого разряда. Затем на все разряды числа А умножается второй разряд и т.д. Полученные частные произведения суммируются, причем каждое послеДукицее частное произведение сдвигается относительно предыдущего на один разряд влево.

Преобразуем приведенную форму записи в форму, удобную для анализа .

ются в число-импульсный код и поступают в определенные разряды счетчика, где суммиру5отся с числом, находящимся там.

Число-импульсньЙ код удвоенного произведения 2сЬ поступает на счетный вход 2-го разряда счетчика (единицы) и на счетный вход 3-го разряда счетчика (десятки).

Число-импульсный код удвоенного произведения 2са поступает на сч.етный вход 3-го разряда счетчика (единицы) и на счетный вход 4-га разряда счетчика (десятки).

Число-импульсный код удвоенного произведения поступает на счет- ный вход 4-го разряда счетчика (единицы) и на счетный вход 5-го разряда счетчика (десятки). Извлечение квадратного корня в предлагаемом устройстве из десятичкого числа А производится методом по следовательных проб за несколько цик лов. Сначала определяется старший п-й разряд, затем (п-1)-й разряд и т.д. Последним находится первый разряд. Для этого последовательно возводятся в квадрат числа натурального ряда а, ... ад, отличакядиеся одно от другого на одну градацию (единицу) начиная с п-го (старшего) разряда, и сравниваются с числом А. Старший п-й разряд корня определяется следукщим образом. Последовательно возводятся в квадрат разрядные числа, причем в (п-1)-м, (п-2)-м,...5 разрядах числа равны нулю, а в п-м разряде в квадрат возводятся числа натурального ряда (и, dj, ..,, «э), отличающиеся одна от другого на одну градацию (единицу) и сравниваются с числом А. Последовательность таких операций продолжается до тех пор, пока выполняется не .. o)iA, т, равенство (« , о, о, (a, , О, о. осуществляется условие ...о). Операция определения старшего разряда корня заканчивается в тот момент, когда выполняется неравенство (а, о, о, ...о)А. Старший разряд корня будет меньше на одну градацию (единицу) того числа а„ , когда была получена положительная разность, т.е. старший разряд корня буЭп (i-1). (п-1)-й разряд корня определяется следующим образом. Последовательно возводятся в квадрат разрядные числа, причем в ((п-2), (п-3),...,1 разрядах числа равны нулю, в п-м раз ряде число равно а (i-1), а в (п-1)-м разряде в квадрат возводятся числа натурального ряда «,,«2 «5, отличакщиеся одно от другого на одну градацию (единицу), и срзвниваются с числом А. Последовательность таких операций продолжается до тех пор, пока выполняется неравенство , т.е. осуществляется условие (a.j, а(п.1)д, .... о, ... о)-МО. Операция определения (n-l)-ro ра ряда корня заканчивается в тот момент, когда вьтолнено неравенство пвч (п-1М ), (п-1)-й разряд корня будет меньше на одну градацию (единицу) того числа .,. , когда бьша получена положительная разность, т.е. (п-1)-й разряд корня будет а(„.|,.| . Таким образом определяются последующие разряды корня вплоть до первого разряда. Устройство работает следующим образом. 1. Операция возведения в квадрат. При поступлении 1-го импульса из генератора 20 тактов в счетчик 21 первый дешифратор-. 22 вьщает разрешающий потенциал через группу элементов ИЛИ 34 на регистр 1 основания, по которому в него записывается число , которое необходимо возвести в квадрат. При поступлении в счетчик 21 2-го импульса из генератора 20 тактов первый дешифратор 22 через группу элементов ИЛИ 34 вьщает разрешающий потенциал на блок 2 возведения десятичной цифры в квадрат. По этому сигналу квадрат каждого разряда (а , Ь , с ) числа А поступает на соответствующие разрядные входы десятичного счетчика 4. При поступлении в счетчик 21 3-го импульса из генератора 20 тактов первый дешифратор 22 через группу элементов ИЛИ 34 вьщает разрешающий сигнал на двухразрядный умножитель 3 и на преобразователь 5 десятичного числа в двоичный код. По этому сигналу удвоенное произведение 2сЬ (единицы) из двухразрядного умножителя 3 поступает на преобразователь 5 десятичного числа в двоичньй код. Затем преобразованное число импульсов поступает на десятичный счетчик 4. При поступлении в счетчик 21 4-го импульса из генератора 20 тактов первый дешифратор 22 через группу элементов ШЖ 34 вьщает разрешаилщй сигнал на двухразрядный умножитель 3 и на преобразователь 5 десятичнрго числа в двоичный код. По этому сигналу удвоенное произведение 2сЬ (десятки) из двухразрядного умножителя 3 поступает на преобразователь 5 десятичного числа в двоичный код. Затем преобразованное число импульсов по-г ступает на десятичный счетчик 4. При поступлении 5- и 6-го импульсов из генератора 20 тактов в счетчик 21 производится преобразование удвоенного произведения 2рс в пропорциональное число- импульсов, которые поступают в десятичньй счетчик 4. При поступлении 7- и 8-го импульсов из генератора 20 тактов в счетчик 21 первый дешифратор 22 через группу элементов ИЛИ 34 вьщает разре шающий сигнал на двухразрядный умножитель 3 и на преобразователь 5 деся тичного числа в двоичный код, по которому производится преобразование удвоенного произведения 2Ьс, находящегося в двухразрядном умножителе 3,в пропорциональное число импульсон,которые поступают в десятичньй счетчик 4. 2. Операция извлечения квадратного корня. При поступлении 1-го импульса из генератора 20 тактов в счетчик 32 циклов второй дешифратор 23 вьщает сигнал начальной установки, устанавливающий все блоки устройства, имеющие цифровую память, в исходное соетояние. При поступлении в счетчик 32 циклов второго импульса из генератора 20 тактов второй дешифратор 23 через группу элементов ИЛИ 34 вьщает разрешакщий сигнал на регистр 1 {Основания, По этому сигналу в ре- ;гистр 1 основания записывается чис|по , из которого необходимо извлечь квадратньй корень. Кроме того, по сигналу второго дешифратора 23 первьй элемент И 10 вьщает сигнал, поступакщий через второй элемент ИЛИ 9 на сдвиговьй регистр 8, а первьй элемент ИЛИ 25 вьщает сигнал на первый триггер 26. Из сдвигового регист ра 8. в старший п-й разряд вычитающего счетчика 7 записывается единица. Выходной сигнал триггера 26 запрещает прохождение сигналов генератора 20 тактов через второй элемент И 29 на счетчик 32 циклов и разрешает про хождение этих сигналов через второй элемент И 30 на счетчик 33 тактов. По 1-му импульсу, поступившему из генератора 20 тактов в счетчик 33 тактов через второй элемент И 30, третий дешифратор 24 вьщает разрешаюощй потенциал на блок 2 возведения десятичной цифры в квадрат. По этому сигналу квадрат каждогоразряда (« 2,0) числа (1,0,..i,0), записанно го в вычитающий счетчик 7, поступает на соответствующие входы определенных двоично-десятичных счетчиков десятичного счетчИка 4. При поступлении в счетчик 33 тактов 2-го импульса из генератора 20 тактов третий дешифратор 24 вьщает разрешакщий сигнал на двухразрядньй умножитель 3 и преобразователь десятичного числа в двоичный код 5. По этому сигналу удвоенное произведение 2сЬ (единицы) из двухразрядного умножителя 3 поступает на преобразователь 5 десятичного числа в двоичньй код. . При поступлении в счетчик 33 тактов 3-го импульса из генератора 20 тактов третий дешифратор 24 вьщает разрешающий сигнал на двухразрядньй умножитель 3 и преобразователь десятичного числа в двоичньй код 5. По этому сигналу удвоенное произведение 2сЪ (десятки) из двухразрядного умножителя 3 поступает на преобразователь 5 десятичного числа в двоичньй код. При поступлении 4- и 5-го импульсов из генератора 20 тактов в счетчик 33 тактов производится преобразова- ние удвоенного произведения 2cq в пропорциональное число импульсов, которое поступает в десятичный счетчик 4. При поступлении 6- и 7-го импульсов из генератора 33 тактов третий дешифратор 24 вьщает разрешающий сигнал на двухразрядньй умножитель 3 и преобразователь 5 десятичного числа в двоичньй код, по которому производится преобразование удвоенного произведения 2Ъс(, находящегося в двухразрядном умножителе 3, в пропорциональное число и fflyльcoв, которые поступают в десятичньй счетчик 4. При поступлении 8-го импульса из генератора 20 тактов в счетчик 33 тактбв третий дешифратор 24 вьщает разрешающий сигнал на первую схему 15 сравнения, по которому производится сравнение числа А, хранящегося в регистре 1 основания, из которого производится извлечение квадратного корня, и числа (аЬс) находящегося в десятичном счетчике 4. Если А7(аЪс)2, первая схема 15 сравнения вьщает сигнал на первьй элемент И 10. Первьй элемент И 10 через второй элемент ИЛИ 9 вьщает сигнал на сдвиговьй регистр 8, который вьщает импульс, поступающий на счетньй вход п-то разряда вычитающего счетчика 7, .е. в вычитаюгцем i счетчике устанавливается число (2,0, ...,0). Кроме того, 8-й Импул.ъс, поступаю щий в счетчик 33 тактов из генератора 20 тактов, устанавливает счетчик 33 тактов в исходное состояние. Последовательность работы устройства при поступлении следующих групп из 8 импульсов на счетчик 33 тактов аналогична рассмотренной. Когда будет выполнено условие А(о( , О,..,, 0), первая схема 15 сравнения устанавливает триггер 27 в единичное сос тояние и запрещает прохождение сигналов из первого элемента И 10 через второй элемент ИЛИ 9 на сдвиговьм регистр 8, В результате второй триггер 27 разрешает прохождение сигнала третьего дешифратора 24 через четвер тый элемент И 31 и первьй элемент ИЛИ 25 на единичньй вход первого триггера 26, Триггер 26 разрешает прохожде ние сигналов генератора 20 тактов че рез второй элемент И 29 на вход счет чика 32 циклов и запрещает прохождение этих сигналов через третий элемент И 30 на вход счетчика 33 тактов Сигнал генератора 20 тактов через второй элемент И 29 поступает на счетчик 32 циклов. По сигналу второго дешифратора 23 вторая схема 16 сравнения устанавливает в единичное состояние триггер 14 реверса. Кроме того, по сигналу второй схемы 16 сравнения срабатывает одновибратор 12 и выдавт одиночный импульс«который через второй элемент ИЛИ 9 и сдвиговьй регистр поступает на счетный вход п-го разряда вычитающего счетчика 7. Так как триггер 14 ревер са находится в единичном состоянии, то из старшего разряда производится вычитание единицы. Кроме того, сигнал одновибратора 12 через время t, определяемое параметраг-ш элемента 11 задержки, переключает сдвиговьй регистр 8. На этом нахождение старшего п-го разряда квадратного корня заканчивается. При поступлении следующего импуль са из генератора 20 тактов на счетчик 32 циклов второй дешифратор 23 вьдает. управляющий сигнал на первую схему 15 сравнения, разрешает прохождение сигналов через первый элемент И 10 и второй элемент ИЛИ 9 на сдвиговьй регистр 8. Сигнал первой схемы 15 сравнения через третий элемент ИЛИ 13 поступает на нулевой вход триггера 14 реверса, которьй выдает разрешающий потенциал на шину сложения вычитающего счетчика 7, Из сдвигового регистра 8 на счетньй вход (п-1)-го разряда вычитающего счетчика 7 поступает импульс, т.е. в (п-1)-й разряд вычитающего счетчика 7 записывается единица. Выходной сигнал первого триггера 26 запрещает прохож;,ение сигналов генератора 20 тактов через второй элемент И 29 на счетчик 32 циклов и разрешает прохождение- этих сигналов через третий элемент И 30 на счетчик 33 тактов. Дальнейшая работа устройства по нахождению (п-1)-го разряда происходит таким же образом, как и при нахождении п-го разряда. Нахождение первого разряда корня ничем не отличается от нахождения предьщущих разрядов корня. Когда будет вьтолнено условие А(а. , , с-), первая схема 15 сравнения выдает запрещающий сигнал на первьй элемент И 10 и устанавливает второй триггер 27 в единичное состояние. Через четвертьй элемент И 31 пройдет сигнал третьего дешифратора 24, который установит в единичное состояние первьй триггер 26„ Последний выдает разрешающий потенциал.на второй элемент И 29 и запрещающий потенциал на третий элемент И 30,, Сигнал генератора 20 тактов поступит через второй элемент И 29 на счетчик 32 циклов и переведет его в нулевое состояние. На этом операция извлечения квадратного корня из десятичного числа заканчивается. Таким образом, введение в устройство вычитающего счетчика, сдвигового регистра, элемента задержки, одновибратора, трех элементов ИЛИ; триггера позволяет уменьшить время вычисления квадратного корня путем поразрядного формирования результата.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ | 0 |

|

SU391560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1982 |

|

SU1084784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-23—Публикация

1982-07-05—Подача