I

Изобретение относится к радиотехнике и может использоваться в устройствах передачи сигналов, в частности в формирователях кода Морзе.

Известно устройство для формирования кода Морзе, содержащее триггер, блок элементов И-ИЛИ, первый блок памяти, основной элемент ИЛИ, генератор тактовых импульсов, шифратор, стартстопный блок, при этом выход генератора тактовых импульсов подключен к первому входу стартстопного блока, соответствующие выходы шифратора соединены с первым и вторым входами первого блока памяти 1.

Однако известное устройство не обеспечивает формирования семизначного телеграфного кода.

Цель изобретения - обеспечение возможности формирования семизначного телеграфного кода.

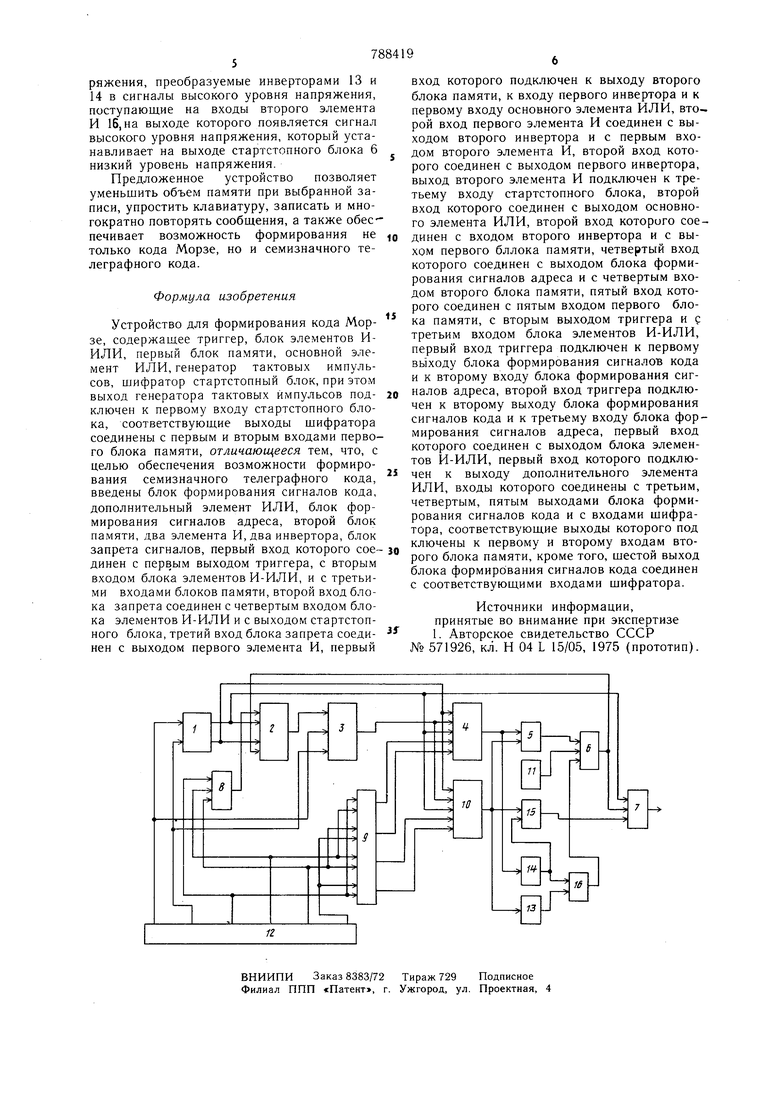

Для достижения этой цели в известное устройство введены блок формирования сигналов кода, дополнительный элемент ИЛИ, блок формирования сигналов адреса, второй блок памяти, два элемента И, два инвертора, блок запрета сигналов, первый вход которого соединен с первым выходом триггера, с вторым входом блока элементов ИИЛИ и с третьим-и входами блоков памяти, второй вход блока запрета соединен с четвертым входом блока элементов И-ИЛИ и с выходом стартстопного блока, третий вход блока запрета соединен с выходом первого элемента И, первый вход которого подключен к выходу второго блока памяти, к входу первого инвертора и к первому входу основного элемента ИЛИ, второй вход первого элемента И соединен с выходом второго инШ вертора и с первым входом второго элемента И, второй вход которого соединен с выходом первого инвертора, выход второго эле мента И подключен к третьему входу стартстопного блока, второй вход которого соединен с выходом основного элемента ИЛИ, вто

рой вход которого соединен с входом второго инвертора и с выходом первого блока памяти, четвертый вход которого соединен с выходом блока формирования сигналов адреса и с четвертым входом второго блока

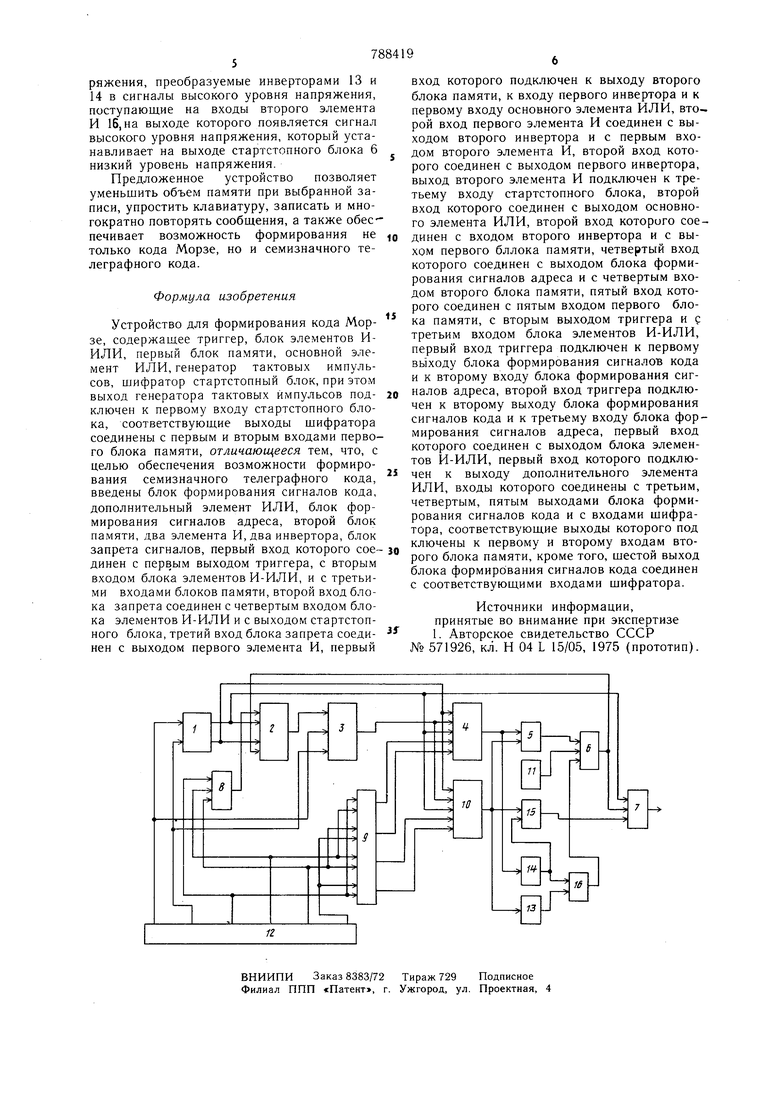

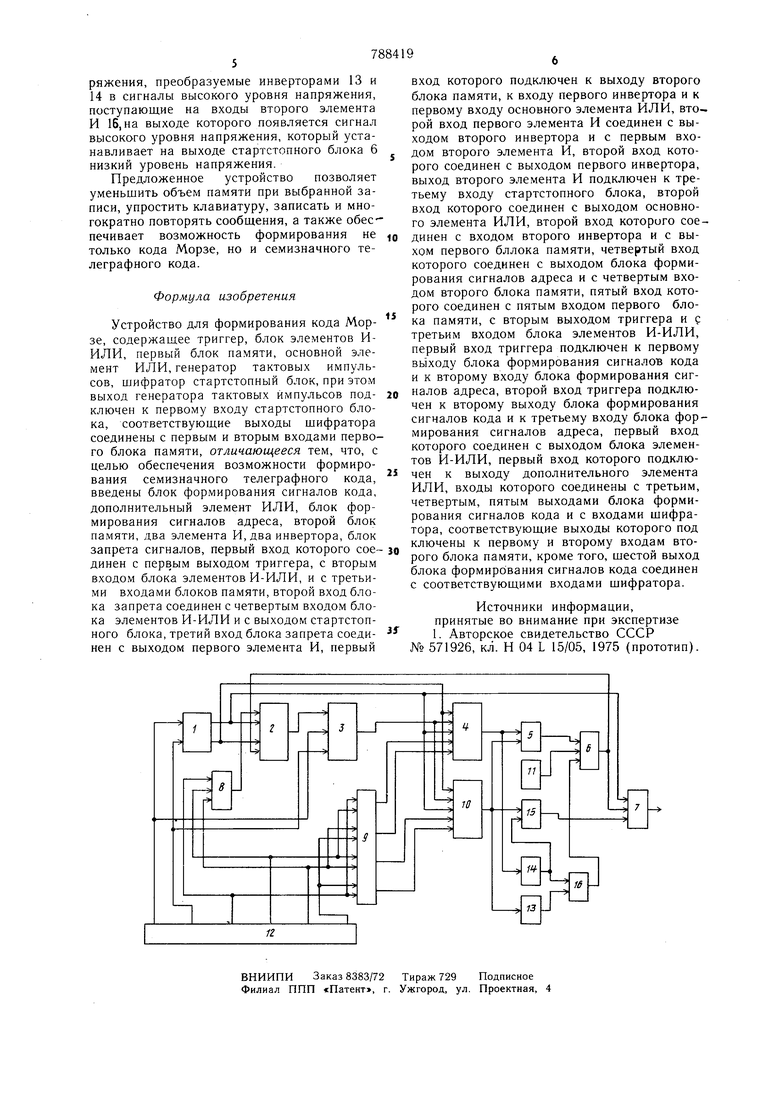

20 памяти, пятый вход которого соединен с пятым входом первого блока памяти, с вторым выходом триггера и с третьим входом блока элементов И-ИЛИ, первый вход триггера подключен к первому выходу блока формирования сигналов кода и к второму входу блока формирования сигналов адреса, второй вход триггера подключен к второму выходу блока формирования сигналов кода и к третьему входу блока формирования сигналов адреса, первый вход которого соединен с выходом блока элементов И-ИЛИ, первый вход которого подключен к выходу дополнительного элемента ИЛИ, входы которого соединены с треьим, четвертым, пятым выходами блока формирования сигналов кода и с входами шифратора, соответствующие выходы которого подключены к первому и второму входам второго блока памяти, кроме того, шестой выход блока формирования сигналов кода соединен с соответствующими входами щифратора. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство для формирования кода Морзе содержит триггер 1, блок 2 элементов ЙИЛИ, блок 3 формирования сигналов адреса первый блок 4 памяти, (хновной элемент ИЛИ 5, стартстопный блок 6, блок 7 запрета сигналов, дополнительный элемент ИЛИ 8 шифратор 9, второй блок 10 памяти, генератор 11 тактовых импульсов, блок 12 формирования сигналов кода, первый и второй инверторы 13, 14 соответственно, первый и второй элементы И 15, 16 соответственно. Устройство работает следующим образом. В режиме записи с первого выхода блока 12 подается высокий уровень напряжения на первый вход триггера 1 и на второй вход блока 3. При этом с первого выхода триггера I высокий уровень напряжения поступает на второй вход блока 2, разрешая прохождение высокого уровня напряжения с выхода дополнительного элемента ИЛИ 8 на первый вход блока 3. Одновременно высокий уровень напряжения поступает на третьи входы блоков 4, 10 и на первый вход блока 3. Одновременно высокий уровень напряжений поступает на третьи входы блоков 4, 10 и на первый вход блока 7, запрещая прохождение сигналов на выход устройства с второго входа блока 7. Блок 3 устанавливается в исходное состояние и подготавливает к записи первые ячейки памяти блоков 4 и 10. Подачей сигналов с третьего, четвертого, пятого и шестого выходов блока 12 производится запись необходимого текста. В режиме считывания с второго выхода блока 12 высокий уровень напряжения поступает на третий вход блока 3 и на второй вход триггера 1, при этом триггер 1 устанавливается в нулевое положение и высокий уровень напряжения с второго выхода триггера 1 поступает на третий вход блока 2, разрешая прохождение высокого уровня напряжения подаваемого на четвертый вход блока 2 с выхода стартстопного блока б на первый вход блока 3. Одновременно высокий уровень напряжения с второго выхода триг гера 1 поступает на пятые входы блоков 4, 10. Блок 3 устанавливается в исходное состояние и включает первые ячейки амяти бло ков 4 и 10. Сигналы, записанные в первых ячейках памяти с выходов блоков 4, 10, поступают на соответствующие входы основного элемента ИЛИ 5 и на инверторы 13, 14, При считывании информации .с первой ячейки памяти блока 4 на его выходе получается низкий уровень напряжения, при считывании с первой ячейки памяти блока 10 на его выходе получается высокий уровень напряжения. При поступлении указанных сигналов на входы основного элемента ИЛИ 5 на его выходе получается сигнал низкого уровня напряжения, поступающий на второй вход стартстопного блока 6. На первый вход стартстопного блока 6 с выхода генератора 11 поступают тактовые .импульсы с длительностью и скважностью, равной «1. При подаче на первый вход стартстопного блока 6 низкого уровня напряжения последний генерирует один импульс низкого напряжения и один импульс высокго напряжения соответствующих длительностей, которые поступают на второй вход блока 7 и на четвертый вход блока 2. Сигнал низкого уровня напряжения , поступающий с выхода блока 4 на вход второго инвертора И, на выходе последнего преобразуется в сигнал высого уровня напряжения и поступает совмест но с сигналом высокого уровня напряжения с выхода блока 10 на входы первого элемента И 15, на выходе которого получается сигнал высокого уровня напряжения, поступающий на третий вход блока 7 и запрещаю щий прохождение сигналов с выхода стартстопного блока 6 на выход устройства. На выходе устройства получается пауза суммарной длительности. При появлении на выходе блока 4 сигнала высокого уровня напряжения, а на выходе блока 10-сигнала низкого уровня напряжения, на выходе основного элемента ИЛИ5 воспроизводится сигнал низкого уровня напряжения, и стартстопный блок 6 генерирует один импульс низкого уровня напряжения и один импульс высокого уровня напряжения соответствующих длительностей, которые поступают на второй вход блока 7. При этом на выходе первого элемента И 15 получается сигнал низкого уровня напряжения, который, поступая на третий вход блока 7, разрешает прохождение сигналов с выхода стартстопного блока 6 на выход устройства. На выходе устройсва воспроизводится пауза и сигнал точки или тире соответствующих длительностей. После окончания сигнала высокого уровня напряжения на выходе стартстопного блока 6 происходит переключение блока 3 и считывание информации со следующих ячеек памяти блоков 4 и 10. При считывании сигнала конца записи на выходах блоков 4, 10 появляются сигналы низкого уровня нап

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов кода морзе | 1975 |

|

SU574862A1 |

| Устройство для формирования кода морзе | 1975 |

|

SU571926A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Шифратор | 1980 |

|

SU920835A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ КОДОВОЙ РЕЛЬСОВОЙ ЦЕПИ | 1991 |

|

RU2005639C1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| Биотехническое адаптируемое устройство для бесклавишного ввода информации | 1987 |

|

SU1576901A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

Авторы

Даты

1980-12-15—Публикация

1978-12-05—Подача