(54) ШИФРАТОР

1

Изобретение относится к вычислительной

технике и может применяться ,в автоматизированных системах управления контроля и обработки информации.

Известен шифратор, содержащий блок адресов, мультиплексор, триггеры и логические элементы И, который фиксирует только факт появления входного сигнала 1.

Известен шифратор, содержащий адресный блок, выполненный из каналов адресации, каждый из которых содержит адресный блок, выполненный из дешифратора, каналов адресации, каждый из которых содержит-ячейку памяти, элемент считывания, формирователь входных сигналов и все каналы, кроме первого содержат элемент ИЛИ. При поступлении сигналов на входные шины шифратора при считывании на выходе шифратора появляется код адреса, соответствующий номеру шины, на которой появился, сигнал. Если на входные шины шифратора сигнал не поступает, то коды адреса соответствующих номеров шин на выходе шифратора отсутствуют 2.

При использовании такого шифратора в устройствах автоматизированных систем управления, контроля и обработки инфор- ;

мации фиксируется только факт появления входного сигнала и преобразовывается в код адреса ячеек памяти, на которые поступили входные сигналы, но не преобразовываются в код параметры этого сигнала.

Цель изобретения - расширеше функциональных возможностей шифратора, а именно преобразование в код временных параметров периодических сигналов а входных шинах шифратора.

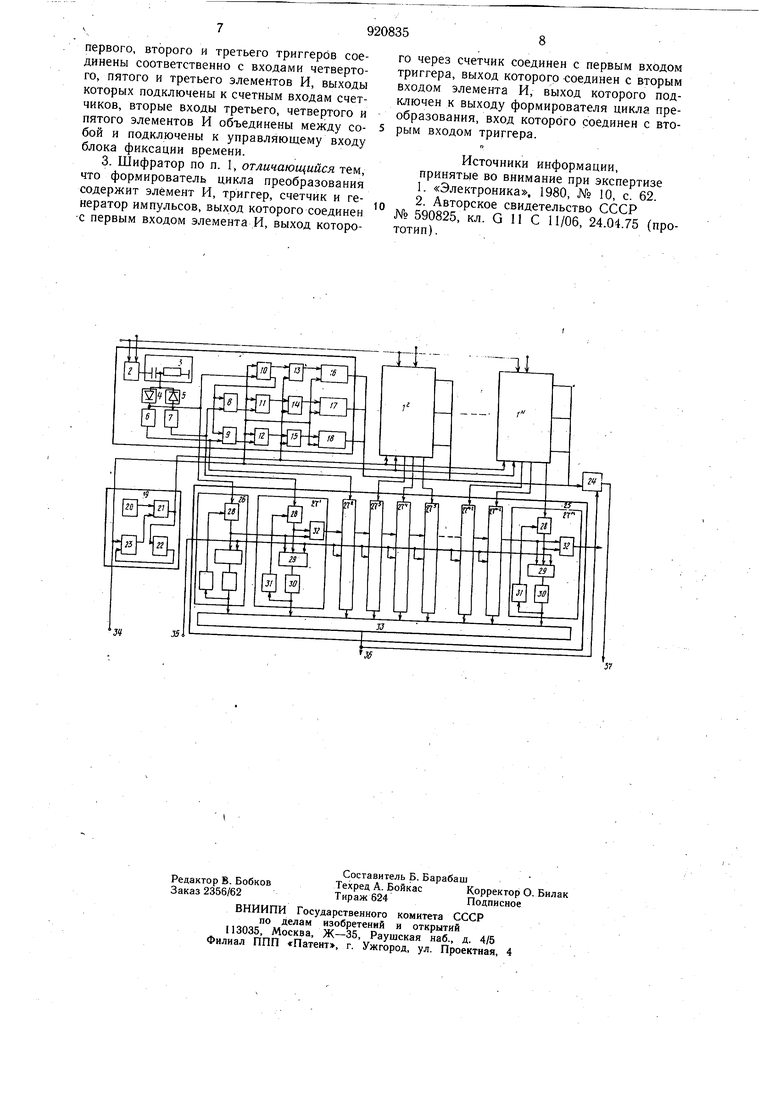

Поставленная цель достигается тем, что в шифратор, содержащий адресный блок, выполненный из дешифратора и каналов адресации, введены мультиплексор, входная шина «Начало преобразования, блоки фиксации времени и формирователь цикла преобразования, выход которого соединен с установочными входами блоков фиксации времени, информационные выходы которых подключены к информационной шине мультиалексора, а адресные выходы соединены с соответствующими входами каналов адресации адресного блока, а входная шийа «Начало преобразования соединена с входом формирователя цикла преобразования и управляющими входами блоков фиксации времени, выход адресного блока соединен с адресной шиной мультиплексора. Кроме того, каждый блок фиксации врейени -содержит компаратор, дифференцирующую цепочку, формирователи импульсов, элементы И, триггеры и счетчики, выход компаратора соединен через дифференцирующую цепочку с формирователями импульсов, выход перого из них соединен через делитель частоты с первым входом первого элемента И, выход которого соединен с первым входом первого триггера, выход первого формирователя импульсов также соединен с-первым входом третьего триггера, один выход которого соединен с вторыми входами первого и второго элементов И, а другой выход соединен с первым входом третьего элемента И вь1ход второго формирователя импульсов че рез инвертор соединен с входом второго элемента И, выход которого соединен с первым входом второго триггера, второй вход которого соединен с вторыми входами других триггеров, с установочным входом блока фиксации времени и установочными входами счетчиков, выходы которых подключены к информационным выходам блока фиксации времени, к соответствующим адресным выходам которого подключены выходы первого формирователя импульсов, выход инвертора и выход делителя частоты, выходы первого второго и третьего триггеров соединены соответственно с входами четвертого, пятого и третьего элементов И, выходы которых подключены к счетным входам счетчиков, вторые входы третьего, четвертого и пятого элементов И объединены между собой и подключены к управляющему входу блока фиксации времени причем формирователь цикла преобразования содержит элемент И, триггер, счетчик и генератор импульсов, выход которого соединен с первым входом элемента И, выход которого через счетчик соединен с первым входом триггера, выход которого соединен с вторым входом элемента И , выход которого является выходом формирователя цикла преобразования, вход которого соединен с вторым входом триггера. На чертеже представлена структурная схема щифратора. Шифратор содержит 1, Р,... блоков фиксации времени, каждый из которых содержит компаратор 2, дифференцирующую цепрчку 3, формирователи 4 и 5 импульсов, делитель 6 частоты на два, инвертор 7, элементы И 8 и 9, триггеры 10 - 12, элементы И 13-15, счетчики 16-18; формирователь 19 цикла преобразования, состоящий из генератора 20 импульсов, элемента И 21, счетчика 22 и триггера 23; мультиплексор 24; блок адресов 25, содержащий 3N каналов 26, 27, 27 ...27 адресации,, причем каждый канал состоит из ячейки 28 памяти, элемента 29 считывания, формирователя 30 входных сигналов и формирователя 31 сигналов сброса, а все каналы адресации, кроме первого, содержат элемент ИЛИ 32, кроме того, блок адресов содержит дещифратор 33, входные щины щифратора «Начало преобразования 34 и «Разрешение считывания 35. Входами щифратора являются входы компараторов блоков фиксации времени. Выходами устройства являются выходные шины «Код адреса счетчика 36 и «Параллельный код величины 37. Шифратор работает следующим образом. При подаче сигнала на шину 34 триггер 23 формирователя 19 цикла преобразования, триггеры 10-12 и счетчики 16-18 блоков 1, 1 ... 1 фиксации времени переходов сигнала через заданный уровень устанавливаются в исходное состояние. При этом на вход элемента И 21 с единичного выхода триггера 23 поступает сигнал, разрешающий прохождение через него импульсов с выхода генератора 20 на вход счетчика 22, а с единичных выходов триггеров 10-12 на входы элементов И 13-15 поступают сигналы, разрешающие прохождение импульсов с выхода элемента И 21 через элементы И 13-15 на входы счетчиков 16-18, т.е. начинается отсчет интервала времени. Входные сигналы поступают на первые входы компараторов 2 блоков 1 , 1 , ... 1 фиксации времени, предназначенных для фиксации времени переходов сигнала через заданный уровнь; на вторые входы всех компараторов поступает опорное напряжение Uon. При превышении входным сигналом заданного уровня компаратор 2 принимает единичное состояние. При этом с помощью дифференцирующей цепочки 3 и формирователя 4 импульсов (диод) формируется импульс, соответствующий переднему фронту входного импульса или нулевой фазе входного синусоидального сигнала и поступающий на нулевой вход триггера 10 и на вход ячейки 28 памяти первого канала 26 адресации блока 25 адресов, Триггер 10 устанавливается в нулевое состояние, снимая тем самым разрешение прохождения импульсов генератора 20 через элемент И 13 на вход счетчика 16. Таким образом, в счетчике 16 фиксируется код времени с момента появления первого переднего фронта входного сигнала. Одновременно сигнал с нулевого выхода триггера 10 поступает на входы элементов И 8 и 9 и разрешает прохождение через них сигналов на нулевые входы триггеров 11 и 12, тем самым обеспечивая фиксацию интервалов в последовательности; передний фронт - в счетчике 16, задний фронт - в счетчике 17, второй передний фронт - в счетчике 18. Ячейка 28 памяти, зафиксировав сигнал на своем входе, своим выходным напряжением открывает элемент 29 считывания и закрывает по третьему запрещающему входу

элемент 29 считывания второго канала 27 адресации и через элементы ИЛИ 32 - остальных каналов 27 ...27 адресации. При подаче сигнала на шину 35 он проходит только через элемент 29 считывания и поступает на формирователь 30 входных сигналов, с выхода которого подается на вход формирователя 31 сброса и на вход дешифратора 33, где превраш,ается в код адреса ячейки 28 памяти и поступает на выход устройства и на адресную шину мультиплексора 24, при этом мультиплексор подключает на шину 37 выход параллельного кода счетчика 16. Таким образом, на момент первого переднего фронта сигнала на входной шине схемы 1 на выходных шинах устройства зафиксирован код номера счетчика, в котором закончен отсчет временного интервала, и код величины временного интервала. Сигнал с выхода формирователя 31 сигнала сброса устанавливает в «О ячейку 28 памяти. Тем самым снимается сигнал с запрещаюшего входа элемента 29 считывания второго канала 27 шифрации.

При обратном переходе сигнала на входной шине компаратора 2, когда сигнал становится меньше, чем Upn, компаратор 2 возвращается в нулевое состояние. При этом с помошью дифференцирующей цепочки 3, формирователя 5 импульсов и инвертора 7 формируется импульс, соответствующий заднему фронту входного импульса, он поступает на вход ячейки 28 памяти канала 27 блока 25 адресов, и через элемент И 8 поступает на нулевой вход триггера 11, устанавливая его в нулевое состояние. Тем самым сигнал, разрешающий прохождение импульсов генератора на вход счетчика 17, снимается со входа элемента И ,14, т.е. в счетчике 17 фиксируется код времени с момента начала преобразования до момента появления заднего фронта входного сигнала.

Ячейка 28 памяти второго канала 27 адресации, зафиксировав входной сигнал, своим выходным сигналом открывает элемент 29 считывания данного канала и закрывает через элементы ИЛИ 32 по третьим запрещающим входам элементы 29 считывания остальных каналов. При подаче сигнала на шину 35 он проходит через элемент 29 считьГвания данного канала ад -есации и через формирователь 30 входных сигналов на вход формирователя 31 сигналов сброса и на вход дешифратора 33, где превращается в код адреса ячейки 28 памяти и поступает на выход устройства и на адресную шину мультиплексора 24, при этом мультиплексор подключает на шину 37 те свои информационные входы, к которым подключен выход параллельного кода счетчика 17.

Сигнал с выхода формирователя 31 сброса устанавливает в «О ячейку 28 памяти каналу 27, чем снимается запрещающий сигнал с выхода элемента 29 считывания следующего канала адресации.

При повторном превышении входным сигналом заданного уровня шифратор работает аналогичным образом.

Технико-экономический эффект, заключается в возможности преобразования в код временных параметров входных сигналов в момент их появления, чем обеспечивается непрерывность слежения за всеми входными сигналами и минимальное время реакции устройства.

Формула изобретения

1.Шифратор, содержаший адресный блок, выполненный из дешифратора и каналов адресации,, отличающийся тем, что, с целью расширения функциональных возможностей в него введены мультиплексор, входная щина «Начало преобразования, блоки фиксации времени и формирователь цикла преобразования, выход которого соединен с установочными входами блоков фиксации времени, информационные выходы которых подключены к информационной шине мультиплексора, а адресные выходы соединены с соответствующими входами каналов адресации адресного блока, входная шина «Начало преобразования соединена с входом формирователя цикла преобразования и управляющими входами блоков фиксации времени, выход адресного блока соединен с адресной шиной мультиплексора.

2.Шифратор по п. Г, отличающийся тем, что каждый блок фиксации времени содержит компаратор, дифференцирующую цепочку, формирователи импульсов, элементы И, триггеры и счетчики, выход компаратора, соединен через дифференцирующую цепочку с формирователями импульсов, выход первого из них соединен через делитель частоты с первым входом первого элемента И, выход которого соединен с первым входом первого триггера, выход первого формирователя импульсов также соединен с первым входом третьего триггера, один выход которого соединен с вторыми входами первого и второго элементов И, а другой выход соединен с первым входом третьегоэлемента И, выход второго формирователя импульсов через инвертор соединен с входом второго элемента И, выход которого соединен с первым входом второго триггера, второй вход которого соединен с вторыми входами других триггеров, с установочным входом блока фиксации времени и установочными входами счетчиков, выходы которых подключены к информационным выходам блока фиксации времени, к соответствующим адресным выходам которого подключены выход первого формирователя импульсов, выход инвертора и выход делителя частоты, выходы

первого, второго и третьего триггеров соединены соответственно с входами четвертого, пятого и третьего элементов И, выходы которых подключены к счетным входам счетчиков, вторые входы третьего, четвертого и пятого элементов И объединены между собой и подключены к управляющему входу блока фиксации времени.

3. Шифратор по п. 1, отличающийся тем, что формирователь цикла преобразования содержит элемент Pi, триггер, счетчик и генератор импульсов, выход которого соединен с первым входом элемента И, выход которого через счетчик соединен с первым входом триггера, выход которого соединен с вторым входом элемента И, выход которого подключен к выходу формирователя цикла преобразования, вход которого соединен с вторым входом триггера.

Источники информации, принятые во внимание при экспертизе 1. «Электроника, 1980, № 10, с. 62. 2. Авторское свидетельство СССР

№ 590825, кл. G II С 11/06, 24.04.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1985 |

|

SU1298802A2 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО СБОРА ДАННЫХ | 2002 |

|

RU2218596C2 |

| Устройство адресации памяти | 1989 |

|

SU1689956A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для адресной передачи сигналов тревоги в системе пожарной сигнализации | 1991 |

|

SU1836707A3 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Шифратор | 1985 |

|

SU1298801A2 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

Авторы

Даты

1982-04-15—Публикация

1980-07-23—Подача