Изобретение относится к технике накопления информации, а именно к устройствам цифровой записи-воспроизведения речевой информации, и может быть использовано на пассажирском транспорте, в частности для обеспечения пассажиров необходимой речевой информацией в вагонах метро, в вагонах электропоездов. Кроме того, оно может найти применение в качестве автоответчика в кинотеатрах, в конференцзалах, а также в качестве информатора в справочных устройствах.

Известно устройство для магнитной записи-воспроизведения речевых сигналов по а. с. N 1554013, кл. G 11 B 5/027, 1990, содержащее входную и выходную шины, дельта-кодер дельта-декодер (кодек), два элемента оперативной динамической памяти, четыре коммутатора, усилитель воспроизведения, усилитель записи, формирователь управляющих импульсов, мультиплексор, три счетчика, блок фиксации цифрового кода речи, три элемента ИЛИ, три триггера, формирователь тактовых импульсов, дифференцирующий элемент, элемент И, блок переключения режимов, формирователь тока скорости перемещения, генератор стирания и подмагничивания, датчик расхода магнитной ленты, электродвигатель с лентопротяжным механизмом (ЛПМ), универсальную и стирающую магнитные головки и магнитную ленту.

В данном устройстве речевая информация, поступающая на входную шину устройства, в режиме записи преобразуется сначала в цифровую форму, затем после соответствующей обработки (задержки) преобразуется снова в аналоговую форму. Обработанный таким образом аналоговый входной сигнал речевой информации записывается в аналоговой форме на магнитную ленту с некоторой задержкой, что позволяет повысить в дальнейшем разборчивость речи при воспроизведении речевых сигналов в режиме с реверсированием направления движения магнитной ленты. Для транспортирования магнитной ленты в устройстве используется ЛПМ, которому свойственна, как известно, некоторая инерционность при реверсировании направления движения магнитной ленты, что ухудшает разборчивость речи. Благодаря использованию оперативной динамической памяти в данном устройстве цифровой код речевой информации задерживается в процессе записи на интервал времени, превышающий время реверсирования перемещения магнитной ленты, что улучшает разборчивость речи в дальнейшем при воспроизведении.

Недостатком устройства является сам факт наличия ЛПМ, для изготовления которого необходимо большое число механических деталей, а для его функционирования необходимы соответствующие схемы (усилители записи и воспроизведения, генератор стирания и подмагничивания, датчик расхода магнитной ленты, формирователь тока скорости перемещения, электродвигатель и магнитные головки), что усложняет устройство и снижает его надежность.

Этот недостаток отсутствует в известном Автомобильном приемнике с памятью (Ж. Мицубиси дэнки гихо, N 8, 1987, с. 641-644, Япония), содержащем антенну, тракт АМ, тракт НЧ, коммутатор, аналого-цифровой преобразователь (АЦП), цифроаналоговый преобразователь (ЦАП), блок оперативной памяти, блок управления и динамическую головку.

Данное устройство, кроме приема радиовещательных станций, позволяет принимать дорожную речевую информацию и записывать ее в память устройства. В этом устройстве дорожная речевая информация, поступающая на вход устройства, преобразуется с помощью АЦП в цифровую форму и записывается в блок памяти устройства (микросхемы оперативной памяти). Хранимая в блоке памяти устройства речевая информация в процессе считывания преобразуется с помощью ЦАП из цифровой формы в аналоговую, которая является точной копией записываемого сигнала. Здесь в качестве накопителя информации используются микросхемы оперативной памяти.

Недостатком устройства является то, что запись и считывание речевой информации осуществляются последовательно по всем адресам ячеек памяти. В ячейки памяти записываются как фрагменты речевой информации, так и паузы между ними. Такой способ записи и считывания применим, если общая продолжительность речевых сообщений и пауз во времени не велика и если речевая информация в каждый текущий момент времени не содержит часто повторяющихся фрагментов речевой информации. Как известно, надежность таких устройств зависит прежде всего от количества применяемых в блоке памяти микросхем оперативной памяти. Чем больше общая продолжительность речевых сообщений и пауз во времени, тем больше при последовательной записи и считывании речевой информации требуется микросхем памяти. Увеличение числа используемых микросхем памяти приводит, кроме удорожания, к уменьшению надежности блока оперативной памяти и самого устройства в целом.

Наиболее близким к предлагаемому устройству является устройство для цифровой записи-воспроизведеия речевой информации по а. с. N 1573470, кл. G 11 B 20/00, взятое в качестве прототипа, содержащее кодек (дельта-модулятор-демодулятор), блок управления и синхронизации, основной канал записи, хранения и считывания информации, включающий в себя три блока памяти, два двоичных счетчика, реверсивный счетчик и счетный триггер, три мультиплексора, компаратор, формирователь порогового напряжения, генератор кода паузы, инвертор, элементы И, ключевые элементы, фильтр нижних частот и усилитель. В данном устройстве при записи речевого сигнала осуществляется компрессия пауз при помощи порогового контроля уровня речевого сигнала посредством компаратора. При этом информация о длительности речевых фрагментов и пауз записывается в соответствующие блоки памяти. Данное устройство производит последовательную запись и последовательное считывание речевой информации.

Недостатками прототипа являются невозможность произвольного считывания речевой информации по заданному алгоритму, что ограничивает область его применения, а также применение большого количества микросхем в блоках памяти в случаях, когда речевая информация имеет большую информационную емкость (1 Мбит и более).

Цель изобретения - произведение последовательной записи и произвольное считывание речевой информации по заданному алгоритму. Такой принцип записи и считывания речевой информации позволяет использовать минимально возможное количество микросхем памяти и значительно улучшить эксплуатационные качества устройства.

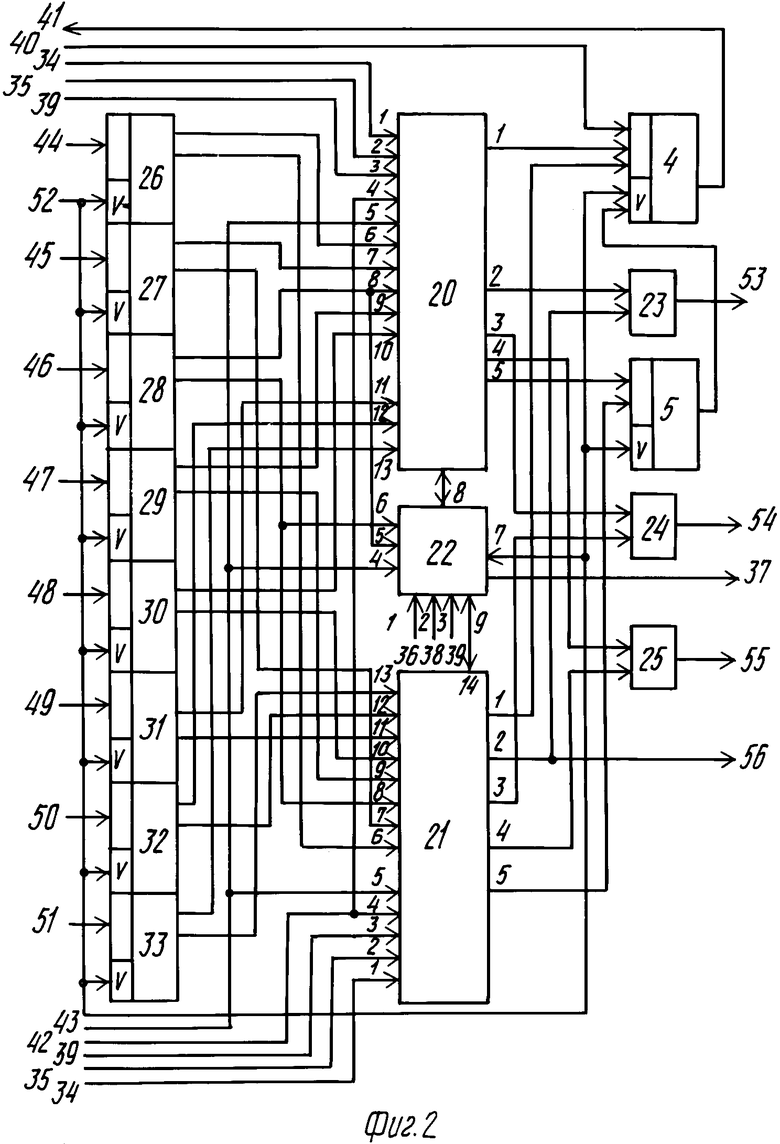

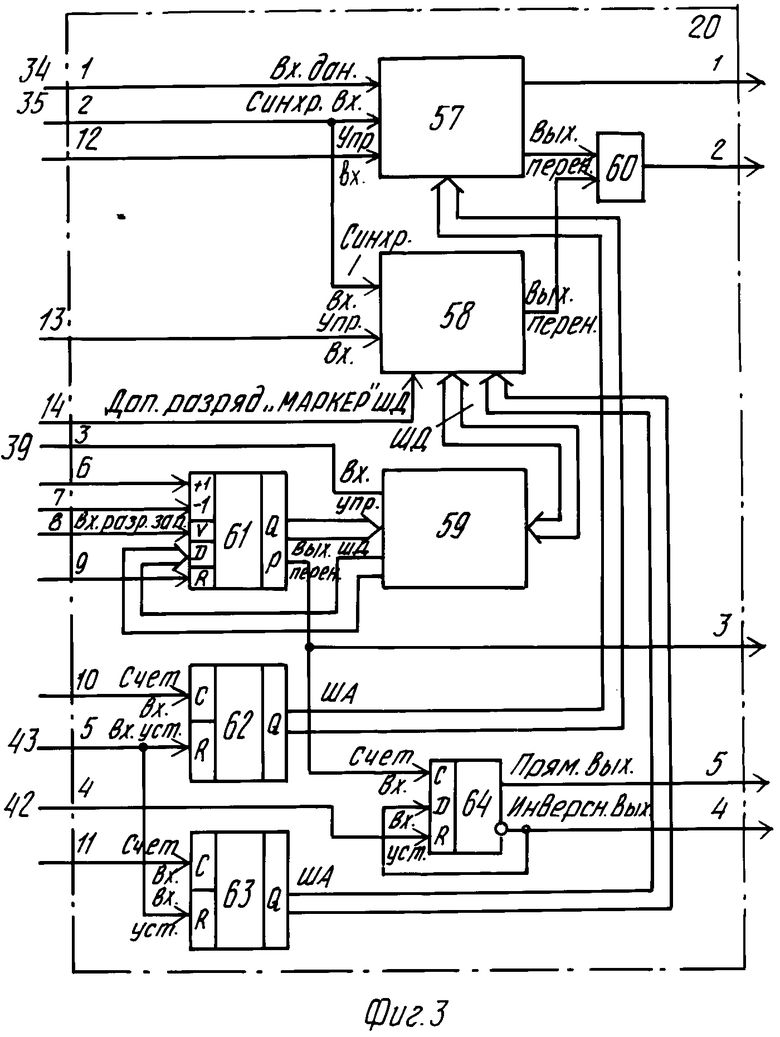

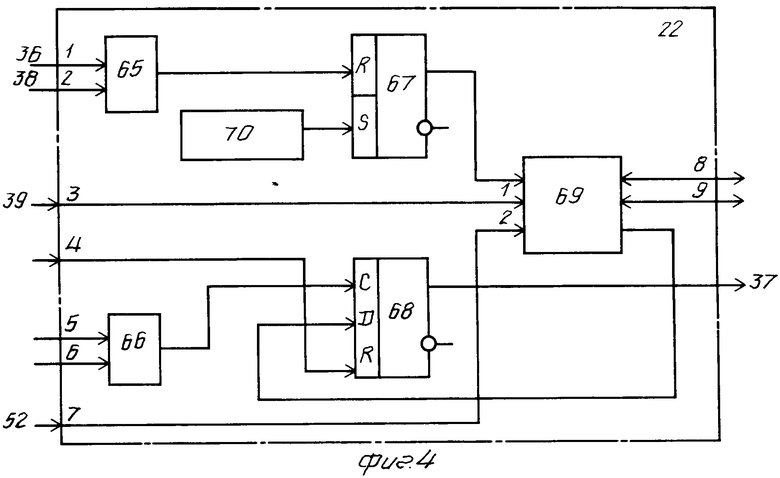

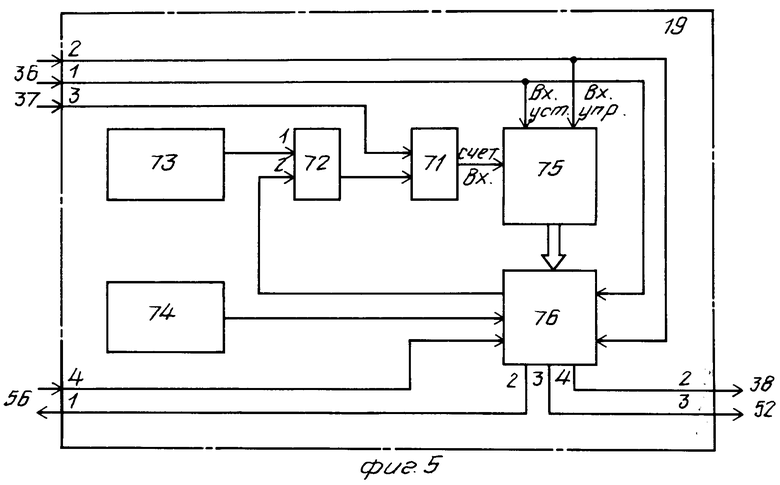

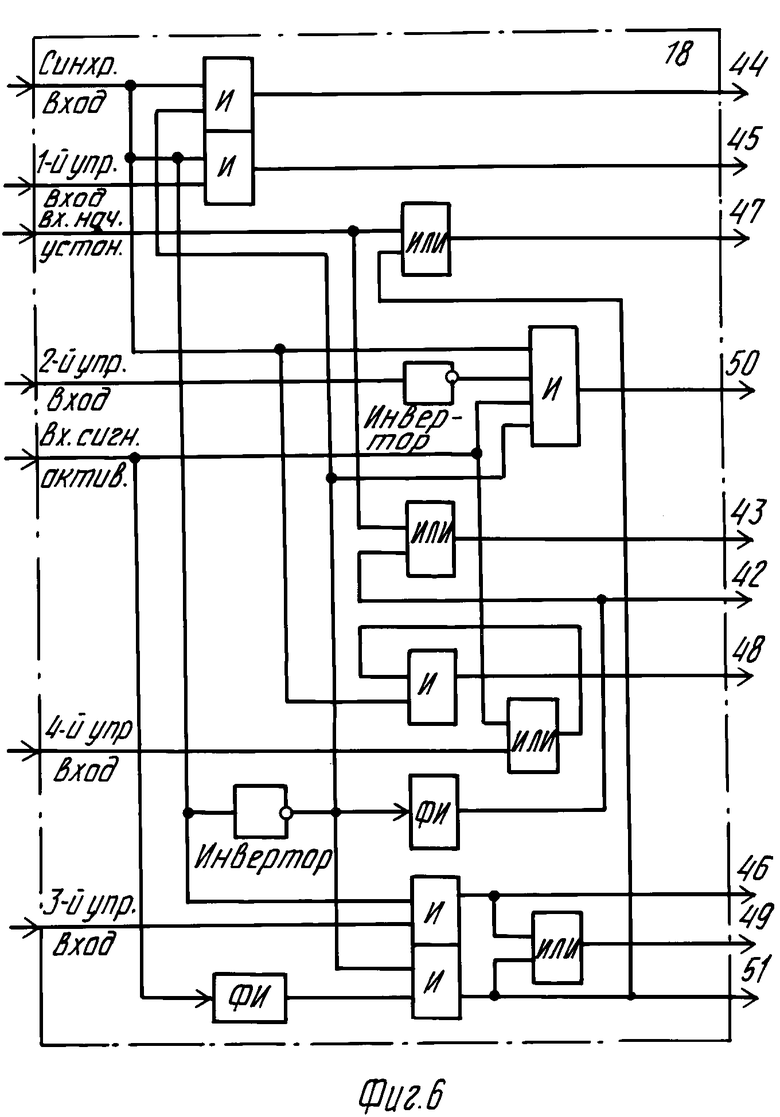

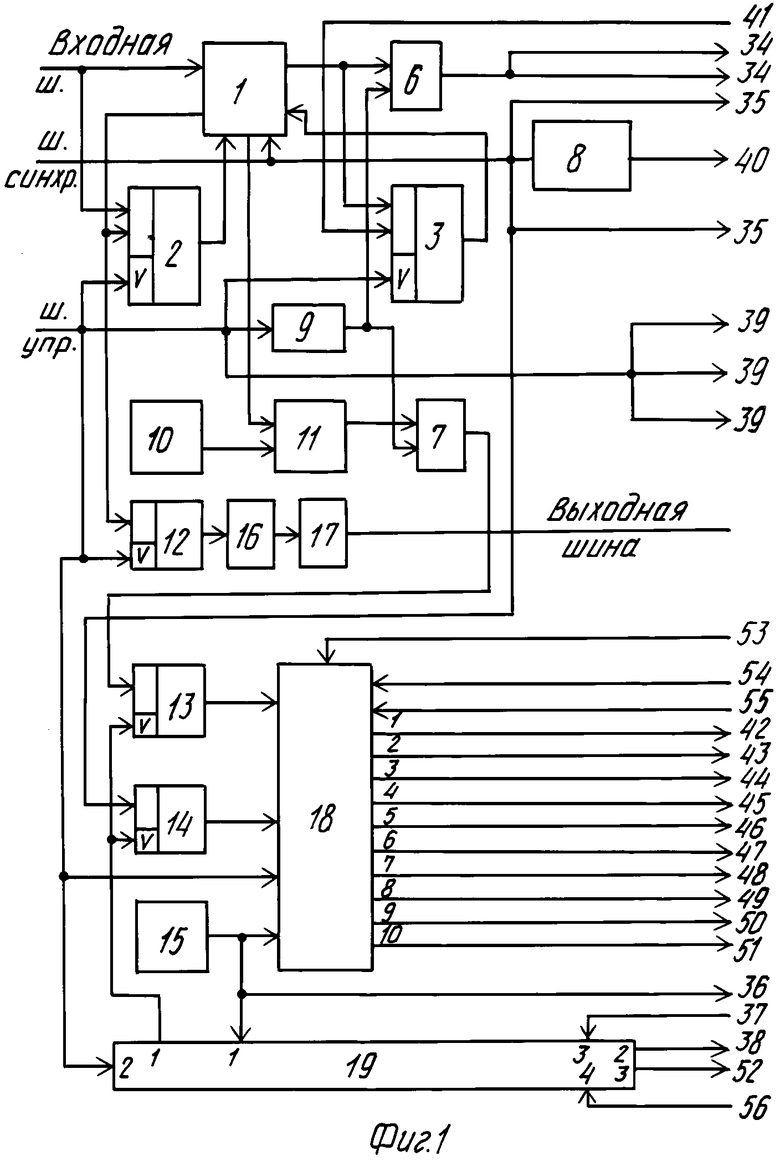

На фиг. 1, 2 изображена структурная схема предлагаемого устройства; на фиг. 3-6 - варианты выполнения отдельных блоков: фиг. 3 - основной (дополнительный) канал записи, хранения и считывания информации; на фиг. 4 - блок обработки маркера; на фиг. 5 - старт-стопный блок управления; на фиг. 6 - блок управления и синхронизации.

Устройство для цифровой записи-воспроизведения речевой информации содержит кодек 1, первый 2, второй 3, третий 4 и четвертый 5 мультиплексоры, первый 6 и второй 7 элементы И, генератор 8 кода паузы, инвертор 9, формирователь 10 порогового напряжения, компаратор 11, ключевые элементы 12-15, фильтр 16 нижних частот, усилитель 17, блок 18 управления и синхронизации, старт-стопный блок 19 управления, основной 20 и дополнительный 21 каналы записи, хранения и считывания информации, блок 22 обработки маркера, первый 23, второй 24 и третий 25 элементы ИЛИ, восемь демультиплексоров 26-33. Кодек 1 первым аналоговым входом подключен к входной шине и первому входу мультиплексора 2, выход которого подключен к второму аналоговому входу кодека 1, а второй вход - к аналоговому выходу кодека 1 и входу ключевого элемента 12, подсоединенного выходом через последовательно соединенные фильтр 16 и усилитель 17 к выходной шине. Управляющий выход кодека 1 подключен к первому входу компаратора 11, второй вход которого подключен к формирователю 10, а выход - к первому входу элемента И 7. Цифровой вход кодека 1 подключен к выходу мультиплексора 3, первый вход которого подключен к цифровому выходу кодека 1 и первому входу элемента И 6, выход которого 34 подключен к первым входам основного 20 и дополнительного 21 каналов. Синхронизирующий вход кодека 1 подключен к шине синхронизации, входу генератора 8, вторым входам 35 основного 20 и дополнительного 21 каналов и входу ключевого элемента 14, выходом подключенного к синхронизирующему входу блока 18. Вторые входы элементов И 6, 7 объединены и соединены с выходом инвертора 9. Выход элемента И 7 соединен с входом ключевого элемента 13, выходом подключенного к входу сигнала активности блока 18, вход начальной установки которого соединен с ключевым элементом 15, первым входом блока 19 и первым входом 36 блока 22. Второй вход блока 19 подключен к шине управления и управляющим входам мультиплексоров 2, 3, ключевого элемента 12 и блока 18. Третий вход 37 блока 19 соединен с выходом 37 блока 22. Первый выход блока 19 соединен с управляющими входами ключевых элементов 13, 14, второй выход 38 - с вторым входом блока 22 обработки маркера. Вход интертора 9 подключен к шине управления, третьим входам 39 основного 20, дополнительного 21 каналов блока 22. Выход генератора 8 подключен к первому входу 40 мультиплексора 4, выход 41 которого подключен к второму входу мультиплексора 3. Четвертые входы основного 20 и дополнительного 21 каналов соединены между собой и с первым управляющим выходом 42 блока 18. Пятые входы основного 20 и дополнительного 21 каналов и четвертый вход блока 22 объединены и соединены с вторым управляющим выходом 43 блока 18. Шестые - тринадцатые входы основного канала 20 соединены с первыми, а дополнительного 21 - с вторыми выходами демультиплексоров 26-33, входы 44-51 которых соединены соответственно с третьим - десятым управляющими выходами 44 - 51 блока 18. Пятый, шестой входы блока 22 соединены соответственно с восьмыми входами основного 20 и дополнительного 21 каналов, седьмой вход блока 22 соединен с управляющими входами мультиплексоров 4, 5, объединенными управляющими входами 52 демультиплексоров 36-33 и третьим выходом 52 блока 19, а восьмой, девятый входы/выходы блока 22 - с дополнительными (четырнадцатыми) входами/выходами "Маркер" каналов 20, 21. Первые выходы каналов 20, 21 соединены соответственно с вторым и третьим входами мультиплексора 4, вторые, третьи, и четвертые выходы каналов 20, 21 соединены соответственно с входами элементов ИЛИ 23-25, выходы которых 53-55 соединены соответственно с вторым, третьим и четвертым управляющими входами блока 18. Второй выход 56 канала 21 соединен также с четвертым входом блока 19. Пятые выходы каналов 20, 21 подключены к соответствующим входам мультиплексора 5, выход которого соединен с вторым управляющим входом мультиплексора 4. Каналы 20 и 21 по своему исполнению идентичны и аналогичны каналу записи, хранения и считывания информации, описанному в а. с. N 1573470, кл. G 11 B 20/00 и сформированному из блоков памяти 10, 15, счетного триггера 13, элемента ИЛИ 18, счетчиков 23-25 и блока 40, который по своей сути является не блоком памяти, а шинным формирователем. Для более ясного описания работы всего устройства раскрываются состав и структура варианта исполнения канала 20 (фиг. 3). Он содержит два блока 57, 58 памяти и шинный формирователь 59, элемент ИЛИ 60, три счетчика 61-63 и счетный триггер 64. Вход данных, синхронизирующий и управляющий входы первого блока 57 памяти являются соответственно первым, вторым и двенадцатым входами канала 20, первый выход блока 57 памяти является первым выходом канала 20. Адресный вход блока 57 соединен с выходом счетчика 62. Синхронизирующий вход блока 57 соединен с синхронизирующим входом второго блока 58 памяти, управляющий вход которого является тринадцатым входом канала 20. Выходы переполнения блоков 57, 58 памяти соединены с входами элемента ИЛИ 60, выход которого является вторым выходом канала 20. Адресный вход блока 58 соединен шиной с выходом счетчика 63, шиной данных блок 58 соединен с шинным формирователем 59, управляющий вход которого является третьим входом канала 20, а вход/выход "Маркер" старшего дополнительного разряда шины данных блока 58 является дополнительным (четырнадцатым) входом/выходом "Маркер" канала 20. Суммирующий, вычитающий входы, вход разрешения записи и установочный вход счетчика 61 являются соответственно шестым, седьмым, восьмым и девятым входами канала 20. Вход данных счетчика 61 соединен с шинным формирователем 59, выход счетчика 61 соединен с шиной с входом шинного формирователя 59, а выход переноса счетчика 61 - со счетным входом счетного триггера 64 является третьим выходом канала 20. Счетный и установочный входы счетчика 62 являются соответственно десятым и пятым входами канала 20, причем установочный вход счетчика 62 соединен с установочным входом счетчика 63, счетный вход которого является одиннадцатым входом канала 20. Установочный вход счетчика триггера 64 является четвертым входом канала 20, а инверсный и прямой входы триггера 64 являются соответственно четвертым и пятым выходами канала 20, причем инверсный выход и вход D счетного триггера 64 соединены между собой.

Блок 22 обработки маркера является новым, изображен на фиг. 4 и содержит два элемента ИЛИ 65, 66, RS-триггер, D-триггер 68, коммутатор 69 и кнопку "Маркер" 70. Входы элемента ИЛИ 65 являются соответственно первым 36 и вторым 38 входами блока 22, выход элемента ИЛИ 65 подключен к R-входу триггера 67, S-вход которого подключен через кнопку "Маркер" 70 к шине питания, а прямой выход - к маркерному входу коммутатора 69. Два управляющих входа коммутатора являются третьим 39 и седьмым 52 входами блока 22, а два его входа/выхода являются восьмым, девятым входами/выходами блока 22. Выход данных коммутатора 69 соединен с D-входом триггера 68, выход которого является выходом блока 22. Установочный вход триггера 68 является четвертым входом блока 22, а его счетный вход подключен к выходу элемента ИЛИ 66, входы которого являются соответственно пятым и шестым входами блока 22.

Старт-стопный блок 19 управления также является новым, изображен на фиг. 5 и содержит два элемента ИЛИ 71, 72, кнопки "Информация" 73 и "Пуск" 74, счетчик-распределитель команд 75 и шифратор команд 76. Установочный и управляющий входы счетчика 75 соединены соответственно с установочным и управляющим входами шифратора 76 и являются соответственно первым и вторым входами блока 19. Счетный вход счетчика 75 подключен к выходу элемента ИЛИ 71, первый вход которого является третьим входом блока 19, а второй вход соединен с выходом элемента ИЛИ 72, подключенного первым входом через кнопку "Информация" 73 к общей шине устройства, а вторым входом - к первому управляющему выходу шифратора 76. Вход запуска записи шифратора 76 подключен через кнопку "Пуск" 74 к шине питания устройства, четвертый вход является четвертым входом блока 19, а второй, третий, четвертый управляющие выходы шифратора 76 являются соответственно первым, третьим, вторым выходами блока 19.

Один из возможных вариантов блока 18 синхронизации и управления по своему исполнению аналогичен выполненному в устройстве по а. с. N 1573470, кл. G 11 B 20/00 и сформирован из четырех элементов ИЛИ 19-22, двух инверторов 29, 30, шести элементов И 32-37 и двух формирователей 38, 39 испульсов. Внутренние связи между элементами аналогичны известному устройству. Поскольку блок 18 может быть выполнен и иным образом, а в описании участвуют соответствующие входные сигналы блока, составляющие его элементы не нумеруются.

Устройство работает следующим образом.

Для записи или другой информации в устройство совместно с подачей напряжения питания по шине синхронизации поступает тактовая частота. На шину управления режимом работы устройства "Запись/чтение" подключается сигнал логического "0". При этом происходят соответствующие коммутации и переключения в устройстве, при которых к входной шине подключается кодек 1, выход которого подключен к входам блока памяти 57 основного 20 и дополнительного 21 каналов записи, хранения и считывания информации.

Таким образом, устройство готово к восприятию аналоговой информации, преобразованию ее в цифровую дельта-форму и запичи ее в блоки 57 памяти основного 20 и дополнительного 21 каналов. Однако запись информации начинается после нажатия кнопки "Пуск" 74 при поступлении информации в аналоговом виде, если уровень информационного сигнала превышает некоторый порог, величина которого формируется формирователем 10 порогового напряжения. При этом информационная импульсная последовательность речевого сигнала записывается сначала в блок 57 памяти дополнительного канала 21, после переполнения которого запись автоматически продолжается в блок 57 памяти основного канала 20, а информация о длительности импульсной последовательности записывается сначала во второй блок 58 памяти дополнительного канала 21, после переполнения которого запись автоматически продолжается во второй блок 58 памяти основного канала 20. Паузы между фрагментами речевого сигнала исключаются из записи в блоки 57 памяти обоих каналов 20, 21, если их длительность превышает длительность межслоговой паузы. Последовательно в блоки 58 памяти обоих каналов 20, 21 за записью информации о длительности фрагмента речевого сигнала записывается информация о длительности паузы, затем снова величина длительности очередного речевого фрагмента и т. д. Таким образом, в блоки 57 памяти обоих каналов 20, 21 записываются информационные фрагменты речевого сигнала в дельта-форме, а в блоки 58 памяти обоих каналов - последовательно чередующаяся информация о длительности фрагментов речевого сигнала и пауз в двоичном виде. При переполнении памяти основного канала 20 запись информации прекращается.

Устройство при записи позволяет записываемую речевую информацию разбивать на отдельные блоки информации, состоящие из одного или более следующих друг за другом речевых фрагментов. Это осуществляется путем нажатия кнопки "Маркер" 70 в момент наличия паузы, следующей после последнего фрагмента текущего блока информации. В этом случае во вторые блоки 58 памяти обоих каналов 20, 21 одновременно с записью информации о длительности паузы, в момент наличия которой была нажата кнопка "Маркер" 70, записывается информация о длительности блока информации (логическая "1"), в противном случае записывается логический "0".

При считывании информации по шине управления режимом работы устройства "Запись/чтение" поступает сигнал логической "1". В схеме устройства происходят соответствующие коммутации и переключения, при которых к аналоговому выходу кодека 1 подключается тракт воспроизведения нижних частот (ключевой элемент 12, фильтр 16 и усилитель 17).

Через мультиплексоры 4, 3 поочередно поступают информационные фрагменты речевого сигнала в виде информационной импульсной последовательности в дельта-форме и генерируемая последовательность . . . 1010. . . чередующихся "1" и "0" соответствующей длительности, записанной в блоке 58 памяти одного из каналов 20, 21. Мультиплексор 4 цифровоо сигнала управляется от счетных триггеров 64 обоих каналов 20, 21, считывающих информацию о длительности речевых фрагментов и пауз последовательно, в соответствии с двоичными кодами, считываемыми из блоков 58 памяти. Таким образом, при считывании речевой сигнал восстанавливается в его первоначальной форме.

В режиме записи информации на шине управления устройства устанавливается сигнал логического "0". Этот сигнал поступает на вход управления мультиплексора 2, который подключает при этом аналоговый выход кодека 1 к второму аналоговому входу кодека 1, тем самым замыкая цепь обратной связи кодека 1. Тот же сигнал, поступая на вход управления мультиплексора 3 цифровых сигналов, переключает его в положение, при котором цифровой выход кодека 1 подключается к своему цифровому входу. Кроме того, логический "0" с шины управления "Запись/чтение", поступая на вход управления ключевого элемента 12, переводит его в выключенное состояние. Инвертированный инвертором 9 в логическую "1" сигнал "Запись/чтение", поступая на вход элемента И 6, разрешает прохождение цифровой информации с цифрового выхода кодека 1 на входы данных блоков 57 памяти обоих каналов 20, 21. Тот же сигнал логической "1", поступая на вход элемента И 7, разрешает восприятие ключевым элементом 13 импульсов сигнала активности, вырабатываемого компаратором 11. Сигнал "Запись/чтение" уровня логического "0" поступает также на первый управляющий вход блока 18 управления и синхронизации и переводит его в режим управления записью информации. Кроме того, сигнал "Запись/чтение" уровня логического "0" поступает через третьи входы 39 обоих каналов 20, 21 к управляющим входам шинных формирователей 59, включая их в прямом направлении на трансляцию выходных сигналов разрядов реверсивных счетчиков 61 на шину данных блоков 58 памяти. Этот же сигнал через третий вход 39 блока 22 обработки маркера поступает на первый управляющий вход коммутатора 69, включая его в прямом направлении на трансляцию выходного сигнала маркера с прямого выхода RS-триггера 67 на один из дополнительных разрядов "Маркер" шин данных блоков 58 памяти каналов 20, 21 в зависимости от уровня сигнала, подаваемого на второй управляющий вход 52 коммутатора 69 через седьмой вход 52 блока 22. Сигнал с шины управления уровня логического "0" поступает на второй (управляющий) вход старт-стопного блока 19 управления, переводя его в режим управления записью информации. Таким образом, устройство готово к записи в дельта-форме рачевой или другой информации.

Речевой аналоговый сигнал с входной шины поступает на первый аналоговый вход кодека 1, где сравнивается с восстановленным значением аналогового сигнала преды- дущего такта, поступающего с аналогового выхода кодека 1 через мультиплексор 2 на второй аналоговый вход и получаемого из цифрового сигнала речевой информации, поступающего с цифрового выхода кодека 1 через мультиплексор 3 на цифровой вход кодека 1. Если входной аналоговый сигнал с каждым тактом больше восстановленного аналогового сигнала, то на цифровом выходе кодека 1 с тактовой частотой формируется информационная импульсная последовательность входного аналогового сигнала (логическая "1"), в противном случае - логический "0". При отсутствии речевого сигнала на входе кодека 1 ("молчание") цифровая последовательность на цифровом выходе кодека имеет вид . . . 1010. . .

При аналого-цифровом преобразовании в дельта-форму дельта-демодулятор кодека 1 осуществляет цифровую компрессию, управляет величиной шага квантования в зависимости от уровня входного аналогового сигнала. В кодеке 1 осуществляется следующая зависимость: чем больше растет уровень входного аналогового сигнала, тем больше шаг квантования, сильнее компрессия и экспандирование при цифроаналоговом преобразовании, причем закон компрессии при дельта-модуляции полностью соответствует закону экспандирования при дельта-демодуляции.

Кроме того, кодек 1 осуществляет определение границ рачевого фрагмента или паузы. Анализ речевого фрагмента сводится к определению двух ситуаций: перехода от паузы к речевому фрагменту и перехода от речевого фрагмента к паузе. В первом случае до появления аналогового сигнала фрагмента речи на входе кодека 1 последний вырабатывает последовательность чередующихся нулей и единиц . . . 1010. . . , соответствующую нулевому сигналу. На управляющем выходе кодека 1 уровень сигнала равен нулю. При появлении сигнала фрагмента речи кодек 1 начинает вырабатывать однородные символы "1" или "0" в соответствии с изменением уровня фрагмента сигнала. На цифровом выходе кодека 1 имеется цифровая последовательность, содержащая пачки однородных посылок. Следовательно, при появлении после паузы информационного фрагмента на управляющем выходе кодека 1 появляется сигнал, величина которого пропорциональна изменению уровня входного сигнала. Сигнал с управляющего выхода кодека 1 поступает на первый вход компаратора 11, где сравнивается с пороговым сигналом, поступающим на второй вход компаратора 11 с выхода формирователя 10 порогового напряжения.

При переходе от речевого фрагмента к паузе кодек 1 из-за уменьшения уровня сигнала вырабатывает цифровую последовательность, содержащую с каждым разом все меньшее число пачек однородных посылок, и с началом паузы цифровая последовательность принимает вид . . . 1010. . . , а следовательно, при отсутствии пачек однородных посылок сигнал на упавляющем выходе кодека 1 уменьшается до нулевого значения. Из этого следует, что порог компаратора 11 необходимо выбирать таким образом, чтобы он был больше сигнала на управляющем выходе кодека 1 при переходе от речевого фрагмента к паузе и меньше сигнала на управляющем выходе кодека 1 при переходе от паузы к речевому фрагменту.

Компаратор 11 сравнивает сигнал уровня, поступающий с управляющего выхода кодека 1. С выхода компаратора 11 сигнал поступает на вход ключевого элемента 13. Находятся в исходном состоянии счетчики 62, 63 формирования адресов записи, счетный триггер 64 основного 20 и дополнительного 21 каналов, а также RS-триггер 67 и D-триггер 68 блока 22 обработки маркера. Процесс записи начинается сразу же после нажатия кнопки 74 "Пуск". На соответствующий вход шифратора команд 76 старт-стопного блока управления 19 поступает сигнал логической "1". С второго управляющего выхода шифратора 76 через первый выход блока 19 на управляющие входы ключевых элементов 13 и 14, а с третьего управляющего выхода шифратора 76 через третий выход 52 блока 19 и управляющие входы 52 демультиплексоров 26-33, мультиплексоров 4, 5, коммутатора 69 блока обработки маркера 22 поступает управляющий сигнал с уровнем логической "1". В результате этого на синхронизирующий вход блока управления и синхронизации 18 начинают поступать тактирующие импульсы с шины синхронизации, а вход сигнала активности блока 18 подключается к выходу элемента И 7. Демультиплексоры 26-33, мультиплексоры 4, 5 обеспечивают подключение входов и выходов дополнительного канала 21 к соответствующим входам и выходам блоков и элементов устройства и блокировку аналогичных входов и выходов основного канала 20. Таким образом, запись речевой информации сначала осуществляется в блоки 57, 58 памяти дополнительного канала 21. При поступлении первого речевого фрагмента в устройство на вход сигнала активности блока 18 управления и синхронизации появляется сигнал активности с уровнем логической "1". На счетный вход счетчика 62 через десятый вход дополнительного канала 21 с выхода 48 блока 18 через демультиплексор 30 начинают поступать импульсы тактовой частоты. На выходах счетчика 62 с тактовой частотой формируются адреса записи речевой информации в блок 57 памяти. При наличии сигналов с уровнем логического "0" на первых двух управляющих входах блока 18 с управляющего выхода 50 блока 18 через демультиплексор 32 на управляющий вход блока 57 памяти через двенадцатый вход дополнительного канала 21 также поступают импульсы тактовой частоты, являющиеся сигналом стробирования записи информации. Блок 18 по переходному фронту сигнала активности (перепад напряжения от логического "0" к логической "1") формирует на выходах 47, 49 и 51 короткие импульсы с уровнем логической "1". Импульс, поступая с выхода 51 через демультиплексор 33 на управляющий вход блока 58 через тринадцатый вход дополнительного канала 21, является сигналом стробирования записи информации о длительности предшествующей речевому фрагменту паузы в блок 58 памяти. Импульс, поступая с выхода 47 блока 18 через демультиплексор 29 на установочный вход реверсивного счетчика 61 через девятый вход дополнительного канала 21, переводит его в исходное состояние. Импульс, поступая с выхода 49 блока 18 через демультиплексор 31 на счетный вход счетчика 63 через одиннадцатый вход дополнительного канала 21, формирует на выходах последнего сигнал адреса, по которому в блоке 58 памяти записывается информация о длительности поступившего речевого фрагмента. При этом сигнал тактовой частоты поступает с выхода 44 блока 18 через демультиплексор 26 на суммирующий вход реверсивного счетчика 61 через шестой вход дополнительного канала 21, который на основе этого сигнала формирует информацию о длительности поступившего речевого фрагмента. Эта информация с выходов разрядов реверсивного счетчика 61 поступает через шинный формирователь 59 на блок 58 памяти. Информация о длительности поступившего речевого фрагмента записывается в блок 58 памяти по заднему фронту сигнала активности, поступающему на вход сигнала активности блока 18. При этом блок 18 управления и синхронизации формирует импульс, поступающий с выхода 51 блока 18 и стробирующий запись информации в блоке 58 памяти дополнительного канала 21 по адресу, сформированному на выходе счетчика 63. Тот же импульс, поступая с выхода 47 блока 18 на вход установки реверсивного счетчика 61 через девятый вход канала 21, переводит его в исходное состояние, тем самым обеспечивая начало формирования длительности поступающей паузы. Кроме того, импульс с выхода 49 поступает на счетный вход счетчика 63, который при этом формирует сигнал адреса, по которому в блоке 58 памяти записывается информация о длительности наступающей паузы. Таким образом, в режиме записи информации блок 18 управления и синхронизации как по переднему, так и по заднему фронтам сигнала активности речевого фрагмента на соответствующих выходах формирует импульсы, которые, поступая на соответствующие входы дополнительного 21, а в дальнейшем и на аналогиные по значению входы основного канала 20, стробируют запись информации о длительности речевого фрагмента или паузы.

В паузах при записи информации сигнал активности на входе сигнала активности блока 18 управления и синхронизации соответствует логическому "0". Поэтому блоком 18 отключается сигнал стробирования записи информационной импульсной последовательности в блоки 57 памяти каналов 20, 21. Блок 18 отключает также подачу сигнала тактовой частоты на счетные входы счетчика 62 каналов 20, 21, тем самым прекращается выработка сигналов адресов записи в блоки 57 памяти обоих каналов.

Окончание записи в память дополнительного канала 21 поступает при переполнении блока 57 памяти. При этом на вход 56 шифратора 76 команд старт-стопного блока 19 управления поступает сигнал логической "1", в результате чего третий управляющий выход шифратора 76 и соответственно третий выход 52 блока 19 меняет свое состояние. На управляющих входах 52 демультиплексоров 26-33, мультиплексоров 4, 5, коммутатора 69 блока 22 обработки маркера устанавливается сигнал с уровнем логического "0". В результате этого обеспечивается подключение входов и выходов основного канала 20 к соответствующим входам и выходам блоков и элементов устройства и блокировка аналогичных входов и выходов дополнительного канала 21. Таким образом, запись речевой информации продолжается в блоки 57 и 58 памяти основного канала 20, которая осуществляется аналогично записи речевой информации в блоки 57 и 58 памяти дополнительного канала 21, изложенной выше.

Окончание записи, как правило, наступает, когда переполняется блок 57 памяти основного канала 20, так как объем записываемой информации в блок 58 памяти основного канала 20 невелик. При этом на второй управляющий вход 53 блока 18 управления и синхронизации поступает сигнал логической "1". Блок 18 отключает сигнал стробирования записи информации в блок 57 памяти основного канала 20.

Для разбивки записываемой информации на блоки информации производят маркирование пауз, следующих вслед за последним фрагментом речевой информации блока. Для этого в момент наличия паузы между последним фрагментом текущего блока информации и первым фрагментом следующего очередного блока информации нажимают кнопку 70 "Маркер" блока 22 обработки маркера. На вход триггера 67 поступает сигнал логической "1", который устанавливает прямой выход триггера 67 в состояние логической "1". Сигнал маркера через коммутатор 69 в зависимости от состояния седьмого (управляющего) входа 52 блока 22 проходит на дополнительный вход/выход "маркер" соответствующего канала 20, 21. В момент записи информации о длительности паузы, во время которой была нажата кнопка 70 "Маркер", в один из блоков 58 памяти соответствующего канала 20, 21 осуществляется запись содержимого дополнительного разряда "Маркер" шины данных блока 58 памяти. Содержимое данного разряда в процессе считывания в дальнейшем является одним из управляющих сигналов для старт-стопного блока 19 управления. Каждый раз по переднему фронту сигнала активности, поступающего через второй вход 38 блока 22 на вход элемента ИЛИ 65, осуществляется установка в исходное состояние триггера 67 блока 22 обработки маркера.

Таким образом, в процессе записи в блоки 57 памяти обоих каналов 20, 21 записываются фрагменты блоков речевой информации, в блоки 58 памяти обоих каналов 20, 21 - информация о длительности пауз и речевых фрагментов, а также дополнительная информация об окончании блоков речевой информации. В режиме считывания информации на шине управления устанавливается сигнал логической "1". Этот сигнал поступает на первый управляющий вход старт-стопного блока 19 управления, переводя его в режим управления считыванием речевой информации. Сигнал "Запись/чтение" уровнем логической "1" поступает также на управляющие входы 39 шинных формирователей 59 через третьи входы 39 обоих каналов 20 и 21, включая формирователи 59 в обратное направление на трансляцию выходных сигналов разрядов шины данных блоков 58 памяти на входы данных реверсивных счетчиков 61. Этот же сигнал поступает на первый управляющий вход коммутатора 69 через третий вход 39 блока 22 обработки маркера. Коммутатор 69 в зависимости от состояния второго управляющего входа 52 переключается на трансляцию дополнительного разряда "Маркер" шины данных соответствующего шинного формирователя 59 одного из каналов 20 или 21 на вход триггера 68 блока 22. С третьего выхода 52 старт-стопного блока 19 управления на управляющие входы 52 демультиплексоров 26-33, мультиплексоров 4, 5, коммутатора 69 блока 22 обработки маркера поступает управляющий сигнал с уровнем логической "1", в результате чего активизируются входы и выходы дополнительного канала 21, а входы и выходы основного канала 20 блокируются. С первого выхода блока 19 на управляющие входы ключевых элементов 13 и 14 поступает сигнал запрета с уровнем логического "0", замыкая тем самым вход сигнала активности и синхронизирующий вход блока 19 управления и синхронизации на общую шину устройства. На вход элемента ИЛИ 72 блока 19 с первого управляющего выхода шифратора 76 поступает сигнал разрешения с уровнем логического "0". Таким образом, устройство находится в исходном состоянии в режиме ожинания нажатия кнопки 73 "Информация". Процесс считывания начинается после ее нажатия. На счетный вход счетчика-распределителя 75 через элементы ИЛИ 71 и 72 поступает импульс. На втором разряде параллельного выхода счетчика-распределителя 75 появляется сигнал логической "1", шифратор 76 формирует команду считывания речевой информации из блоков 57, 58 памяти дополнительного канала 21, выдавая на управляющие входы ключевых элементов 13, 14 сигнал разрешения с уровнем логической "1". На синхронизирующий вход блока 18 начинают поступать импульсы тактовой частоты, которые появляются на выходе 45 блока 18 и через демультиплексор 27 поступают на вычитающий вход реверсивного счетчика 61 дополнительного канала 21. Блок 18 обеспечивает передачу сигнала с выхода переноса реверсивного счетчика 61 дополнительного канала 21 через элемент ИЛИ 24, третий управляющий вход 54 блока 18, выход 49 блока 18 и далее через демультиплексор 31 - на счетный вход счетчика 63 дополнительного канала 21. В соответствии с адресом, сформированным счетчиком 63, на информационные входы реверсивного счетчика 61 через шинный формирователь 59 поступает информация из шины данных о длительности речевого фрагмента или паузы, причем последовательность записи - пауза, фрагмент обеспечивается последовательностью формирования адреса счетчиком 63. Каждый раз при пересчете длительности паузы или речевого фрагмента на выходе сигнала переноса реверсивного счетчика 61 появляется ипульс, который поступает через элемент 24 на третий управляющий вход 54 блока 18 и формирует на восьмом выходе 49 импульс, который через демультиплексор 31 поступает на счетный вход счетчика 63, обеспечивающего формирование следующего адреса. Кроме того, сигнал переноса, поступая на вход счетного триггера 64, меняет состояние сигналов на его выходах. Причем речевому фрагменту соответствует сигнал логического "0" на прямом выходе счетного триггера 64 и соответственно логической "1" - на инверсном выходе. При паузе сигналы на выходах счетного триггера 64 обратные. Тем самым сигналом логической "1" при речевом фрагменте, поступающим с интерсного выхода триггера 64 через элемент ИЛИ 25 на четвертый управляющий вход 55 блока управления и синхронизации 18, обеспечивается подключение сигнала тактовой частоты к счетному входу счетчика 62 через десятый вход канала 21. Сигнал тактовой частоты поступает с выхода 48 блока 18 через демультиплексор 30. Счетчик 62 при этом формирует сигнал адреса для считывания информации из блока 57 памяти. Сигнал с прямого выхода счетного триггера 64 через пятый выход канала 21 поступает на второй вход мультиплексора 5 и далее на второй управляющий вход мультиплексора 4. При считывании речевых фрагментов (сигнал на втором управляющем входе мультиплесора 4 - логический "0") сигнал с первого выхода блока 57 памяти передается через мультиплексоры 4 и 3 на цифровой вход кодека 1. Сигнал с выхода переноса реверсивного счетчика 61 через элемент ИЛИ 24 поступает на третий управляющий вход 54 блока 18 управления и синхронизации. Последний передает этот сигнал на свой управляющий выход 46. Сигнал переноса с выхода 46 блока 18 через демультиплексор 28 поступает на вход разрешения записи реверсивного счетчика 61, а также через второй вход элемента ИЛИ 66 блока 22 обработки маркера - на счетный вход триггера 68. В результате в триггер 68 осуществляется запись содержимого разряда "Маркер" шины данных блока 58 памяти, поступившего через коммутатор 69 блока 22 обработки маркера на D-вход триггера 68. Если прямой выход 37 триггера 68 имеет сигнал логического "0", то считывание информации из блоков 57, 58 памяти дополнительного канала 21 продолжается. Если прямой выход 37 триггера 68 имеет значение логической "1", то этот сигнал через элемент ИЛИ 71 блока 19 поступит на счетный вход счетчика-распределителя команд 75. На выходе третьего разряда счетчика 75 установится логическая "1", в результате чего шифратор 76 вырабатывает новую команду, разрешая считывание речевой информации из блоков 57 и 58 памяти основного канала 20, блокируя входы и выходы дополнительного канала 21, при этом контроль за состоянием разряда "Маркер" основного канала 20 осуществляется аналогично контролю дополнительного канала 21. При поступлении на третий вход 37 блока 19 очередного сигнала "Маркер" с уровнем логической "1" счетчик-распределитель 75 меняет свое состояние. Сигнал логической "1" теперь устанавливается на выходе четвертого разряда счетчика 75. Шифратор 76 выдает команду "Стоп". При этом второй и третий управляющие выходы шифратора 76, а соответственно первый и третий выходы блока 19, меняют свое состояние, запрещая поступление сигнала тактовой частоты на синхронизирующий вход блока 18 и переключая входы, выходы каналов 20, 21. Входы и выходы основного канала 20 блокируются, а входы и выходы дополнительного канала 21 активизируются. Дальнейшее считывание информации из блоков 57 и 58 канала 21 продолжается после нажатия кнопки 73 "Информация" и все в дальнейшем повторяется: считывание из памяти основного канала, стоп, считывание из памяти дополнительного канала и т. д. согласно алгоритму считывания речевой информации.

Таким образом, устройство позволяет, кроме последовательной записи речевой информации в цифровой форме в память, ее длительного хранения и последовательного считывания ее в аналоговой форме, производить и произвольное считывание речевой информации по заданному алгоритму с маркированием блоков речевой информации, что повышает эксплуатационные качества устройства и ведет к его более широкому использованию. (56) Авторское свидетельство СССР N 1573470, кл. G 11 B 20/00, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для цифровой записи-воспроизведения речевых сообщений | 1985 |

|

SU1312641A1 |

| Устройство для магнитной записи-воспроизведения речевых сигналов | 1990 |

|

SU1739384A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для цифровой записи-считывания речевых сигналов | 1984 |

|

SU1210132A1 |

| Матричный процессор | 1985 |

|

SU1354204A1 |

Использование: изобретение относится к технике цифровой записи-воспроизведения речевой информации. Сущность изобретения: с целью повышения эксплуатационных качеств за счет увеличения числа выполняемых функций, устройство содержит кодек, основной и дополнительный каналы записи, хранения и считывания информации, блок управления и синхронизации, старт-стопный блок управления, блок обработки маркера, а также четыре мультиплексора, два элемента И, генератор кода паузы, инвертор, формирователь порогового напряжения, компаратор, четыре ключевых элемента, фильтр нижних частот и усилитель, три элемента ИЛИ и восемь демультиплексоров. В основной канал записывается переменная информация, а в дополнительный - часто повторяющаяся и обеспечен раздельный доступ к блокам памяти обоих каналов, то есть устройство обеспечивает последовательную запись и, кроме последовательного, произвольное считывание речевой информации по заданному алгоритму. 6 ил.

УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ, содержащее кодек, три мультиплексора, два элемента И, генератор кода паузы, инвертор, формирователь порогового напряжения, компаратор, два ключевых элемента, фильтр нижних частот, усилитель, блок управления и синхронизации, основной канал записи, хранения и считывания информации, и шины - входную, выходную, синхронизации и управления, причем кодек подключен первым аналоговым входом к входной шине и первому входу первого мультиплексора, вторым аналоговым входом - к выходу первого мультиплексора, аналоговым выходом - к второму входу первого мультиплексора и входу первого ключевого элемента, выходом подключенного через последовательно соединенные фильтр и усилитель к выходной шине, а управляющим входом - к шине управления, управляющему входу первого мультиплексора и первому управляющему входу блока управления и синхронизации, цифровым выходом кодек подключен к первому входу второго мультиплексора и через первый элемент И к первому входу основного канала, цифровым входом - к выходу второго мультиплексора, синхронизирующим входом - к шине синхронизации, второму входу основного канала и через генератор к первому входу третьего мультиплексора, выходом подключенного к второму входу второго мультиплексора, а управляющим выходом кодек подключен к первому входу компаратора, второй вход которого соединен с выходом формирователя, а выход - с первым входом второго элемента И, второй вход которого подключен к второму входу первого элемента И и выходу инвертора, вход которого соединен с шиной управления, управляющим входом второго мультиплексора и третьим входом основного канала, первый выход которого подключен к второму входу третьего мультиплексора, а четверный и пятый входы - соответственно к первому и второму управляющим выходам блока управления и синхронизации, вход начальной установки которого подключен к выходу второго ключевого элемента, отличающееся тем, что в него введены дополнительный канал записи, хранения и считывания информации, блок обработки маркера, червертый мультиплексор, три элемента ИЛИ, третий и четвертый ключевые элементы, стартстопный блок управления и восемь демультиплексоров, входы которых соответственно соединены с третьим - десятым управляющими выходами блока управления и синхронизации, второй, третий и четвертый управляющие входы которого соединен соответственно с выходами элементов ИЛИ, вход сигнала активности - с выходом третьего ключевого элемента, входом подключенного к выходу второго элемента И, синхронизирующий вход - с выходом четвертого ключевого элемента, а вход начальной установки - с первыми входами блока обработки маркера и старт-стопного блока управления, второй вход которого соединен с первым управляющим входом блока управления и синхронизации, третий вход - с выходом блока обработки маркера, первый выход - с управляющими входами третьего и четвертого ключевых элементов, второй выход - с вторым входом блока обработки маркера, первый - пятый входы дополнительного канала соединены с одноименными входами основного канала, шестые - тринадцатые входы каналов соединены соответственно основного - с первыми, а дополнительного - с вторыми выходами демультиплексоров, вторые входы основного и дополнительного каналов соединены с входом четвертого ключевого элемента, третьи и пятые входы - соответственно с третьим и четвертым входами, а восьмые основного - с пятым и дополнительного - с шестым входами блока обработки маркера, седьмой вход которого соединен с управляющими входами третьего и четвертого мультиплексоров, объединенными управляющими входами демультиплексоров и третьим входом стартстопного блока управления, в оба канала введены дополнительные вход-выход "Маркер", подключенные от основного канала к восьмому, от дополнительного - к девятому входам-выходам блока обработки маркера, первый выход дополнительного канала соединен с третьим входом третьего мультиплексора, вторые, третьи и четвертые выходы основного и дополнительного каналов соединены соответственно с входами элементов ИЛИ, а пятые - с соответствующими входами четвертого мультиплексора, выход которого подключен к второму управляющему входу третьего мультиплексора, второй выход дополнительного канала подключен также к четвертому входу стартстопного блока управления.

Авторы

Даты

1994-02-28—Публикация

1992-02-28—Подача