Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи данных по цифровым каналам связи.

Цель изобретения - расширение области применения за счет преобразования двоичного кода, повышение быстродействия и упрощение преобразователя.

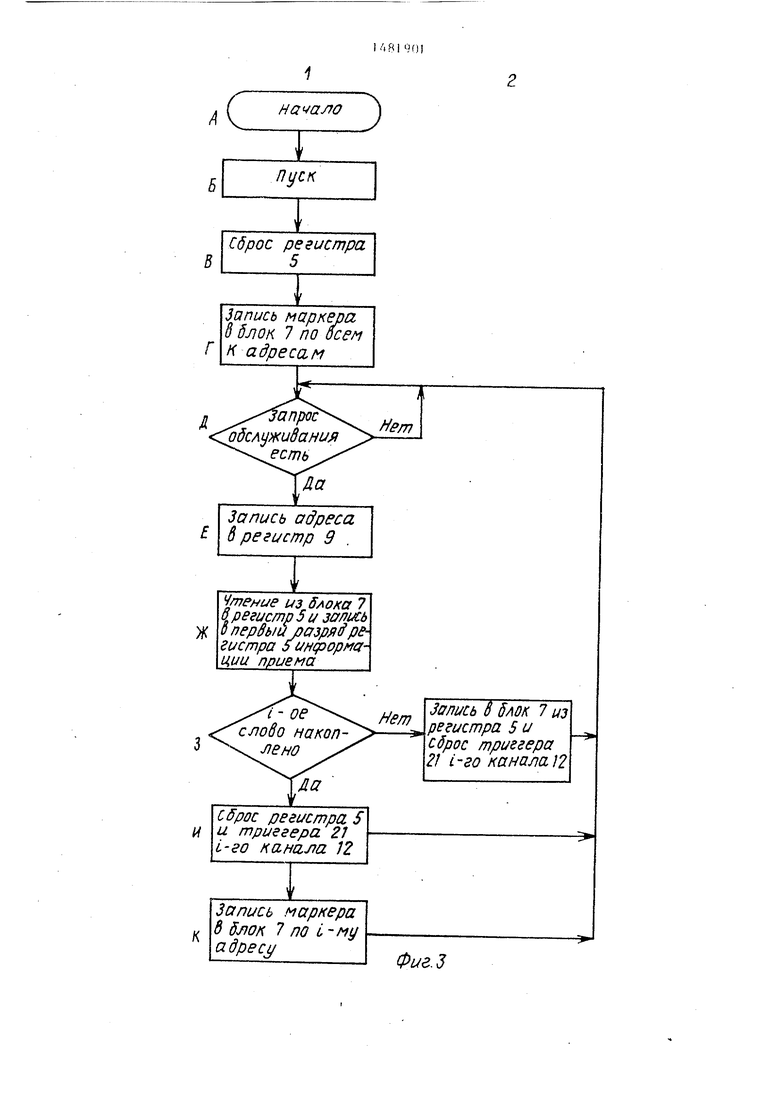

На фиг.1 изображена функциональная схема преобразователя; на фиг.2 - блок управления; на фиг.З - схема алгоритма работы преобразователя; на фиг.4 - временные диаграммы, иллюстрирующие работу преобразователя; на фиг о5 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь последовательного кода в параллельный содержит генератор 1 импульсов, блок 2 управления, блок 3 контроля нечетности, мультиплексор 4, выходной регистр 5, шифратор 6, блок 7 оперативной памяти, дешифратор 8, регистр 9 адреса, эле- мент ИЛИ 10, коммутатор 11 и каналы 12 преобразования, каждый из которых содержит инвертор 13, первый-четвер- тый элементы НЕ 14-17, первый-пятый триггеры 18-22, первый - пятый элементы ИЛИ 23-27, первыи-пятый элементы И 28-32. Первый канал 12.1 содержит, кроме того, источник 33 логической 1м. На фиг.1 обозначены первая 34 и вторая 35 группы информационных входов, первая 36 и вторая

37группы управляющих входов, вход

38запуска, адресные выходы 39, информационные выходы 40, управляющий выход 41 и контрольный выход 42.

Блок 2 управления содержит (фиг„2) первый-пятый триггеры 43-47, счетчик

00

со

314

, Ht plUM ЧЧР МДЧа I МИ ШГМРНТЫ II-llFj

4) , пррвыи-ггдьмои элементы ИЛИ 61 -6/, первый--т рр гии элементы И 68-- 70, пррнып-икч-юй элементы ПК 71-76, парный-четвертый входы 77-80, пер- ВЫН-ЧРТ нрргыи, пятые и шегтой-деся- тыи выходы 81-90.

Преобразователь последовательно- i n кода в параллельный работает следующим образом.

Входной информацией для преобразования может быть как последовательный биполярный код, так и последоватепьный двоичный код. I

В первом случае последовательный бипопярный код поступает на вход 34 канала 12 (фиг.4а), при этом на вход 36 кацапа 12 подается логический О разрешающий работу второго 24 и i третьего 25 элементов ИЛИ, а его ин- яерсное значение (логическая 1) на выходе третьего элемента 16 НЕ проходит через четвертый 26 и пятый 27 лрменты ИЛИ, разрешая работу первого 28 и второго 29 эпементов И. Первый элемент 14 выделяет единичную информацию иэ биполярного сигнала (фиг.4б). Входной сигнал, проинверти рованный в инверторе 13, поступает на второй элемент 15 НЕ, который выделяет пулевую информацию из биполярного сигнала (фиг.4в). Выделенная единичная и нулевая информации поступают на S- и R-входы первого триггера 18 и параллельно - на входы первого элемента ИЛИ 23. На выходе первого триггера 18 формируется последовательный двоичный код (фиг.4г), несущий ту же информацию, что и биполярный код, Полученный последовательный двоичный код поступает через открытые второй элемент ИЛИ 24 и первый элемент И 28 на D-вход второго триггера 19, а первый элемент ИЛИ 23 выделяет синхротакты (фиг.4д), поступающие через открытые третий элемент ИТ.И 25 и второй элемент И 29 на Р- пход третьего триггера 20.

Во втором случае последовательный двоичный код поступает на вход 35 канала 12 (фиг 4г), а синхротакты, сопровождающие информационные разряды, поступают на вход 37 канала 12 (фиг.4д). При этом на вход 36 канала 12 подается логическая 1, проходя- щля через второй 24 и третий 25 эле- МРШЫ ИЛИ, а ее инверсное значение

011

GUM ичгч кии О) на выходе третьего эпемента НП 16 обеспечивает прохождение последовательною двоично о кода с входа 55 на D-вход второго триггера 19 и синхротактов с входа 37 на D-вход третьего триггера 20 канала 12.

Таким образом, перед началом раQ боты каждьй из К каналов 12 настраивается на преобразование последовательного биполярного кода или последовательного двоичного кода.

Далее на С-входы третьего 20,

5 четвертого 21 и пятого 22 триггеров канала 12 с второго выхода блока 2 управления поступают синхроимпульсы (фиг 4е), по которым синхротакты, поступающие на D-вход третьего тригQ гера 20, записывают инфс .ч а ц изо п

третий триггер 20, ас его выхлда переписывают ее в четвертый триггер 21. При этом на его выходе формируются сигналы, задержанные относительно

5 сигналов на выходе третьего триггера 20 на величину периода следования синхроимпульсов. Сигналы с прямого выхода третьего триггера 20 и инверсного выхода -.етвэртого три. i ера 21

0 поступают на третий элемент И 30, на выходе которого формируются короткие импульсы, фиксирующие моменты изменения состояния синхротактов, сопровождающих принимаемые разряды информации, из состояния О в состояние 1 (фиг.4ж). При этом момент перехода совпадает с серединой длительности передачи каждого информационного разряда, поступающего на вход втоQ рого триггера 19.

i

Таким образом, с приходом на Свход второго триггера 19 моментов изменения состояния синхротактов вто- с рой триггер 19 фиксирует каждый очередной разряд информации.

Моменты изменения синхротактов с выхода третьего элемента И 30 поступают также на J-вход пятого триггера 22, на прямом выходе которого форми5

0

5

руются запросы обслуживания принимаемой информации. Логическая с источника 33 в первом канале 12 разрешает прохождение запросов обслуживания принимаемой информации через четвертый элемент И 31. При этом логический О с инверсного выхода пятого триггера 22 поступает на первый вход пятого элемента И 3 и запрета5

ет прохождение море: него логической

ГТ 1 11

Сигнал с выхода пятого элемента И 32 первого канала 12.1 запрещает pa- боту второго канала 12.2, сигнал с выхода пятого элемента И 32 второго канапа 12.2 запрещает работу третьего канала 12.3 и т.д.

При отсутствии входной информации на входах 34 и 35 первого канала 12.1 пятый триггер 22 находится в исходном состоянии, удерживая выход элемента И 31 в нулевом состоянии, а единичное состояние инверсного выход триггера 22 разрешает прохождение логической I с источника 33 первого канала 12,1 на выход пятого элемента И 32, на входы элементов И 31 и 32 второго канала 12.2. Эта логическая 1 является в данном случае сигналом переноса для включения второго канала 12.2. Аналогично происходит включение остальных каналов 12. |

Так организуется параллельно-последовательная схема приоритета, обеспечивающая формирование сигналов запроса обслуживания каналов 12 и сигналов переноса для включения следую- щих каналов 12 на выходах элементов И 31 и 32, причем одновременно сигнал запроса обслуживания может присутствовать на выходе элемента И 3

только одного какого-либо канала 12.

При преобразовании происходит поочередная запись по всем каналам 12 в блок 7 оперативной памяти очередных информационных разрядов с одновременным преобразованием их по мере накопления каждого слова в параллельный код по управляющим сигналам от блока 2 управления и выдача каждого принятого слова по окончании преобразования во внешнее устройство.

Перед началом работы преобразователь настраивается на число п разрядов принимаемого слова по каждому каналу 12. Каждому каналу 12 в блоке 7 оперативной памяти отведена n-раз- рядная ячейка памяти со своим адресом До начала работы блок 2 управления и пятые триггеры 22 каналов 12 преобразования удерживаются в исходном состоянии низким уровнем сигнала (блок А1, фиг.З), поступающего на вход 38 преобразователя. При этом сигналом с девятого выхода 89 блока 2 управления регистр 5 устанавлива-

9016

ется в исходное состояние (блоь Г1, фиг.З).

При поступлении на вход 38 преобразователя сигнала Пуск (логическая 1) блок 2 управления вырабатывает на четвертом выходе 84 сигнал по которому коммутатор 11 подключает k адресному входу блока 7 оперативной памяти пятые выходы 85 блока 2 управления, С восьмого выхода 88 блока 2 управления через элемент ИЛИ 10 на первый информационный вход блока 7 оперативной памяти подается логическая 1, а с восьмого выхода 88 на второй управляющий вход блока 7 поступает сигнал разрешения записи. На пятых выходах 85 блока 2 управления по очереди вырабатываются все адреса n-разрядных ячеек памяти блока 7, а по сигналам с седьмого выхода 87 блока 2 управления, поступающим на первый управляющий вход блока 7, происходит запись в первые разряды n-разрядных ячеек логической 1, а в остальные разряды - логического О (так как остальные информационные входы соединены с одноименными выходами регистра 5, который перед этим установлен в исходное состояние) .

Таким образом, перед началом работы в первый разряд п-разрядной ячейки памяти, отведенной для каждого канала 12, записан маркер приема (блок Г1, фиг.3).

При поступлении хотя бы одного из сигналов запроса обслуживания канала на соответствующий вход шифратора 6, на его первом выходе вырабатывается сигнал включения, поступающий на первый вход 77 блока 2 управления (блок Д1, фиг.З). На вторых выходах шифратора 6 при этом формируется в двоичном коде адрес того канала 12, от которого поступает сигнал запроса. Полученный адрес обслуживаемого канала 12 записывается в регистр 9 адреса с приходом на его вход разрешения записи управляющего сигнала с первого выхода 81 блока 2 управления, выработанного им в ответ на сигнал включения, поступивший от шифратора 6 (блок Е1, фиг.З).

С выхода регистра 9 адрес обслуживаемого канапа поступает на дешифратор 8, через коммутатор 11 на адресные входы блока 7 оперативной памяти и непосредственно на адресные

п ходы мульт шшоксора /4, который ПОД-- КШОЧаег ЧРреч ОДИН ИЗ СВОИХ ВХОДОВ

информационный первый выход обслужила РМОТ-О канапл 12 к первому информационному входу регистра 5. Далее устанавливается режим чтения из блока 7 оперативной памяти сигналом, поступающим на его второй управляющий вхо с i-едьмого выхода 88 блока 2 управ- ления, а сигналом с седьмого выхода 87 блока 2 управления, поступающим на первый управляющий вход блока 7, производится считывание содержимого r.-разрядной ячейки памяти блока 7, адрес которой соответствует двоичному коду номера обслуживаемого канала 1, и одновременная запись в регистр 5 по сигналу, поступающему на его чторой управляющий вход с десятого выхода 90 блока 2 управления (блок (1 , фиг.З). Причем информационные t чзряды ия блока 7 записываются в регистр 5 со сдвигом, т.е. первый разряд записывается во второй разряд ре- гистра 5, второй разряд - в третий разряд регистра 5 и так далее, п-й разряд записывается в (п+1)-й разряд регистра 5, а в первый разряд регистра 5 при этом записывается первый информационный разряд, принятый обслуживаемым каналом 1.

За счет такой переписи из i-й п- разрпдной ячейки блока 7 оперативной памяти в регистр 5 и последующей пря мой записи из регистра 5 в ту же i-ю ячейку блока 7 достигается сдвиг на один разряд информации, хранившейся в i-й ячейке блока 7. Это обеспечивает при приеме очередных информацион- ных разрядов поразрядное накопление информации из канала 12 преобразования .

Таким образом, на данном этапе преобразования в первом разряде ре- гистра 5 записан первый информационный разряд, во втором разряде - маркер приема (ранее он был записан в первьй разряд блока 7, а в остальных разрядах - нули.

Следующий шаг преобразования - прямая запись содержимого регистра 5 ту же ячейку памяти блока 7, из которой перед этим производилось счи тывание (блок 32, фиг.З). При этом управляющие сигналы для записи на первом и втором управляющих входах блока 7 формируются так же, как при

записи маркера. Одновременно с переписью из регистра 5 в блок 7 оперативной памяти с третьего выхода 83 блока 2 управления на первый К-вход пятого триггера 22 обслуживаемого канала 12 поступает сигнал сброса обслуживания канала, а с соответствующего выхода дешифратора 8 через второй К-вход пятого триггера 22 обслуживаемого канала 12 приходит дешифрованный сигнал, соответствующий адресу обслуживаемого какала. При этом триггер 22 с приходом на его С-вход синхроимпульса с второго выхода 82 блока 2 управления устанавливается в исходное состояние. На этом заканчивается обслуживание канала 12 преобразования, которым принят первый разряд информации.

На выходе элемента И 32 оЗсл/жв : ного канала 12 появляется сигнал переноса для включения следующего за ним канала 12. Если в следующем канале еще не принят очередной бит информации, т.е. канал не требует обслуживания, то осуществляется поиск канала 12, требующего обслуживания. Когда такой к „па л 12 найден, ла. выходе его пятого элемента И 32 появляется сигнал запроса обслуживания и весь цикл обработки принятого бита информации повторяется. Аналогично обслуживаются остальные каналы 12.

I

Время обслуживания всех К каналов

12 преобразования выбрано меньше времени периода следования информационных разрядов из каналов 12. Это дает возможность производить преобразование последовательного кода в параллельный в каждом из каналов 12 со скоростью поступления информации на входы 34 или 35,

При поступлении очередного информационного разряда в обслуженный ранее канал 12 процесс обработки повторяется, причем очередной поступивший информационный разряд информи- ровывается к части слова, накопленного ранее ь соответствук.ш,ей п-раз- рядной ячейке блока 7 оперативной памяти.

Таким образом, блок 7 оперативной памяти вместе с регистром 5 выполняет роль регистров сдвига, причем для каждого канала 12 преобразования образуется свой регистр сдвига - регис.тр 5 одни и поч же, а ячейки блока 7 «пора i ИРНОЙ памяти ратные.

Окончание преобразования последовательного кода н n-раэрядный параллельный код в каком-либо канале 12 (блок 31, фиг.З) обнаруживается появлением в (n-Н )-м разряде регистра 5 (на выходе 41) логической 1, т.е. маркера, который является сигналом готовности для приема внешним устройством, например ЭВМ, преобразованного n-разрядного слова с выходов регистра 5 через выходы 40 преобразователя и сопровождающего это слово адреса через выходы 39 преобразователя Информационные разряды преобразованного слова поступают также на блок 3 контроля нечетности, анализирующий правильность принятого кода. Подключение блока 3 контроля нечетности осуществляется поступлением на его управляющий вход логической I с (п+1)-го разряда регистра 5, т.е. по окончании преобразования. Сигнал контроля с выхода блока 3 через выход 42 преобразователя также передается во внешнее устройство. По окончании преобразования по какому-либо из каналов 12 маркер приема, появившийся в (п+1)-м разряде регистра 5, поступает также на ч четвертый вход 80 блока 2 управления который под воздействием этого сигнала сбрасывает регистр 5 и пятый триггер 22 обслуженного канала 12 в исходное состояние (блоки И1, фиг.З) при этом адрес обслуженного канала 12 сохраняется на регистре 9 адреса до появления на его входах сигнала разрешения записи и другого адреса. За это время блок 2 управления производит запись маркета в первый разряд i-й п-разрядной ячейки из блока 7, соответствующей обслуженному каналу 12, подготавливая тем самым эту ячейку к преобразованию следующего слова (блок К1, фиг.З).

Блок 2 управления работает следующим образом.

До начала работы все триггеры 43- 47 находятся в нулевом состоянии. На третий вход 79 блока 2 управления подаются синхроимпульсы от генератора 1 Сфиг.За). При поступлении от внешнего устройства через вход 38 . преобразователя на второй вход 78 блока 2 управления сигнала Пуск (фиг.56) на прямом и инверсном выходах пятого триггера 47 формируются импульсы Гфиг.Зв, г/, поступающие на входы десятого 58 и одиннадцатого 59 элементов И-НЕ, на выходах которых формируются импульсы, сдвинутые относительно друг друга на половину периода (фиг.5д,е), Импульсы с выхода десятого элемента И-НЕ 58 по- ступают на второй выход 82 блока 2 управления и используются для синхронизации работы канапов 12 преобразования, Эти же импульсы обеспечивают синхронизацию работы блока 2 управления. После сигнала Пуск

блок 2 управления и его первый - третий триггеры 43-45 находятся в исходном состоянии до поступления на их С-входы очередного .синхроимпульса. При этом с инверсных выходов первого 43 и второго 44 триггеров сигналы высокого уровня поступают на входы первого элемента И-НЕ 49, на выходе которого формируется сигнал, поступающий через первый элемент НЕ 71 на девятый выход 89 блока 2 (фиГо5ж) и устанавливающий информационные выходы регистра 5 преобразователя в состояние низкого уровня. На остальных выходах блока 2 управляющие сигналы отсутствуют. Логическая 1 с выхода четвертого элемента И-НЕ 52 подается на установочньй вход счетчика 48, удерживая его в исходном положении, и на второй вход двенадцатого элемента И-НЕ 60, разрешая его работу, на третий вход которого подается разрешающий потенциал с выхода первого элемента ИЛИ 61. В исходном положении на выходе переполнения счетчика 48 поддерживается высокий уровень, поступающий на второй вход третьего элемента И 70 и разрешающий его работу. Таким образом, двенадцатый элемент И-НЕ 60 и третий элемент И 70 подготавливаются к прохождению очередного синхроимпульса с выхода десятого элемента И-НЕ 58 на С-входы пер- вого-третьего триггеров 43-45. Одновременно логический О с выхода первого элемента И-НЕ 49 поступает соответственно на первый и второй входы восьмого 56 и девятого 57 элементов И-НЕ и учитывает на их выходах логи- гические 1, которые поступают на D-входы второго 44 и третьего 45 триггеров. На D-входе первого триггера 43 сохраняется логический О.

При поступлении очередного синхроимпульса на С-входы первого-третьего трип-еров 43-45 их прямые выходы устанавливаются в состояния 0,1,1.Низкий уровень с инверсного выхода второго триггера 44 снимает сигнал на девятом выходе 89 блока 2, а высокие уровни с прямых выходов второго 44 и третьего 45 триггеров, поступающие на входы третьего элемента И-НЕ 51, формируют на восьмом выходе 88 блока 2 сигнал маркера (логическую для записи его в блок 7 оперативной памяти (фиг.5э). Высокие уровни с инверсного выхода первого триггера 43 и прямого выхода третьего триггера 45 поступают на входы четвертого элемента И-НЕ 52. При этом на его выходе устанавливается низкий уро- ьень (фиг.5и), который разрешает работу счетчика 48, запрещает прохождение синхроимпульсов через двенадцатый элемент И-НЕ 60 на С-входы пер0

5

0

импульсам (фиг.5л), поступающим г выхода первого элемента И 68 через восьмой выход 88 блока 2 на второй управляющий вход блока 7 оперативной памяти, производится запись в блок 7.

Одновременно с выхода третьего элемента И-НЕ 51 логический О поступает на второй вход седьмого элемента И-НЕ 55 и устанавливает на его выходе логическую 1, которая подается на D-вход первого триггера 43. На D-входы второго 44 и третьего 45 триггеров поступают логические О с соответствующих выходов-восьмого 56 и девятого 57 элементов И-НЕ, так как на их входах присутствуют логические 1, которые приходят с выходов первого 49, пятого 53 элементов И-НЕ и пятого элемента ИЛИ 65, состояние которых определяется состояниями первого-третьего триггеров 43-45. Таким образом, первый - третий триггеры 43-45 подготавливаются к пере

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи данных по цифровым каналам связи позволяет расширить область применения за счет преобразования двоичного кода, повысить быстродействие и упростить преобразователь, содержащий генератор синхроимпульсов, блок управления блок контроля нечетности, мультиплексор, выходной регистр и каналы преобразования. Благодаря введению блока оперативной памяти, шифратора, дешифратора, регистра адреса, элемента ИЛИ и переключателя, а также соответствующему выполнению каналов преобразования в преобразователе обеспечивается процесс непрерывного преобразования как биполярных, так и двоичных кодов. 1 з.п. ф-лы, 5 ил.

вого-третьего триггеров 43-45 на вре- 25 ходу в состояния 1,0,0.

,хя записи маркера во все К ячеек блока 7 оперативной памяти и одновременно поступает через четвертый выход 84 блока 2 на управляющий вход коммутатора 1 1, который по этому сигналу подключает к адресным входам блока 7 оперативной памяти выходы счетчика 48.

Высокий уровень с прямого выхода второго триггера 44 поступает на вход третьего элемента НЕ 73. При этом на его выходе формируется низкий уровень который поступает через седьмой выход 87 блока 2 на первый управляющий вход блока 7 оперативной памяти и подготавливает его к записи (фиг.5к). Этим же сигналом разрешается прохождение синхроимпульсов с выхода одиннадцатого элемента И-НЕ 59 через седьмой элемент ИЛИ 67 на первый вход первого элемента И 68, на второй вход которого подается логическая 1 с выхода шестого элемента ИЛИ 68, разрешающая прохождение синхроимпульсов на выход первого элемента И 68. Логическая 1 на выходе шестого элемента ИЛИ 66 поддерживается высоким уровнем на его втором входе, поступающим с выхода шестого элемента И-НЕ

54, который удерживается в этом соiстоянии низким уровнем, поступающим

на его второй вход с инверсного выхода второго триггера 44. По синхро0

5

0

5

0

3

Синхроимпульсы, поступающие на С-вход счетчика 48 с выхода четвертого элемента НЕ 76, перебирают адреса ячеек памяти в блоке 7 и в первый разряд каждой n-разрядной ячейки памяти записывается маркер. Когда К тактовых импульсов переберут все адреса, на выходе переполнения счетчика 48 появляется отрицательный импульс (фиг.5т), который поступает через открытый третий элемент И 70 на С-входы первого - третьего триггеров 43-45 и переводит их в состояния 1,0,0,

При этом управляющие сигналы на четвертом 84 и шестом-восьмом 86-88 выходах блока 2 снимаются, что приводит к возвращению счетчика 48 в исходное положение, коммутатор 11 преобразователя отключает выходы счетчика 48 и подключает выходы регистра 9 к адресным входам блока 7 оперативной памяти. Состояния 1S0,0 пер- вого-третьег.: триггеров 43-45 вызывают появление на входах пятого элемента И-НЕ 53 логических 1, а на входах первого элемента ИЛИ 61 - логических О. При этом, если на первый вход 77 блока 2, соединенный с первыми входами элементов И-НЕ 53 и ИЛИ 61, поступает логический О с первого выхода шифратора 6 (запрос обслуживания канала 12 отсутствует), то блок 2 управления находитс я н режиме ожидания, ч «эк как логический О, поступавший на третий вход двенадцатого элемента И-(IE 60, запрещает прохождение синхроимпульсов на С-входы первого-третьего триггеров 43-45 и их состояние 1,0,0 сохраняется (фиг.5м).

При появлении на первом входе 77 блока 2 управления запроса обслуживания канала 12 (логическая 1, фиг.5м), на выходе пятого элемента И-НЕ 53 формируется отрицательный импульс (фиг.5н), поступающий через первый выход 81 блока 2 на вход разрешения записи регистра 9 адреса, а логическая 1, сформированная на выходе первого элемента ИПИ 61, разрешает прохождение очередного синхроимпульса на С-входы первого-третьего триггеров 43-45 и переводит в состояния 1,0,1, подготовленные сигналом с выхода пятого элемента И-НЕ 53,

При этом с выхода третьего элемента НЕ 73 через седьмой выход 87 блока 2 на первый управляющий вход блока 7 оперативной памяти подается логическая 1 (фиг.Зк), подготавливая его к считыванию, а на выходе шестого элемента И-НЕ 54 формируется логический О, разрешающий прохождение импульса с прямого выхода пятого триггера 47 через шестой элемент ИЛИ 66 на вход первого элемента И 68, на другом входе которого присутствует сигнал разрешения (логическая 1), поступающий с выхода седьмого элемента ИЛИ 67, так как на его вход подается логическая 1 с выхода третьего элемента НЕ 73, Отрицательный импульс с выхода первого элемента И 68 через восьмой выход 88 блока 2 поступает на второй управляющий вход блока 7 оперативной памяти (фиг.5л), по которому производится чтение п-раз- рядной ячейки по i-му адресу. Одновременно на десятом выходе 90 формируется положительный импульс (фиг.5о) передний фронт которого совпадает с серединой длительности импульса чтения (фиг.5л).

Таким образом, импульс, поступающий с десятого выхода 90 блока 2 на второй управляющий вход регистра 5, производит запись в регистр 5 числа, считанного с блока 7 оперативной памяти.

0

5

0

5

0

5

0

5

0

5

Дальнейшая работа блока 2 управления зависит о г того, накоплено в регистре S п-разрядное слово или нет.

Если преобразование не закончено, то с выхода (п+1)-ю разряда регистра 5 логический О поступает через четвертый вход 80 блока 2 на D-вход четвертого триггера 46, состояние которого не изменяется с приходом на его С-вход синхроимпульса. Поэтому низкий уровень на прямом выходе четвертого триггера 46, поступающий на первый вход пятого элемента ИЛИ 65, на второй вход которого приходит также низкий уровень с выхода шестого элемента И-НЕ 54, вызывает появление на выходе пятого элемента ИЛИ 65 логического О, который- устанавливает с помощью восьмого элемента И-НЕ 56 на D-входе второго триггера 44 логическую 1, На D-входах первого 43 и третьего 45 триггеров при этом появляются логические О. I

Таким образом, с приходом очередного синхроимпульса на С-входы первого-третьего триггеров 43-45 они переходят из состояний 1,0,1 в состояния 0,1,0. При этом на седьмом 87 и восьмом 88 выходах блока 2 управления формируются сигналы (фнг.5к,л), по которым содержимое регистра 5 записывается в i-ю ячейку блока 7 оперативной памяти, соответствующую обслуживаемому каналу 12, а на третьем выходе 83 блока 2 управления формируется сигнал сброса в исходное по- ложение пятого триггера 22 обслуженного канала 12 (фиг.5п).

I

С приходом на С-входы первого- третьего триггеров 43-45 очередного синхроимпульса они снова переходят в состояния 1,0,0 и далее блок 2 управления вырабатывает все необходимые управляющие сигналы по обслуживанию следующего канала 12.

Если преобразование по какому-либо каналу 12 закончено, т.е. в регистре 5 накоплено n-разрядное слово, то первый-третий триггеры 43-45 блока 2 управления переходят из состояний 1,0,1 в состояния 0,0,0,

При этом в отличие от первоначального состояния, кроме сигнала сброса в исходное положение регистра 5, одновременно на третьем выходе 83 блока 2 управления формируется сигнал

сброса пятого триггера 22 обслуживаемого канала 12 (фиг.5ж,п). Это достигается тем, что маркер приема, появившийся в (п+1)-м разряде регистра 5, записывается в четвертый триггер 46 блока 2 управления и логическая 1 с его прямого выхода (фиг.Зр) поступает на второй вход второго, элемента ИЛИ 62 и формирует на его выходе логическую 1, поступающую на второй вход второго элемента И-НЕ 50 на первый вход которого приходит также логическая 1 с инверсного выхода третьего триггера 45. При этом с выхода второго элемента И-НЕ 50 на третий выход 83 блока 2 управления поступает сигнал для сброса пятого триггера 22 обслуживаемого канала 12 (фиг.Зи).

Одновременно первый-третий триггеры 43-45 подготавливаются к переходу в следующее состояние. Сигналы низкого уровня с инверсного выхода четвертого триггера 46 и выхода третьего элемента И-НЕ 50 поступают на входы четвертого элемента ИЛИ 64, и логический О, сформированный на его выходе, устанавливает седьмой элемент И-НЕ 55 в состояние логической 1, которая подается на D-вход первого триггера 43. С выхода первого элемента И-НЕ 49 сигнал низкого уровня поступает на входы восьмого 56, девятого 57 элементов И-НЕ и устанавливает на их выходах логические 1, которые подаются на D-входы второго 44 и третьего 45 триггеров,

Таким образом, с приходом очередного синхроимпульса на С-входы первого-третьего триггеров 43-45 они - переходят в состояния 1,1,1.

При этом на шестом выходе 86 блока 2 управления формируется маркер (фиг,5з), который по сигналам, сформированным на седьмом 87 и восьмом 88 выходах блока 2 управления(фиг.5к л), записывается в первый разряд i- n-раэрядной ячейки блока 7 (адрес обслуженного канала 12 сохраняется на регистре 9 адреса до перехода блока 2 управления в состояние 1,0,0).

Положительным перепадом сигнала с выхода первого элемента И 68 в четвертый триггер 46 записывается логический О (фиг.5 л,р), так как регистр 5 обнулен и на D-вход четвертого триггера 46 поступает с (п+1)- го разряда регистра 5 логический О

10

5

0

5

0

35

40

45

50

5

Очередной синхроимпульс, поступающий с выхода десятого - лемента И-НЕ 58, переводит первый-третий триггера 43-45 в состояния 1,0,0 и далее вся работа блока 2 управления повторяется .

Таким образом, за время, равное периоду между двумя информационными разрядами входного кода, происходит прием и обработка одного разряда информации во всех К каналах преобразования, причем прием каждого п-раз- рядного информационного слова происходит с одновременным его преобразованием и в отличие от известного преобразователя не требуется проме-. жуточного хранения накопленных слов. Поэтому преобразование может быть непрерывным без предварительного «акоп- ления N слов.

Предлагаемый преобразователь позволяет производить преобразование любых входных кодов, как биполярных, так и двоичных, как с паузами, так и Лез пауз, что расширяет область его применения.

Кроме того, предлагаемый преобразователь позволяет одновреме производить в одних каналах 12 преобразование биполярных входных кодов, а в других каналах 12 преобразование двоичных входных кодов, причем скорость поступления входной информации для разных каналов 12 может быть различной, что также расширяет область его применения.

Формула изобретения

1, Преобразователь последовательного кода в параллельный, содержащий генератор импульсов, блок управления, блок контроля нечетности, мультиплексор,выходной регистр и К каналов преобразования, каждый из которых включает в себя первый-пятый триггеры, первый-четвертый элементы И, первый-пягый элементы ИЛИ, первый и второй элементы НЕ я инвертор, вход которого объединен с входом первого элемента НЕ и является первым информационным входом канала преобразования, выход первого элемента НЕ соединен с S-входом первого триггера и первым входом первого элемента ИЛИ, выход инвертора через второй элемент НЕ подключен к R-входу первого триггера и второму входу первоI ;

го (ммп И;ГИ, о т л и ч л ю ш и г я тем, чти , г цепью расширения оласти применения за с«от преобразования ДРОИЧНОГО кода, повышения быстродействия и упрощения преобразователя, в него введены шифратор,бло оперативной памяти, дешифратор, регистр адреса, элемент ИЛИ,коммутатор, а в каждый канал преобразования - пятый элемент И и третий и чевертый элементы НЕ, вход третьего элемента НЕ объединен с первыми входами второго и третьего элементов ИЛИ и является первым управляющим входом канала преобразования, выход третьего элемента НЕ соединен с первыми входами четвертого и пятого элементов ИЛИ, вторые входы которых являются вторыми соответственно управляющим и информационным входами канала преобразования, прямой выход первого триггера соединен с вторым входом второго элемента ИЛИ, выход которого и выход пятого элемента ИЛ подключены к первому и второму входам первого элемента И, выход которго соединен с D-входом второго триггера, выход первого элемента ИЛИ соединен с вторым входом третьего элемента ИЛИ, выход которого и выхо четвертого элемента ЕЛИ подключены первому и второму входам второго элмента И, выход которого соединен с D-входом третьего триггера, прямой выход которого подключен к D-входу четвертого триггера и первому входу третьего элемента И, инверсный выход четвертого триггера соединен с вторым входом третьего элемента И, выход которого через четвертьй элемент НЕ и непосредственно подключен соответственно к С-входу второго и J-входу пятого триггеров, прямой и инверсный выходы пятого триггера соединены с первыми входами соответственно четвертого и пятого элементов И, вторые входы которых в первом канале преобразования подключены к выходу источника логической единицы, выход пятого элемента И каждого канала преобразования, кроме последнего, соединен с вторыми входами четвертого и пятого элементов И последующего канала nppoff разования, прямой выход второго триггера каждого канала преобразования соединен с соответствующим информационным входом мультиплексора, выход четвертого эле

8

мента И каждсно к .и к- га ript-обрлчсша- ния подключен к соответствующему входу шифратора, первый выход Koiopoio соединен с мерным входом блока управления, перлый выход которого и вторые выходы шифратора подключены соответственно к рходу разрешения записи и информационным входам регист- JQ ра адреса, выходы которого соединены с входами дешифратора, первыми информационными входами коммутатора, адресными входами мультиплексора и являются адресными выходами преобра- 5 зователя, второй и третий выходы блока управления подключены соответственно к С-входам третьего-пятого триггеров всех каналов преобразования и первому К-входу .пятого трнг- 0 гера всех каналов преобразования, вч- ходы дешифратора подключены к вторым Квходам пятых триггеров соответствующих каналов преобразования, второй вход блока управления объединен с 5 Rвходами пятых триггеров всех каналов преобразования и является входом запуска преобразователя, выход генератора соединен с третьим входом блока управления, четвертый, пятый и 0 шестой выходы которого подключены соответственно к управляющему и вторым информационным входам коммутатора и первому входу элемента ИЛИ, выходы которых соединены соответственно а с адресными и первым информационным J входами блока оперативной памяти, выход мультиплексора подключен к первому информационному входу выходною регистра, выход первого разряда ко- 0 торого подключен к первому информационному входу блока контроля нечетности, второму входу элемента ИЛИ и является первым информационным выходом преобразователя, выходы второго 5 n-го разрядов выходного регистра (п. - разрядность слов входного кода) соединены с одноименными информационными входами блока контроля нечетности и блока оперативной памяти и яв- Q ляются одноименными информационными выходами преобразователя, выход (п+ +1)-го разряда выходного регистра подключен к управляющему входу блока контроля нечетности, четвертому вхо- 5 ДУ блока управления и является управляющим выходом преобразователя, седьмой-десятый выходы блока управления соединены соответственно с первым и вторым управляющими входами

блока оперативной памяти и выходного регистра, выходы первого - пто разрядов блока оперативной памяти подключены соответственно к второму - (п+1)-му информационным входам выходного регистра, выход блока контроля нечетности является контрольным выходом преобразователя.

2„ Преобразователь по п.1, о т- личающийся тем, что блок управления содержит первый-пятый триггеры, счетчик , первый-двенадца- . тый элементы И-НЕ, первый-седьмой элементы ИЛИ, первый-третий элементы И и первый-шестой элементы НЕ, первые входы первого элемента ИЛИ и пятого элемента И-НЕ объединены и являются первым входом блока, R-вхо- ды всех триггеров объединены с первым входом одиннадцатого элемента И-НЕ и являются вторым входом блока, С-вход пятого триггера объединен с первым входом десятого и вторым в хо- дом одиннадцатого элементов И-НЕ и является третьим входом блока, D- вход четвертого триггеря является четвертым входом блока, прямой выход пятого триггера подключен к второму входу десятого элемента И-НЕ и первому входу шестого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, инверсный выход пятого триггера подключен к третьему входу одиннадцатого элемента И-НЕ, выход которого соединен через четвертый элемент НЕ и непосредственно с первыми входами соответственно второго элемента И и седьмого элемента ИЛИ, выход которого подключен к второму входу первого элемента И, прямой выход четвертого триггера соединен с первыми входами второго и пятого элементов ИЛИ, выходы которых подключены к первым входам соответственно второго и восьмого элементов И--НЕ, инверсный выход четвертого триггера соединен с первым входом четвертого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И-НЕ, выход которого соединен с D-входом первого гера, прямой выход которого подключен к второму входу пятого элемента И-НЕ, выход которого соединен с вторым входом седьмого и первым входом девятого -шементов И-НЕ и является, первым выводом блока, выход десятого

элемента И-НЬ соединен с входом шестого элемента НЕ и является вторым выходом блока, выход шестого элемента НЕ подключен к первому входу двенадцатого элемента И-НЕ и счетному входу счетчика, выход переполнения которого соединен с первым входом третьего элемента И, инверсный выход

первого триггера подключен к первому входу первого и четвертого элементов И-НЕ и второму входу первого элемента ИЛИ, выход которого соединен с вторым входом двенадцатого элемента

5 И-НЕ, выход которого подключен к второму входу третьего элемента И, выход которого соединен с С-входами первого-третьего триггеров, выход первого элемента И-НЕ подключен к

0 входу первого элемента НЕ и вторым входам восьмого и девятого элементов И-НЕ, выходы которых соединены с D-входами соответственно второго и третьего триггеров, прямой выход

5 второго триггера подключен к третьему входу первого элемента ИЛИ, входу третьего элемента НЕ, первому входу третьего элемента И-НЕ и второму входу второго элемента ИЛИ, выход вто0 Рого элемента И-НЕ подключен к пер- вому входу третьего и второму входу четвертого элементов ИЛИ и является третьим выходом блока, выход третьего элемента И-НЕ соединен с входом второго элемента НЕ и третьим входом седьмого элемента И-НЕ, инверсный выход второго триггера подключен к третьему входу пятого, второму входу первого и первому входу шестого элеп ментов И-НЕ, прямой выход третьего триггера соединен с вторыми входами третьего, четвертого и шестого элементов И-НЕ и четвертым входом первого элемента ИЛИ, выход четвертого

5 элемента И-НЕ подключен к третьему входу двенадцатого элемента И-НЕ и входу обнуления счетчика и является четвертым выходом блока, выходы разрядов счетчикз являются пятыми выхоп дами блока, выход второго элемента НЕ является шестым выходом блока, выход третьего элемента НЕ подключен к вторым входам третьего и седьмого элементов ИЛИ и является седьмшм выг- ходом блока, выход первого элемента И соединен с С-входом четвертого триггера и является восьмым выходом блока, выход первого элемента НЕ является девятым выходом блока, инвер5

сны и РЫХОД трртьгю грип рра под-того -элементов ilJIH и входом пятого

ключеи к второму входу второго и чет- элемента НЕ, выход которого подклю- вертому входу пятого плементон И-НЕ,чсн к второму входу второго элемента

выход шестого элемента И-НЕ сосци- нен с вторыми нходами пятого и шес И, выход которого является десятым выходом блока.

.М.1

J7./ 6.1

Фиг.1

И, выход которого является десятым выходом блока.

№

7/

Л 72

№AwllfJl2 J3jjH Is йОЙЙсЬЙЙ

$Н

7

rfl

С

начало

В

Сброс регистра

Г

Запись маркера 8 длок 7 по осем к адресам

Чтение из блока 7 в регистр 5 и зямсь о первыйо а зря о регистра 5 информации приема

и

сброс регистра 5 и триггера 27 L-го канала 12

К

Запись маркера в блок 7 по I -му адресу

)

Записьо блок 7 из регистра 5 и сдрос триггера 21 i-го канала 12

.З

а

i

01

г

д е

ж

JTVHrf7Lrriiijm-urwsri v rm

-ц-

.J

LJ

LJ

ЪГЪГ

LT

LJTJLJ

0

I-TJ

0

JU

.

II

I I I

Фиг. k

gUlJlJlJTJX JTrLrTJTjnLJ

tf

.-Л-ГЛ.-.

Ж

и

л м н

т

{ „„.„,---1,---,--, . I - -,-- II

,.

0jЗг$з ffs °з fft, of &g G3

Фие.5

Составитель О.Ревинский

Редактор М.Бланар Техред М.Дидык Корректор с.Шекмар

Заказ 2702/57 Тираж 885Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производгтвенно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

LJ

LJ

LJTJLJ

0

I-TJ

0

.

о

I I I

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-08-27—Подача