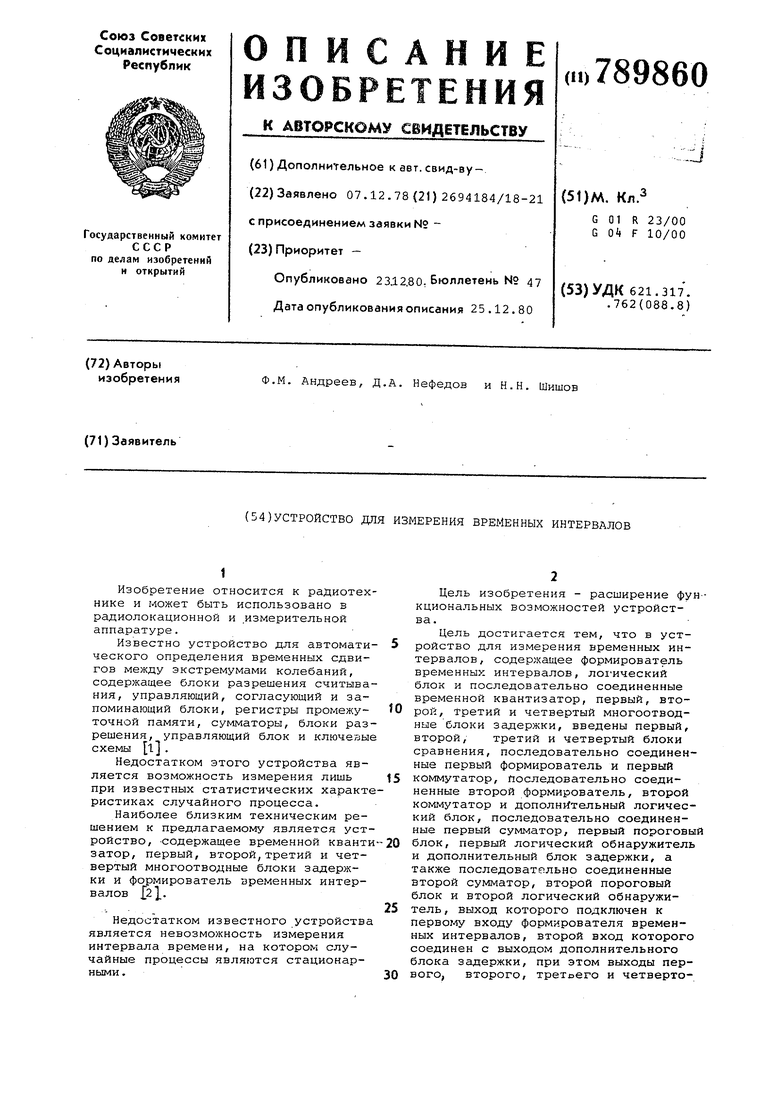

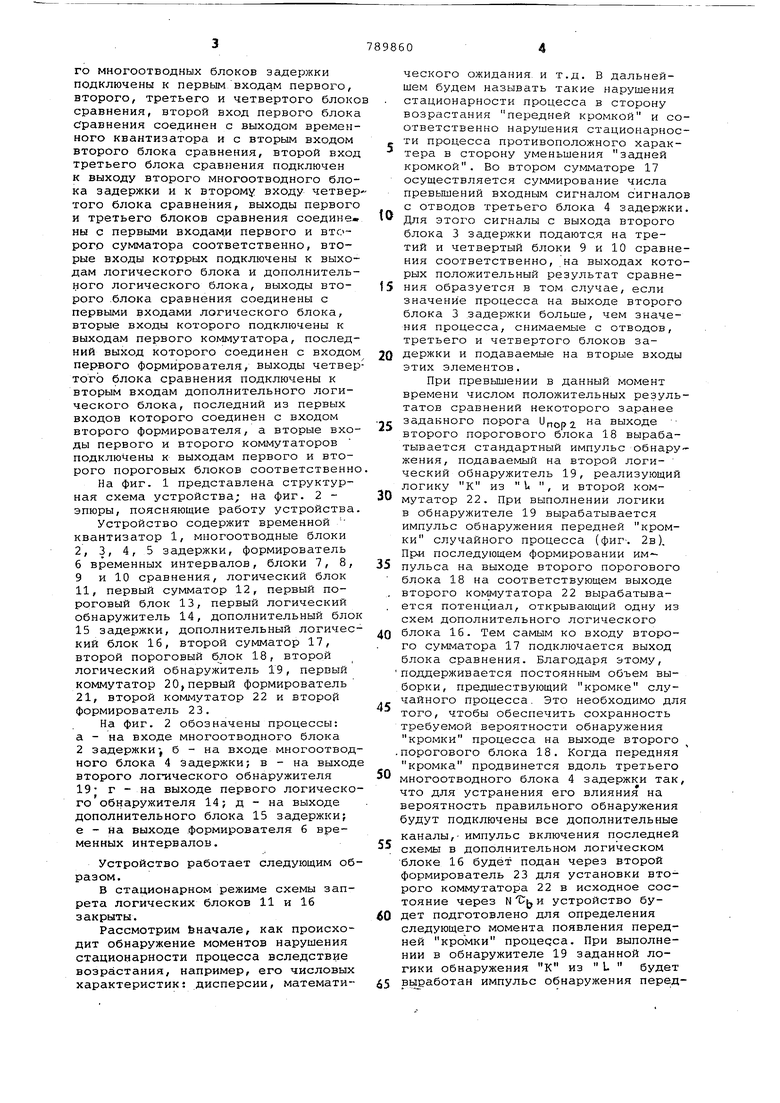

Изобретение относится к радиотех нике и может быть использовано в радиолокационной и измерительной аппаратуре. Известно устройство для автомати ческого определения временных сдвигов между экстремумами колебаний, содержащее блоки разрешения считыва ния, управляющий, согласующий и запоминающий блоки, регистры промежуточной памяти, сумматоры, блоки раз решения, управляющий блок и ключевы схемы l . Недостатком этого устройства является возможность измерения лишь при известных статистических характ ристиках случайного процесса. Наиболее близким техническим решением к предлагаемому является уст ройство, -содержащее временной квант затор, первый, второй,третий и четвертый многоотводные блоки задержки и формирователь временных интерваловНедостатком известного устройств является невозможность измерения интервала времени, на котором случайные процессы являются стационарными. Цель изобретения - расширение фун-кциональных возможностей устройства. Цель достигается тем, что в устройство для измерения временных интервалов, содержащее формирователь временных интервалов, ло1ический блок и последовательно соединенные временной квантизатор, первый, второй, третий и четвертый многоотводные блоки задержки, введены первый, второй, третий и четвертый блоки сравнения, последовательно соединенные первый формирователь и первый коммутатор. Последовательно соединенные второй формирователь, второй коммутатор и дополнительный логический блок, последовательно соединенные первый сумматор, первый пороговый блок, первый логический обнаружитель и дополнительный блок задержки, а также последовательно соединенные второй сумматор, второй пороговый блок и второй логический обнаружитель, выход которого подключен к первому входу формирователя временных интервалов, второй вход которого соединен с выходом дополнительного блока задержки, при этом выходы первого, второго, третьего и четвертого многоотводных блоков задержки подключены к первым входам первого, второго, третьего и четвертого блоко сравнения, второй вход первого блок сравнения соединен с выходом времен ного квантизатора и с вторьлу входом второго блока сравнения, второй вход третьего блока сравнения подключен к выходу второго многоотводного блока задержки и к второму входу четвер того блока сравнения, выходы первого и третьего блоков сравнения соедине ны с первыми входами первого и второго сумматора соответственно, вторые входы котррых подключены к выходам логического блока и дополнительного логического блока, выходы второго .блока сравнения соединены с первыми входами логического блока, вторые входы которого подключены к выходам первого коммутатора, послед ний выход которого соединен с входом первого формирователя, выходы четвер того блока сравнения подключены к вторым входам дополнительного логического блока, последний из первых входов которого соединен с входом второго формирователя, а вторые вхо ды первого и второго коммутаторов подключены к выходам первого и второго пороговых блоков соответственн На фиг. 1 представлена структурная схема устройства; на фиг. 2 эпюры, поясняющие работу устройства Устройство содержит временной квантизатор 1, многоотводные блоки 2, 3, 4, 5 задержки, формирователь б временных интервалов, блоки 7, 8, 9 и 10 сравнения, логический блок 11, первый сумматор 12, первый пороговый блок 13, первый логический обнаружитель 14, дополнительный бло 15 задержки, дополнительный логичес кий блок 16, второй сумматор 17, второй пороговый блок 18, второй логический обнаружитель 19, первый коммутатор 20,первый формирователь 21, второй коммутатор 22 и второй формирователь 23. На фиг. 2 обозначены процессы: а - на входе многоотводного блока 2 задержки-, б - на входе многоотвод ного блока 4 задержки; в - на выход второго логического обнаружителя 19- г-на выходе первого логическо го обнаружителя 14; д - на выходе дополнительного блока 15 задержки; е - На выходе формирователя б временных интервалов. Устройство работает следующим об разом. В стационарном режиме схемы запрета логических блоков 11 и 16 закрыты. Рассмотрим бначале, как происходит обнаружение моментов нарушения стационарности процесса вследствие возрастания, например, его числовых характеристик: дисперсии, математического ожидания, и т.д. В дальнейшем будем называть такие нарушения стационарности процесса в сторону возрастания передней кромкой и соответственно нарушения стационарности процесса противоположного характера в сторону уменьшения задней кромкой. Во втором cyj/iMaTope 17 осуществляется суммирование числа превышений входным сигналом сигналов с отводов третьего блока 4 задержки. Для этого сигналы с выхода второго блока 3 задержки подаются на третий и четвертый блоки 9 и 10 сравнения соответственно, на выходах которых положительный результат сравнения образуется в том случае, если значение процесса на выходе второго блока 3 задержки больше, чем значения процесса, снимаемые с отводов, третьего и четвертого блоков задержки и подаваемые на вторые входы этих элементов. При превышении в данный момент времени числом положительных результатов сравнений некоторого заранее заданного порога порх выходе второго порогового блока 18 вырабатывается стандартный импульс обнаружения, подаваемый на второй логический обнаружитель 19, реализующий логику К из U , и второй коммутатор 22. При выполнении логики в обнаружителе 19 вырабатывается импульс обнаружения передней кромки случайного процесса (фиг-. 2в). Пр« последующем формировании импульса на выходе второго порогового блока 18 на соответствующем выходе второго коммутатора 22 вырабатывается потенциал, открывающий одну из схем дополнительного логического блока 16. Тем самым ко входу второго сумматора 17 подключается выход блока сравнения. Благодаря этому, поддерживается постоянным объем выборки, предшествующий кромке случайного процесса. Это необходимо для того, чтобы обеспечить сохранность требуемой вероятности обнаружения кромки процесса на выходе второго порогового блока 18. Когда передняя кромка продвинется вдоль третьего многоотводного блока 4 задержки так, что для устранения его влияния на вероятность правильного обнаружения будут подключены все дополнительные каналы,- импульс включения последней схемы в дополнительном логическом блоке 16 будет подан через второй формирователь 23 для установки второго коммутатора 22 в исходное состояние через и устройство будет подготовлено для определения следующего момента появления передней кромки процедса. При выполнении в обнаружителе 19 заданной логики обнаружения К из выработан импульс обнаружения передней кромки процесса (фиг. 2в), задержанный относительно передней кромки процесса на величину At-tjjU Он подается для запуска формирователя б временных интервалов. При этом в течение всего времени обнаружения передней кромки процесса, схемы логического блока 11 будут закрыты, так как в этом случае сигнал на выходе временного квантизатора 1 не меньше сигналов с отводов первого многоотводного блока 2 задержки, подключенных к первому блоку 7 сравнения. Поэтому уровень порога и,др. превьошен не будет.

С появлением задней кромки процесса на входе первого многоотводного блока 2 задержки в результате работы блока 7 сравнения будут выработаны сигналы положительных результатов сравнения, сумма которых начнет превышать уровень порога первого порогового блока 13 выходе последнего будет сформирован стандартный импульс. При этом на выходах блоков 7 и 8 сравнения положительный результат сравнения вырабатывается в том случае, если значение процесса на выходе квантизатора 1 меньше, чем значения процесса, снимаемые с отводов первого и второго блоков 2 и 3 задержки соответственно и подаваемые на вторые входы этих элементов. Импульсы превышения U f,op поступают на входы первого коммутатора 20 и первого обнаружителя 14 К из L. Коммутатор при этом вырабатывает, сигнал , отпирающий одну из схем логического блока 11, благодаря чему обеспечивается сохранение объема выборки входного процесса со старой дисперсией или прежним законом распределений. Вследствие этого логика работы порогового узла остается неизменной. При выполнении в первом обнаружителе 14 заданной логики обнаружения вырабатывается импульс обнаружения задней кромки процесса (фиг. 2г), который через дополнительный блок 15 задержки (фиг. 2 д) подается на второй вход формирователя 6 временных интервашов. В результате этого с выхода формирователя б будет сниматься импульс (фиг. 2е), содержащий информацию о временном положении передних и задних кромок процесса и длительности интервала стационарности.

В качестве .формирователя 6 временных интервалов может быть использован, например, обыкновенный триггер.

Проанализируем показатели качества обнаружения моментов нарушения. стационарности процесса применительно к предлагаемому устройству. Для обнаружения передней и задней кромок процесса в этом устройстве используются два непараметрических обнаружителя, первый из которых содержит блоки 2, 3, 7, 8, 11, 13, сумматор 12,а второй - 4,5,9, 10, 16,18 и второй сумматор 17. Алгоритм обнару, женин 1 этапа на выходе порогового устройства, при обнаружении передней кромки процесса может быть представлен в виде

;, v(o-u.

o ,о а на выходе первого порогового блока 13 при обнаружении задней кромки процесса S4-(n(U.-u)4i

5 Л 2iw.

где пороговое число пз п, - число отводов линии задержки непара- метрического обнаружителя, и - выборочное значение процесса на входе

20 непараметрического обнаружителя.

Как правило (3), выбирают m-in. В этом случае вероятности ложной тревоги и правильного обнаружения случайного процесса с новой интенсивностью определяются соответственно выражениями

Рр-- (x)d% nfw (vldv.

(1)

01 1-1 о 1

P.--Jw Iw.. (j)dv

C2) о .i i-1 о i t

Рассмотрим случай, когда огибающая помехового фона до момента изменения интенсивности скачка имеет распределение Релея

,(

е2

(г)

а после скачка интенсивности - то же распределение, но с измененной дисперсией

n,((), (4)

где S - степень различия дисперсий помехи до и после скачка. Тогда вероятности ложной тревоги Рр и Правильного обнаружения Рд момента скачка на 1 этапе,т.е. на выходах пороговых, блоков 13 и 18 определяются из (1) и (2) с учетом (3) и (4) в виде

4

(5)

Р.. Hv

Г(П.1К(.0

л; г(.. ..)

(6)

где rU)- гамма-Функция.

60

Так как. при выдаче сигнала обнаружения на выходе порогового блока 18 с помощью дополнительного логического блока 16 проводится подключение ко второму сумматору 17 вы- .

ходов блока 10 сравнения,то вероятность правильного обнаружения в следующий момент времени новой интенсивности помехи следует определять с уча том вероятности правильного обнаружения этого процесса в предыдущий момент времени. Среднее значение этой вероятности равно

IW.. (K-)d)(.FiT

.„(,)а,|(,-рд,1

2Lo

LK

П

n+1

ПТ1 p

,.

WAi.

W)dy P..

2 1 .

Вследствие того, что выборочные значения помехи не коррелированы и имеют одинаковые распределения,/ выражение (7) становится адекватным выражению (6).

Решение об обнаружении кромки процесса принимается в том случае, когда в L последовательных выборках будет иметь место К обнаружений Для этих целей используется обнаружитель 19 типа К из L, Вероятность правильного обнаружения кромки процесса Рд на выходе такого обнаружителя

Рд -- 2 с 1 А-р. t (g)

i-.K NV . , .

JiL

c;.-

где К - порог I I

этапа.

1 И U -1) С учетом (6).

. ui )(4-i)T .-KV,

.,

При этом вероятность ложного обнаружения (тревоги) на выходе обнаружителей 14 или 19 равны

р Л

(10

WW4

Полученные выражения могут быть также использованы для определения вероятности правильного обнаружения задней кромки процесса. Задаваясь числом п, требуемым значением 1л , можно определить по формуле (10) логику обнаружения, т.е. число К, удовлетворяющую задаваемой величине вероятности .ложной тревоги Рр, на выходе обнаружителя 19. Для L 8, значений п 10 и п 30, вероятностей ложной тревоги Рр, 10 и 10 приведены кривые вероятности правильного обнаружения момента нарушения стационарности случайного процесса устройством (фиг. 1) и для сравнения кривые обнаружения пр использовании идеального обнаружителя (сплошные линии), в рассматриваемом случае, когда случайный процесс имеет pacrfpeдeлeниe вида (з), таким идеальным обнаружителем является идеальный некогерентный накопитель. Из графиков следует, что уменьшение требуемого значения вероятности ложной тревоги на выходе обнаружителя 19 также как и уменьшение числа отводов приводит к возрастанию потерь по сравнению со случаем идеального накопления.. Приведенные графики позволяют произвести выбор требуемого числа отводов линий задержки, а также необходимой логики обнаружения.

Таким образом, применение данного устройства в отличие от прототипа позволяет измерять интервал стационарности помехового колебания, что расширяет его функциональные возможности.

Формула изобретения Устройство для измерения временных интервалов, содержащее формирователь временных интервалов, логи- ческий блок и последовательно соединенные временной квантизатор, первый, второй, третий и четвертый многоотводные блоки задержки, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены первый, второй, третий и четвертый блоки сравнения, последовательно соединенные первый формирователь и первый коммутатор,.последовательно соединенные второй формирователь, второй коммутатор и дополнительный логический блок,последовательно соединенные первый сумматор,первый пороговый блок,первый логический обнаружитель и дополнительный блок задержки,а также последовательно соединенные второ сумматор, второй пороговый блок и втрой логический обнаружитель,выход которого подключен к первому входу формрователя временных интервалов,второй вход которого соединен с выходом

дополнительного блока задержки, при этом выходы первого, второго, третьего и четвертого многоотводных блоков задержки подключены к первым входам первого, второго, третьего и четвертого блоков сравнения, второй вход первого блока сравнения соединен с выходом временного квантизатора и с вторым входом второго блока сравнения, второй вход третьего блока сравнения подключен к выходу второго многоотводного блока задержки и к второму входу четвертого блока сравнения, выходы первого и третьего блоков сравнения соединены с первыми входами первого и второго сумматора соответственно, вторые входы которых подключены к выходам логического блока и дополнительного ,логического блока, выходы второго .блока сравнения соединены с первыми входами логического блока, вторые входы которого подключены к выходам первого комму-татора, последний выход которого соединен с входом первого формирователя, выходы четвертого блока сравнения подклю.чены к вторым входам дополнительного логического блока, последний из riegBbix входов которого соединен с-входом второго формирователя, а вторые входы первого и второго ком мутаторов подключены к выходам первого и второго пороговых блоков соответственно. Источники информации, инятые во внимание при экспертизе 1.Авторское свидетельство СССР 506818, кл. G 01 V 1/30, 1976. 2.Заявка Великобритании 1411058, кл. G 01 R 23/02 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| ОБНАРУЖИТЕЛЬ ФАЗОКОДИРОВАННЫХ СИГНАЛОВ | 1990 |

|

SU1818985A1 |

| Комплексное устройство обнаружения в многопозиционной радиолокационной станции | 2021 |

|

RU2778247C1 |

| ОБНАРУЖИТЕЛЬ РАДИОИМПУЛЬСОВ | 1979 |

|

SU1840949A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Комплексное устройство обнаружения воздушных объектов | 2024 |

|

RU2835495C1 |

| ЦИФРОВОЙ АДАПТИВНЫЙ ОБНАРУЖИТЕЛЬ | 1993 |

|

RU2048681C1 |

| Комплексное устройство обнаружения воздушных объектов | 2023 |

|

RU2816190C1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ ПОМЕХОУСТОЙЧИВОСТИ ПРИЕМНИКА ВИДЕОСИГНАЛОВ | 1993 |

|

RU2048680C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ УРОВНЯ ЛОЖНЫХ ТРЕВОГ ПОМЕХОЗАЩИЩЕННОГО РАДИОЛОКАЦИОННОГО ПРИЕМНИКА, РАСПОЛОЖЕННОГО НА ВОЗДУШНЫХ НОСИТЕЛЯХ | 1990 |

|

SU1840162A1 |

i

Авторы

Даты

1980-12-23—Публикация

1978-12-07—Подача